内容总览

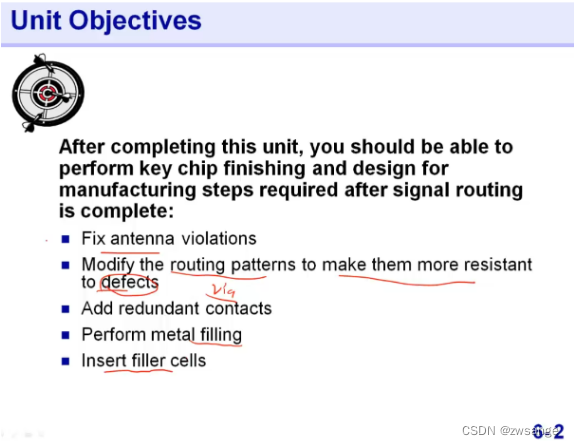

Chip finish即为DFM;

①在DFM阶段,我们需要fix所有的antenna violation,在route阶段也做了天线效应的修复,但是只fix了一次,可能还有未修复的,这一节全部fix完成;

②修正routing的pattern以使得布线更加强壮以抵抗defect缺陷;

③增加一些冗余的连接;

④执行金属填充并插入filler cell;

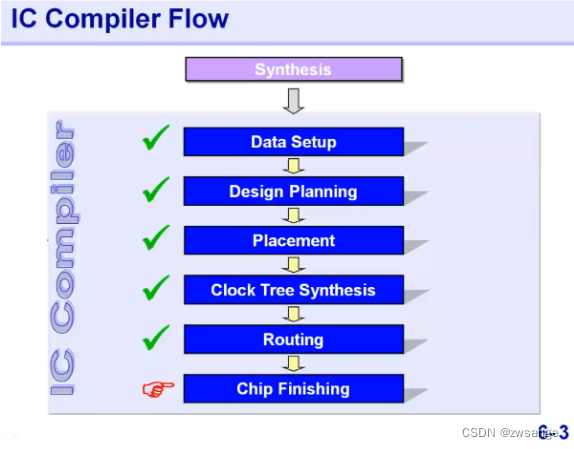

DFM/Chip Finish

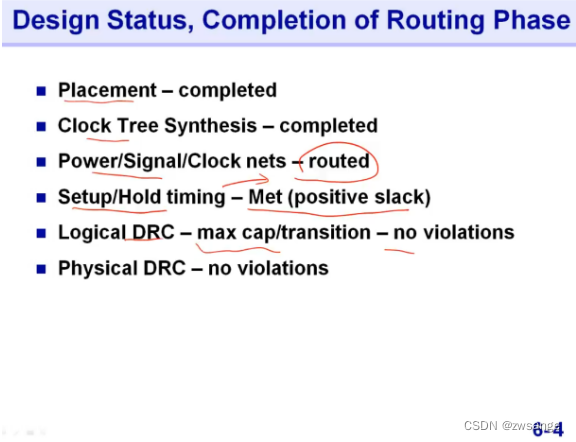

状态检查

在进行DFM之前,我们需要对设计状态进行检查,如上图,logic DRC允许有一些violation存在,其他方面必须要满足;

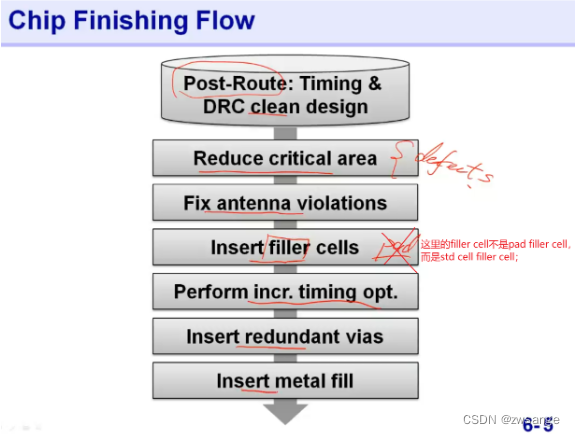

Chip Finish Flow

在post-Route后,timing及DRC应该都是满足的,我们跟着flow进行就好;

这里的reduce critial area就是为了resistant defect;

Insert filler cell指的不是pad filler cell,pad filler cell在前面floorplan就已经完成了,这里指的是std cell filler cell;

在执行完上述一些步骤后,会使layout/placement/route发生一些变化,可能会对timing有影响,因此只要做一下timing opt;

Reduce critical area

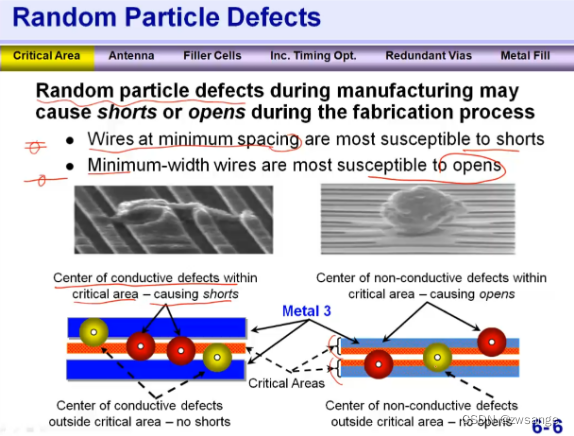

随机散粒缺陷

芯片在制造时,难免会有些异物存在,这些异物可能是导电的,也可能是不导电的;如果是导电的,当位于两条metal直接时就会导致short;而不导电的颗粒落在某根net上,可能就会导致open出现;

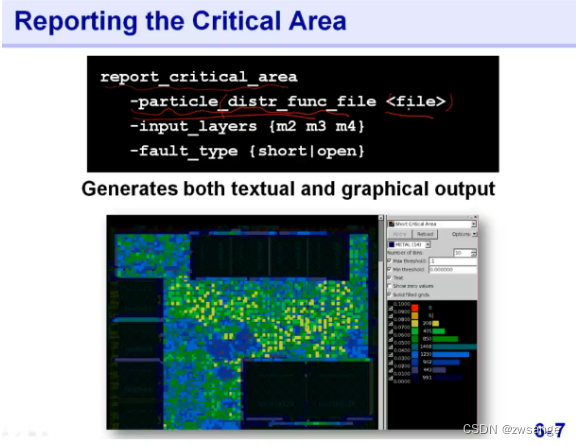

Report critical area

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3282

3282

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?