几个概念分析

OCV: On-Chip-Varification 片上偏差

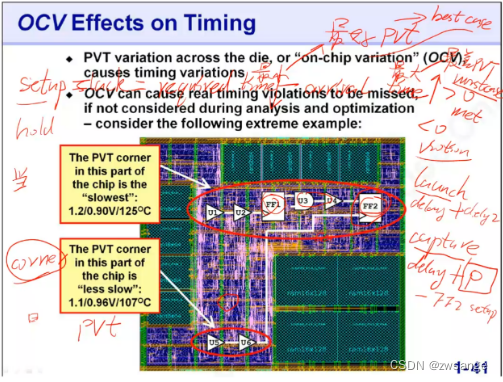

我的理解就是:对于整个芯片而言,工作时不同区域的PVT环境是不同的,因此我们在分析时序时,工具需要利用最worse的情况来评估;

前面提到过,setup slack=Required time - Arrived time,要考虑最worse,那就是Required最小,Arrived最大;由图可知,Required time=capture delay(U5 & U6 & net delay) + T - FF2 setup,要让Required最小,那就需要capture delay最小,那就给capture path上的cell最好的PVT环境条件,让U5 & U6 & net delay最小;

同理,Arrived time=Tck(FF1) + U3 delay + U4 delay,要想让Arrived最大,那就给Arrived path上最worse的PVT条件,让U3 & U4 cell的delay最大;

Thold在计算时,slack=arrived - require,最worse就要求arrived最小,require最大;

一般来说,best case=fast process + High voltage + low T;

worst case=slow process + low voltage + high T;

我们一般会在worst case情况下检查setup,在best case下检查hold;

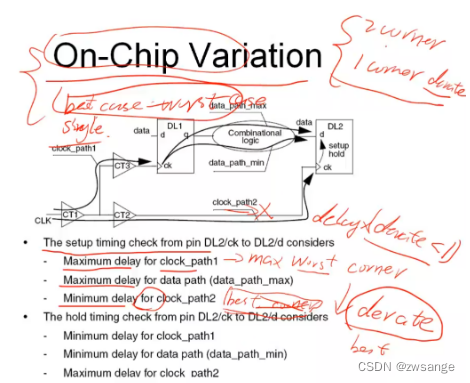

前面提到,在进行setup分析时,我们会考虑worst和best两种工艺corner来计算delay,但实际在进行OCV计算时,一般只选择一种corner加上另一个time derate来处理,比如前面提到的Arrived path cell运用worst corner计算,而capture path delay直接也用worst corner,但是会乘一个derate,这个derate的值是<1的,相当于打折;

上图给出了不同类型delay的time derate选择的值范围;

三种分析模型

计算setup OCV的三种模型,就像上面所提,我们常用OCV mode,但是选择的是单corner+time derate;

简单设置timing derate并举例,注意setup和hold的区别;

primetime report

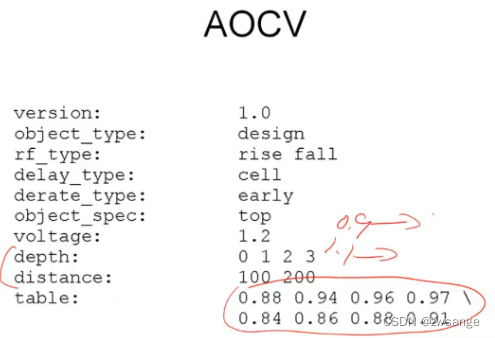

Advanced OCV

我们在实际的项目中发现,对于我们估算的时序约束和实际相比,逻辑深度越大,偏差越小,而逻辑深度越小就偏差越大;

CRPR

CRPR主要就是再说明,前面我们在说data path/clk path 的time derate时,会对相应的path*derate,而对于上图蓝框中的common path共有的路径,两条path在这一段的delay肯定是一样的,所以这一段不需要任何的derate;

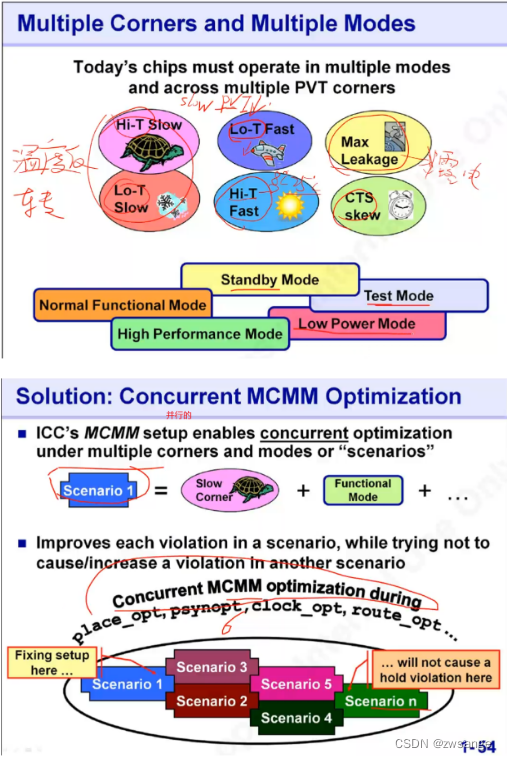

Multi-Corner Multi-Mode(MCMM)

Multi-Mode:可分为FUNC Mode和TEST Mode(用于DFT scan chain);

Multi-Corner:WC & BC & TC (Worst case/Best case/Typical case);

上述的mode和corner组合,就可以得到6种情况,这其中主要关注的有:

①Func+WC---setup;

②Func+BC---hold;

③Func+TC---Power功耗分析;

④TEST+BC---DFT hold;

ICC工具会自动组合corner & mode,每一种称为一种"Scenario",并且会同时检查每种scenario的violation;

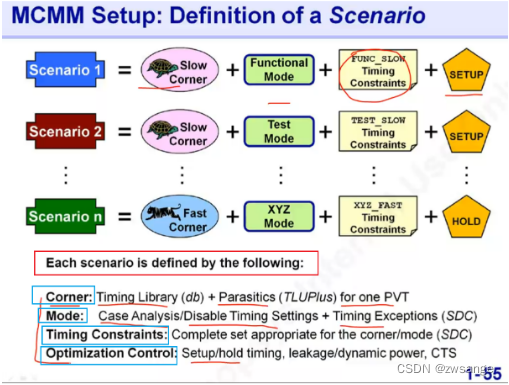

Scenario Definition

每种scenario的定义包含四大部分内容:corner & mode & timing constraints & opt;

MCMM setup

MCMM的data setup主要的区分点有上图(其实就和scenario的定义相关):

①logic lib会有区分,因为我们在DC综合时,不同corner的库文件会有Fast/slow 等的区分,所以在指定.db文件时需要注意(target/link lib);

②timing constraints会有区分,.sdc主要区分的是Mode部分;

③TLU+部分也有区分,因为不同的工艺对应的RC寄生参数是不一样的;

ICC Lab

首先打开ICC ,新手可以打开GUI操作,要把软件当成游戏一样来研究;

后续有设计文件了自己再回来对着视频实践;

3732

3732

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?