目录

输入漏电流Input Leakage Test IIL/IIH

输出漏电流Output Tristate Leakage Test IOZL/IOZH

基本介绍

芯片测试在发展过程中诞生了许多术语,初次接触的人大部分都会被绕晕。因此为方便广大读者理解,在开始介绍测试项之前,需要对测试领域的名词进行解释。还有部分较为抽象的内容,需要略作展开。

术语介绍

DUT——Device Under Test,正在被测试的器件

Pin——器件引脚,信号引脚分为输入,输出,三态和双向四类,负责与外界进行信息交互;电源引脚分为电源和地两类,结构与信号引脚不同,负责给器件内部运行和外部输出提供电平。

输入:在外部信号和器件内部逻辑之间起缓冲作用的信号输入通道;输入管脚感应其上的电压并将它转化为内部逻辑识别的“0”和“1”电平

输出:在芯片内部逻辑和外部环境之间起缓冲作用的信号输出通道;输出管脚提供正确的逻辑“0”或“1”的电压,并提供合适的驱动能力(电流)

三态:输出的一类,它有关闭的能力(达到高电阻值的状态)

双向:同时拥有输入、输出功能并能达到高阻态的管脚

VCC:TTL器件的供电输入引脚,TTL即晶体管逻辑电路,一般由三极管构成

VDD:CMOS器件的供电输入引脚,CMOS即互补金属氧化物半导体逻辑电路,一般由MOS管构成

VSS:为VCC或 VDD提供电流回路的引脚

GND:地,连接到测试系统的参考电位节点或VSS,为信号引脚或其他电路节点提供参考0电位;对于单一供电的器件,我们称VSS为GND

Defect:器件的缺陷

Fault:表现出异常的错误情况

Force:驱动电流或电压到器件引脚上,与Apply同义

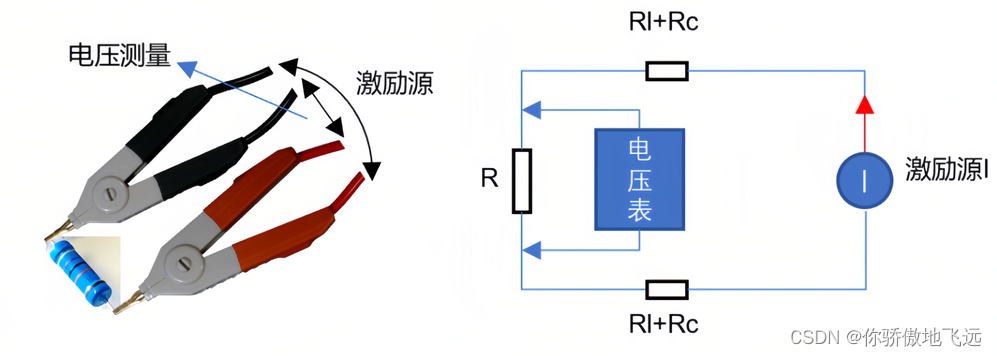

Sence:检测器件引脚上的电压,force与sence组成开尔文连接,将施加电压电流的与检测电压电流的部分分开组成四脚接法,以消除导线上微小的分压,提高测试精度。Sence线路还可以会将结果反馈给电源,让其与理想值进行比较,并作出相应的补偿修正以尽可能减小偏差。

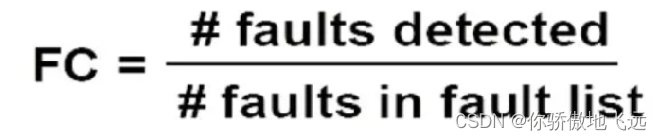

测试覆盖率:测试项所覆盖的可能出现的所有错误类型在存在的所有错误类型中的占比

测试向量介绍

Pattern(也叫Vecter):一组时序波形,数据有0,1,L,H,Z等符号位对应不同的输入和输出状态,可设置电平,频率和占空比,通常翻译为测试向量。Pattern本质上是一组真值表,至于Vecter以我的理解是指装载在单个引脚上的一组时序数据,如(0,1,0,0,0,1,1,1,0,H,0,0,Z),所有引脚的Vecter的组合就是Pattern(关于这部分的说法仅代表个人理解,欢迎大家讨论)。通常Pattern和Vecter描述的是同一样东西。Pattern可用于设置芯片状态,读写信息,测试通信总线等。可配置为多种信号格式,有多个电平状态,是ATE测试中非常重要的部分。

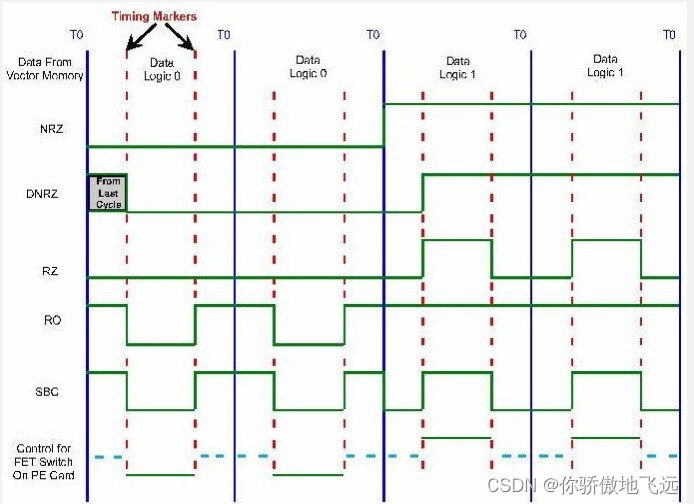

NRZ Non Return to Zero,不返回,代表存储于向量存储器的实际数据,它不含有时沿信息,只在每个周期的起始(T0)发生变化。

DNRZ Delayed Non Return to Zero,延迟不返回,顾名思义,它和NRZ一样代表存储于向量存储器的数据,只是周期中数据的转变点不在T0。如果当前周期和前一周期的数据不同,DNRZ会在预先定义的延时点上发生跳变。

RZ Return to Zero,返回0,当数据为1时提供一个正向脉冲,数据为0时则没有变化。RZ信号含有前(上升)沿和后(下降)沿这两个时间沿。当相应管脚的所有向量都为逻辑1时,用RZ格式则等于提供正向脉冲的时钟。一些上升沿有效的信号,如片选(CS)信号,也会要求使用RZ格式。

RO Return to One,返回1,与RZ相反,当数据为0时提供一个负向脉冲,数据为1时则保持。RO信号也有前(下降)沿和后(上升)沿。当相应管脚的所有向量都为逻辑0时,RO格式提供了负向脉冲的时钟。一些下降沿有效的信号,如始能(OE/)信号,会要求使用RO格式。

ZD Z(Impendance)Drive,高阻驱动,允许输入驱动在同一周期内打开和关闭。当驱动关闭,测试通道处于高阻态;当驱动打开,则根据向量给DUT送出逻辑0或1。

SBC Surround By Complement,补码环绕,当前后周期的数据不同时,它可以在一个周期内提供3个跳变沿,信号更为复杂:首先在T0翻转电平,等待预定的延迟后,在定义的脉冲宽度内表现真实的向量数据,最后再次翻转电平并在周期内剩下的时间保持。SBC是运行测试向量时唯一能同时保证信号建立(setup)和保持(hold)时间的信号格式,也被称为XOR格式。

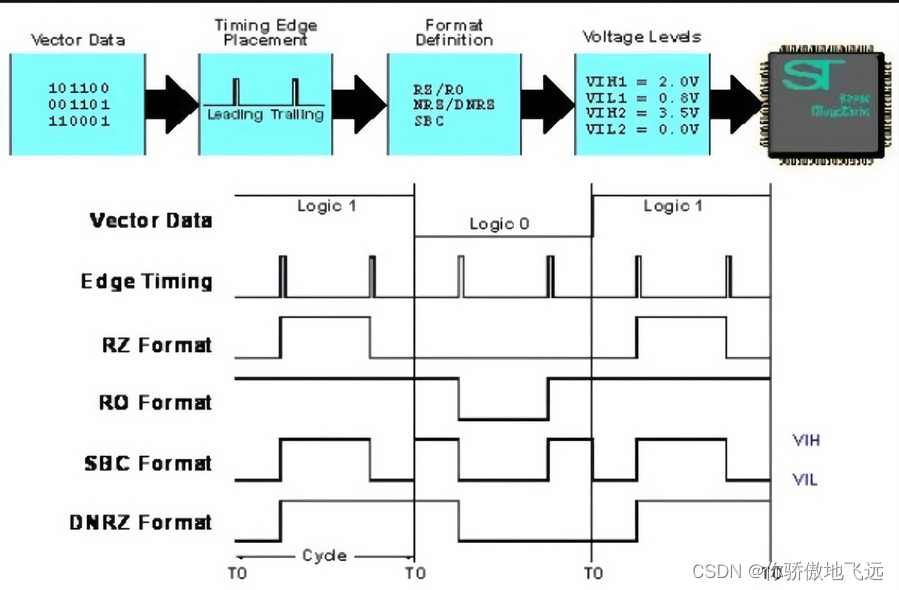

测试向量的使用

一旦决定了测试周期,周期内各控制信号的布局及时沿位置也就可以确定了。通常来说,输入信号有两类:控制信号和数据信号。数据信号在控制信号决定的时间点提供数据读入或锁定到器件内部逻辑。

第一个要决定的是控制信号的有效时沿和数据信号的建立和保持时间,这些信息将决定周期内各输入信号时间沿的位置。

接下来决定各输入信号的格式。时钟信号通常使用RZ(正脉冲)或RO(负脉冲)格式;上升沿有效的信号如片选(CS)或读(READ)常使用RZ格式;下降沿有效的信号如输出始能(OE/)常使用RO格式;拥有建立和保持时间要求的数据信号常使用SBC格式;其他的输入信号则可以使用NRZ或DNRZ格式。

输入信号由测试系统各区域提供的数据组合创建,最后从测试头输出的信号波形是测试向量、时沿设置、信号格式及逻辑高低电平设置共同作用的结果。

关于测试机设备和机台的部分已在上篇文章中介绍过,这里不再赘述。

开短路测试——OS测试

开短路测试主要是测试引脚到VDD和GND的保护二极管是否正常工作。这两个保护二极管是为了防止引脚到VDD或GND短路产生大电流烧坏设备。如果出现了开短路故障会使芯片失效。由于该项测试可以很快地检测出较严重的缺陷,因此通常被放在第一步进行,归入检查测试机是否与芯片正确连接的连通性测试流程中。

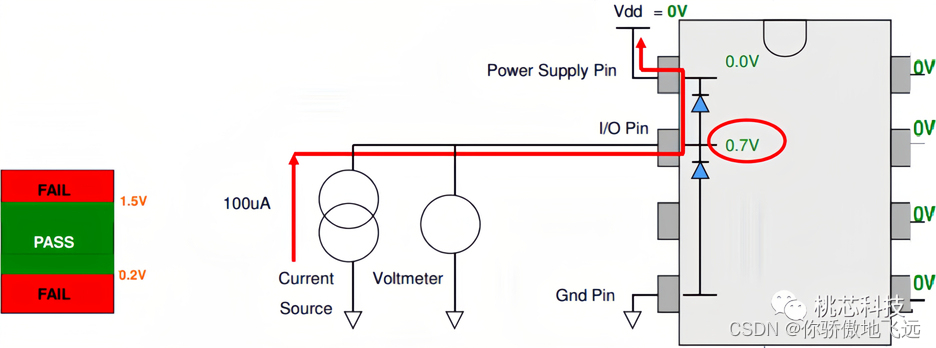

Pin对VDD开短路测试

Step1: 所有不测试的pin都置0v。

Step2: 在需要测试的pin上force一个100uA的电流。

Step3: 量测这个在测试的pin上的电压。

--如果tester与这个测试pin接触很好,并且这个pin本身没有任何的开路或者短路到VDD/ground/其它的pin脚上,那么理想的测试到的电压会是0.7v。

--如果这个在测试的pin有开路的fault,会量测到一个大的正电压。

--如果这个在测试的pin有短路到vdd/ground/其它的pin上,会量测到一个接近0v的电压。

考虑到实际的电路的情况,一般limit设置为0.2V~1.5V。

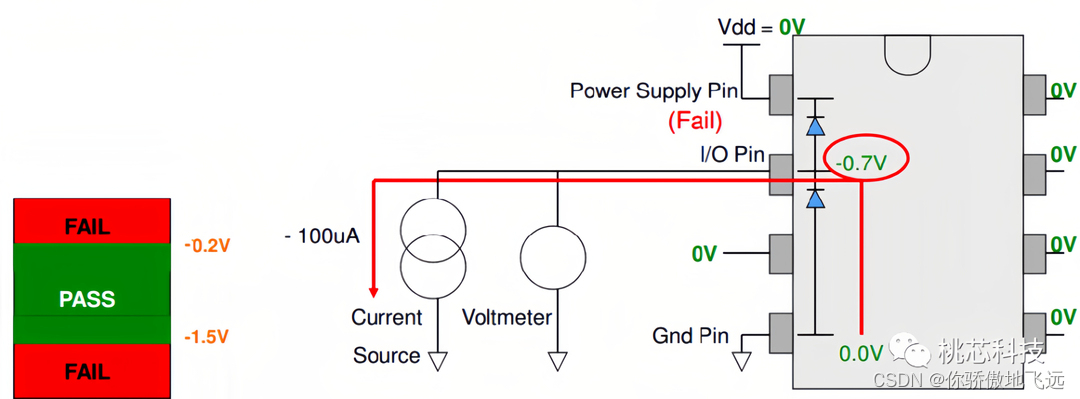

Pin对GND开短路测试

Step1: 所有不测试的pin都置0v。

Step2: 在需要测试的pin上force一个-100uA的电流。

Step3: 量测这个在测试的pin上的电压

--如果测试机台与这个测试pin接触很好,并且这个pin本身没有任何的开路或者短路到VDD/ground/其它的pin脚上,那么理想的测试到的电压会是-0.7v。

--如果这个在测试的pin有开路的fault,会量测到一个大的负电压。

--如果这个在测试的pin有短路到vdd/ground/其它的pin上,会量测到一个接近0v的电压。

考虑到实际的电路的情况,一般limit设置为-1.5V ~-0.2V。

电源电流测试——IDD测试

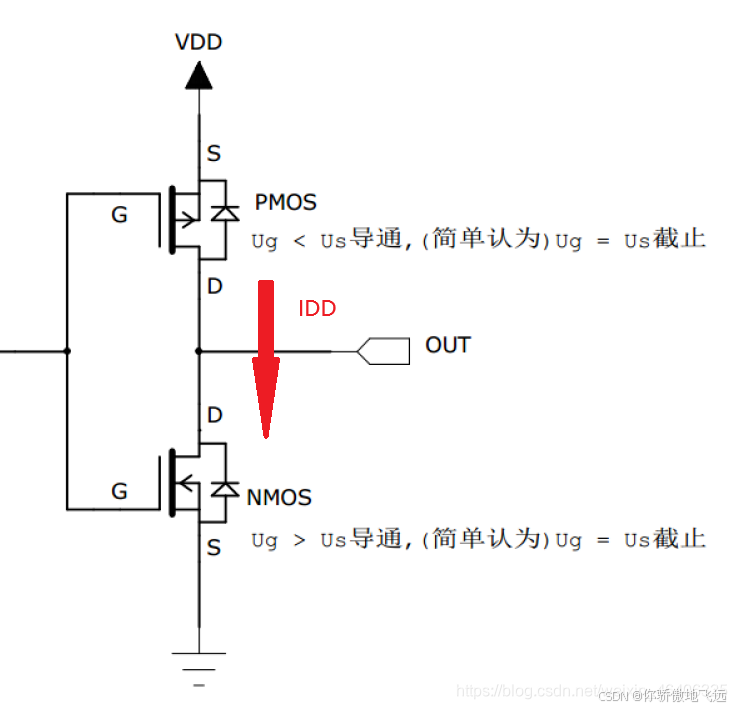

IDD测试(或者叫做ICC测试),在CMOS电路中是测试漏极到漏极(Drain to Drain)的流动电流,在TTL电路中是测试集电极到集电极(Collector to Collector)的流动电流。

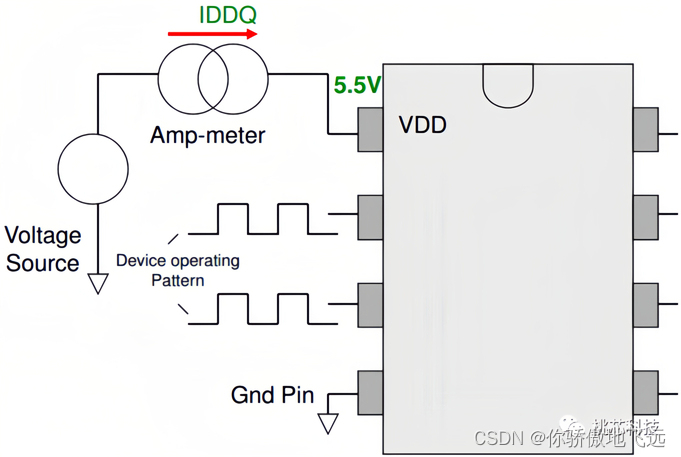

静态CMOS电流IDDQ

CMOS电路具有低功耗的优点,静态条件下由泄露电流引起的功耗可以忽略,仅仅在转换期间电路从电源消耗较大的电流。Q代表静态(quiescent),则IDDQ表示MOS电流静态时从电源获取的电流。

在典型的CMOS电路中由充放电电容引起的功耗占主导地位,直接通路电流引起的功耗可以通过设计控制在限定范围内,而漏电在目前的制程下可以忽略。在静态时无故障的电源总电流为微安数量级;当电路出现桥接或栅源短接等故障时,会在静态CMOS电路中形成一条从电源到地的低阻通路,会导致电源总电流超过毫安数量级。所以静态电源电流IDDQ测试可以通过检测CMOS电路静态时的漏电流来判断电路是否存在问题。

IDDQ测试是源于物理缺陷的测试,也是可靠性测试的一部分,其有着测试成本低和能从根本上找出电路的问题(缺陷)所在的特点。即若在电压测试生成中加入少量的IDDQ测试图形,就可以大幅度提高电压测试的覆盖率。即使电路功能正常,IDDQ测试仍可以检测出桥接、短路、栅氧短路等物理缺陷。

Step1: 给VDD上最高电压,并且tester的电压源设定一个钳制电流,防止电流过大损测试机。

Step2: 运行一个特定的pattern,去调整尽量多的晶体管开启。等待 5~10ms。

Step3: 量测流过VDD上的电流。

Step4: 运行另外一个特定的pattern,去调整尽量多的晶体管关断。等待5~10ms。

Step5: 量测流过VDD上的电流。

Step6: 重复上述的step2到step5的步骤大概5~10次,取读出的平均值。跟datasheet中的规范进行比较,可以排查出相应的问题。

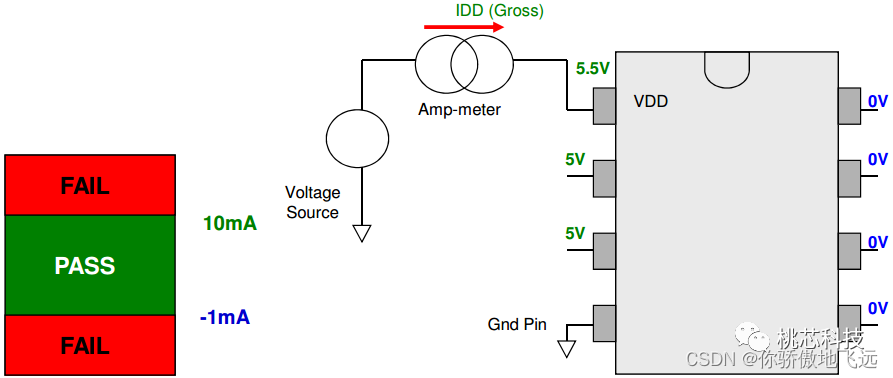

电源短路Gross-IDD

电源pin的短路测试,通常Open/short测试后马上进行,如果在制造过程中有事故,导致了电源到地的短路,会测试到非常大的电流,也会反过来损害到测试机本身。

Step1: 给VDD上最高电压,并且测试机台的电压源设定一个钳制电流,防止电流过大损测试机。

Step2: 所有的输入pin置高,所有的输出pin置0. 等待5~10ms。

Step3: 测量流过VDD上的电流,正向或者反向电流过高都说明电源到地短路了。

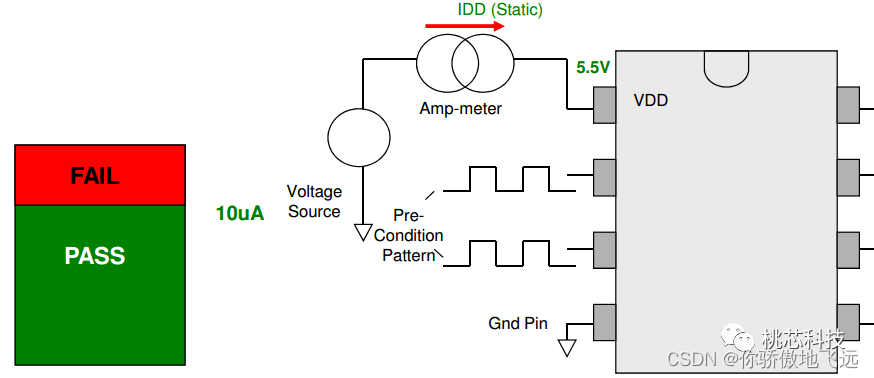

静态功耗Static-IDD

这个项目是测试当芯片在静态或者空闲状态的情况下,流过VDD的漏电,这个参数对低功耗应用场景特别重要;这项测试也能检测出一些在制造中产生的margin defect,这些defect非常有可能会给芯片带来潜在的可靠性风险。

Step1: 给VDD上最高电压,并且测试机台的电压源设定一个钳制电流,防止电流过大损测试机。

Step2: 运行预设置Pattern,把芯片设置到低功耗状态。等待5~10ms。

Step3: 循环测量流过VDD上的电流,根据datasheet中的标识设定limit,超过limit即表示坏品。

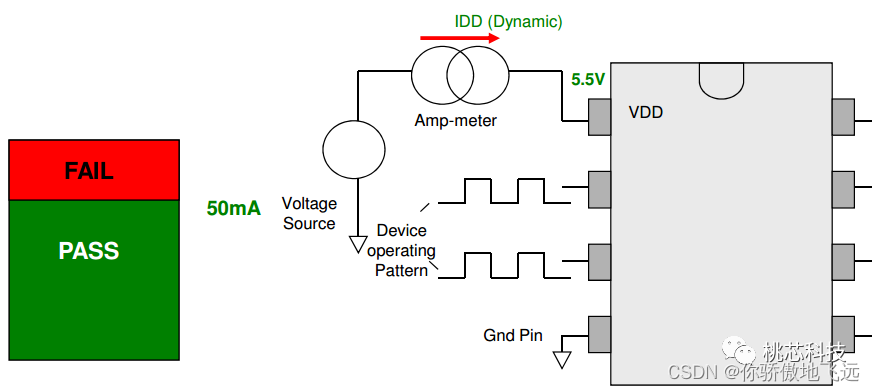

动态功耗Dynamic-IDD

这个项目是测试当芯片在不停地运行某种功能的情况下,流过VDD的电流。这个类似于某种工作情况下的功耗,需要符合产品规格中的值,对于功耗要求严格的应用方案,此项指标非常重要。

Step1: 给VDD上最高电压,并且测试机台的电压源设定一个钳制电流,防止电流过大损测试机。

Step2: 让芯片持续不断的运行特定的Pattern,等待5~10ms。

Step3: 循环测量流过VDD上的电流,根据datasheet中的标识设定limit,超过limit表示坏品。

漏电流测试——Leakage测试

芯片内部晶体管不可能在理想的状态,因此或多或少会存在一定的漏电流,需要测试漏电,保证漏电是在正常的允许的范围内,而不是潜在的defect。

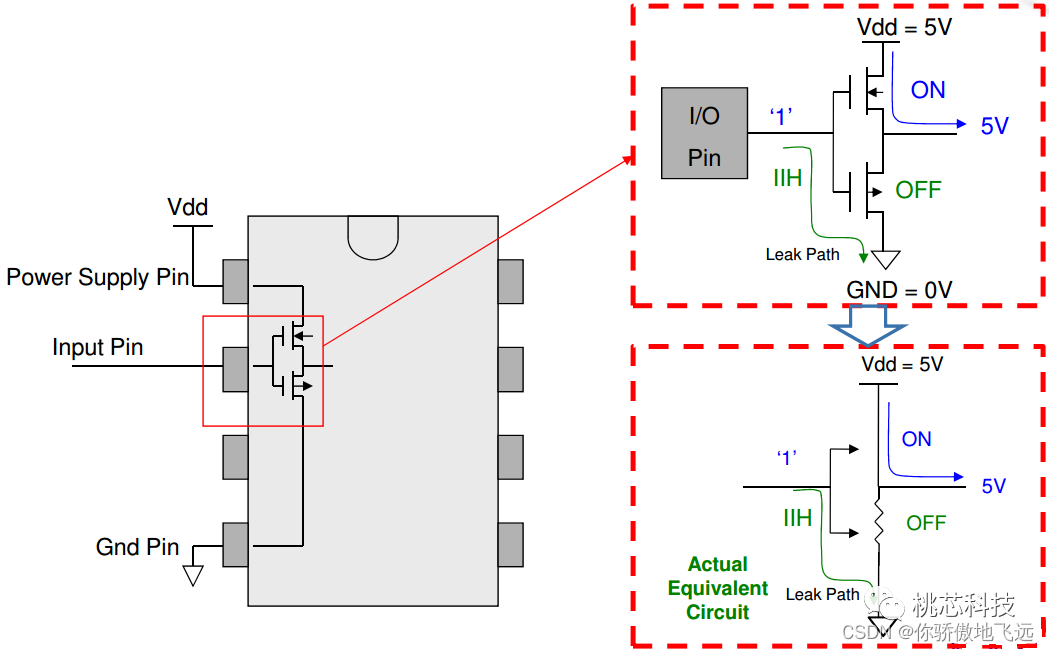

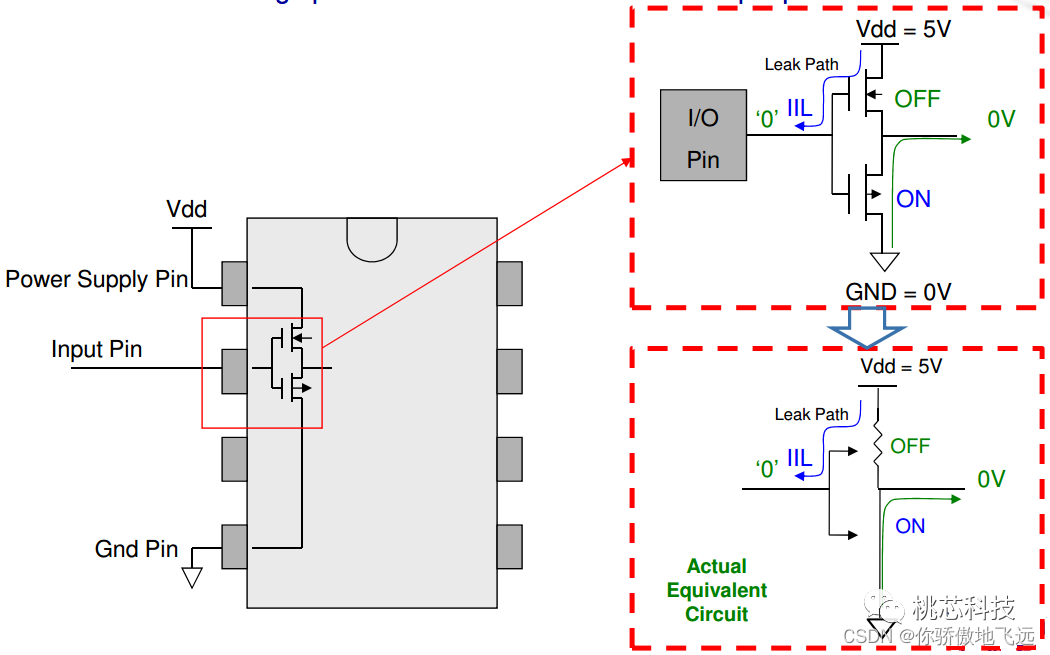

输入漏电流Input Leakage Test IIL/IIH

IIH是当芯片的某个input pin被设定为输入VIH时,从这个input pin到芯片的ground之间的漏电流

Step1: 给VDD上最高电压,其他不参与测试的引脚置高电平,并且测试机台的电压源设定一个钳制电流,防止电流过大损测试机。

Step2: 给输入引脚施加逻辑1电平,等待5~10ms。

Step3: 循环测量流过输入引脚上的电流,根据datasheet中的标识设定limit,超过limit表示坏品。

IIL是当芯片的某个input pin被设定为输入VIL时,从芯片的VDD 到这个input pin的之间的漏电流

Step1: 给VDD上最高电压,其他不参与测试的引脚置高电平,并且测试机台的电压源设定一个钳制电流,防止电流过大损测试机。

Step2: 给输入引脚施加逻辑0电平,等待5~10ms。

Step3: 循环测量流过输入引脚上的电流,根据datasheet中的标识设定limit,超过limit表示坏品。

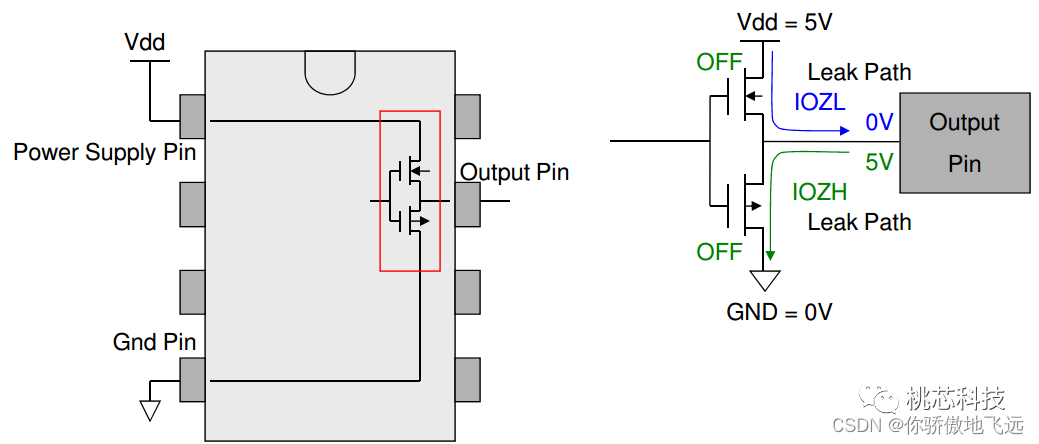

输出漏电流Output Tristate Leakage Test IOZL/IOZH

Tristate表示的是输出pin是高阻状态,当这个时候,如果输出pin上有电压VDD,那么从输出pin到芯片的ground上会有漏电(IOZH);如果输出pin接地,那么从芯片的VDD到这个输出pin上也会有漏电(IOZL)。这些漏电必须保持在芯片规格规定的范围内,以确保芯片的正常工作,不会有潜在的defect产生。

Step1: 给VDD上最高电压,其他不参与测试的引脚置高电平,并且测试机台的电压源设定一个钳制电流,防止电流过大损测试机。

Step2: 给输出引脚施加逻辑0电平,等待5~10ms。

Step3: 测量流过输出引脚上的电流。

Step4: 给输出引脚施加逻辑1电平,等待5~10ms。

Step5: 测量流过输出引脚上的电流。

Step6:循环Step2-5,根据datasheet中的标识设定limit,超过limit表示坏品。

逻辑电平测试——VIH/VIL,VOH/VOL测试

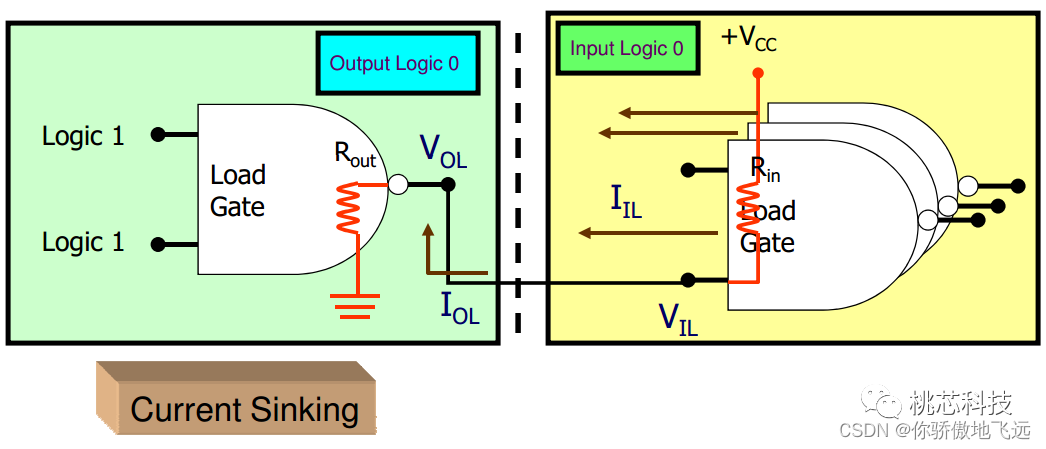

VOL是输出pin为状态0的最大电压,IOL是对应的电流;VIL是输入pin识别为逻辑状态0的最大电压,IIL是对应的电流。该项测试实际是在测试当此状态下的输出pin对地,输入pin对VCC的电阻大小。

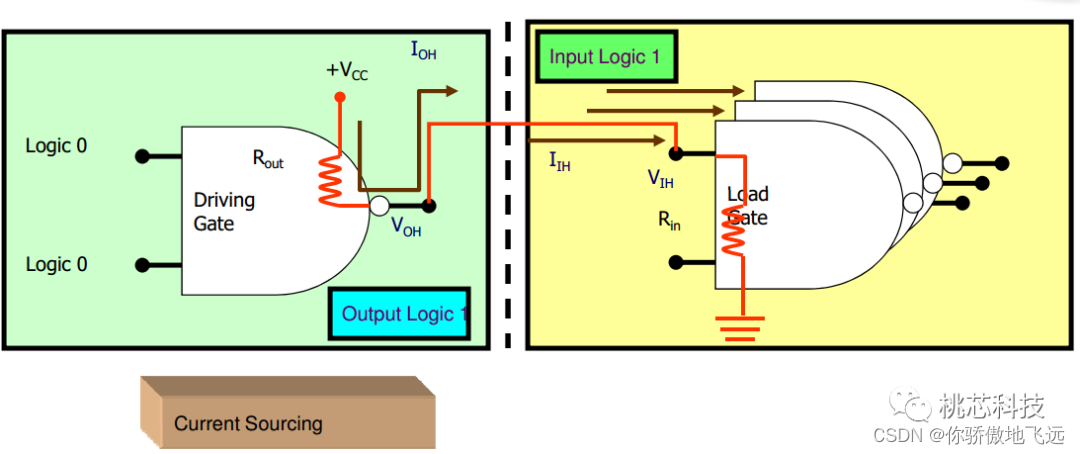

VOH是输出pin为状态1的最小电压,IOH是对应的电流;VIH是输入pin识别为逻辑状态1的最小电压,IIH是对应的电流。该项测试实际是在测试当此状态下的输出pin对VCC,输入pin对地的电阻大小。

参考:

道客巴巴,《The Fundamentals Of Digital Semiconductor Testing 中文版本》

桃心科技公众号,《芯片测试介绍(一)(二)(三)》

1954

1954

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?