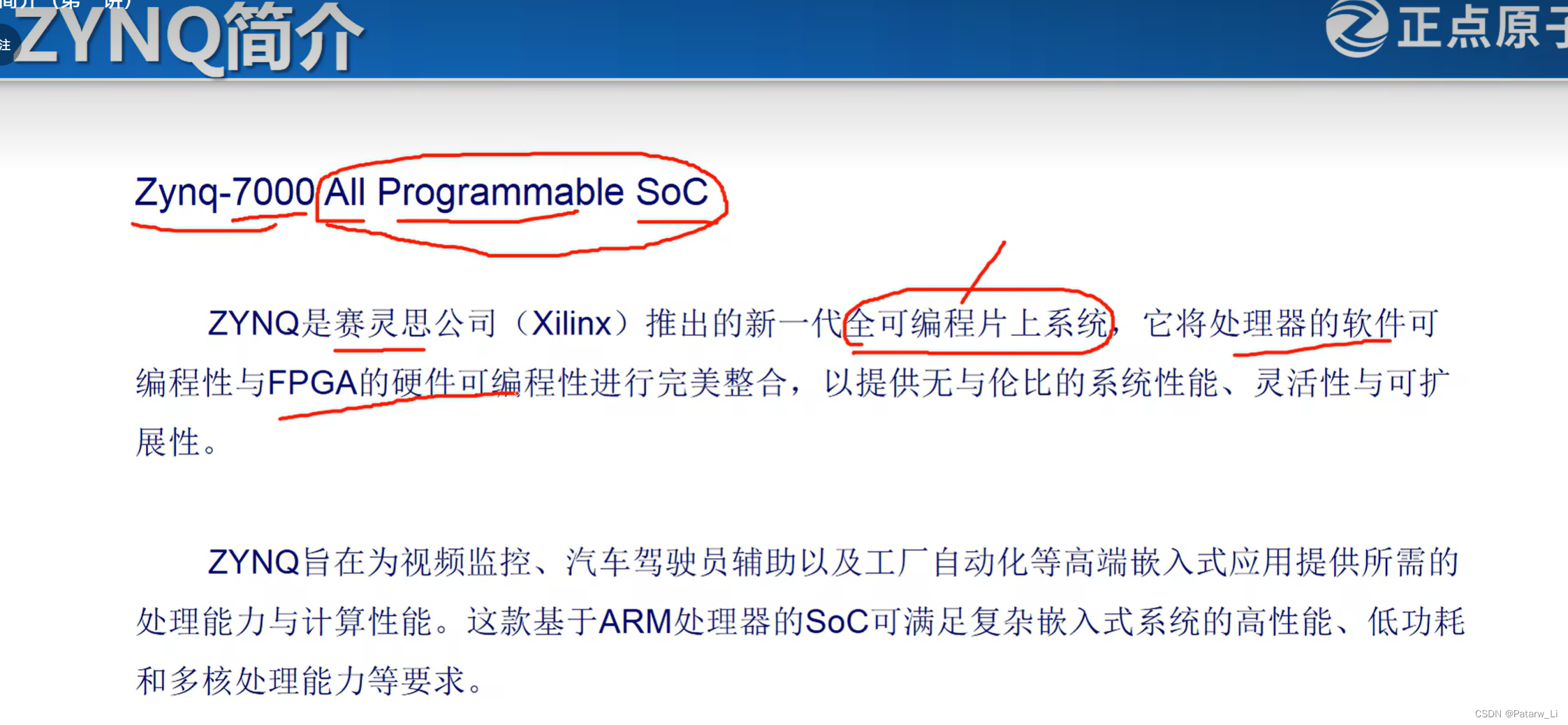

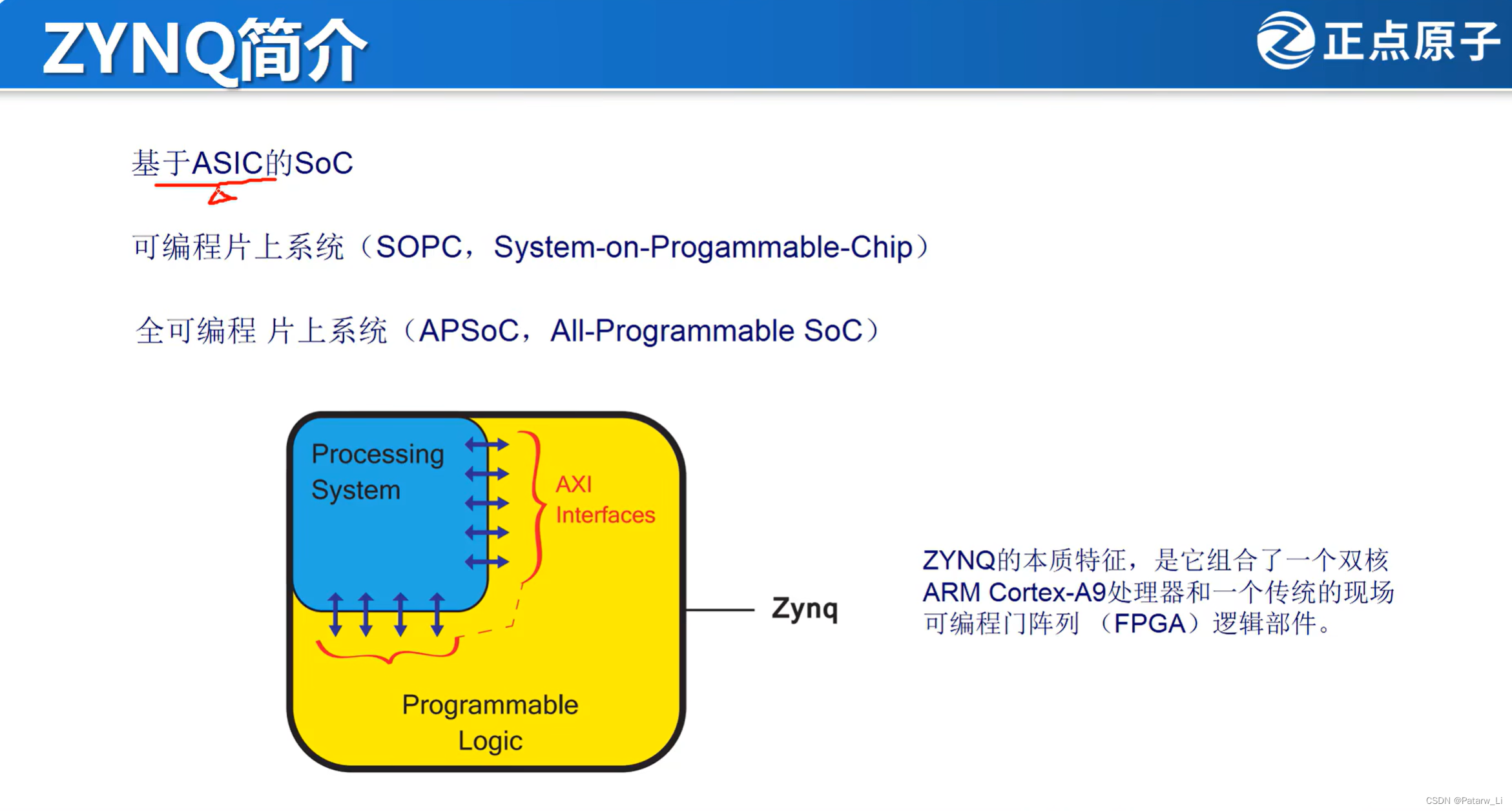

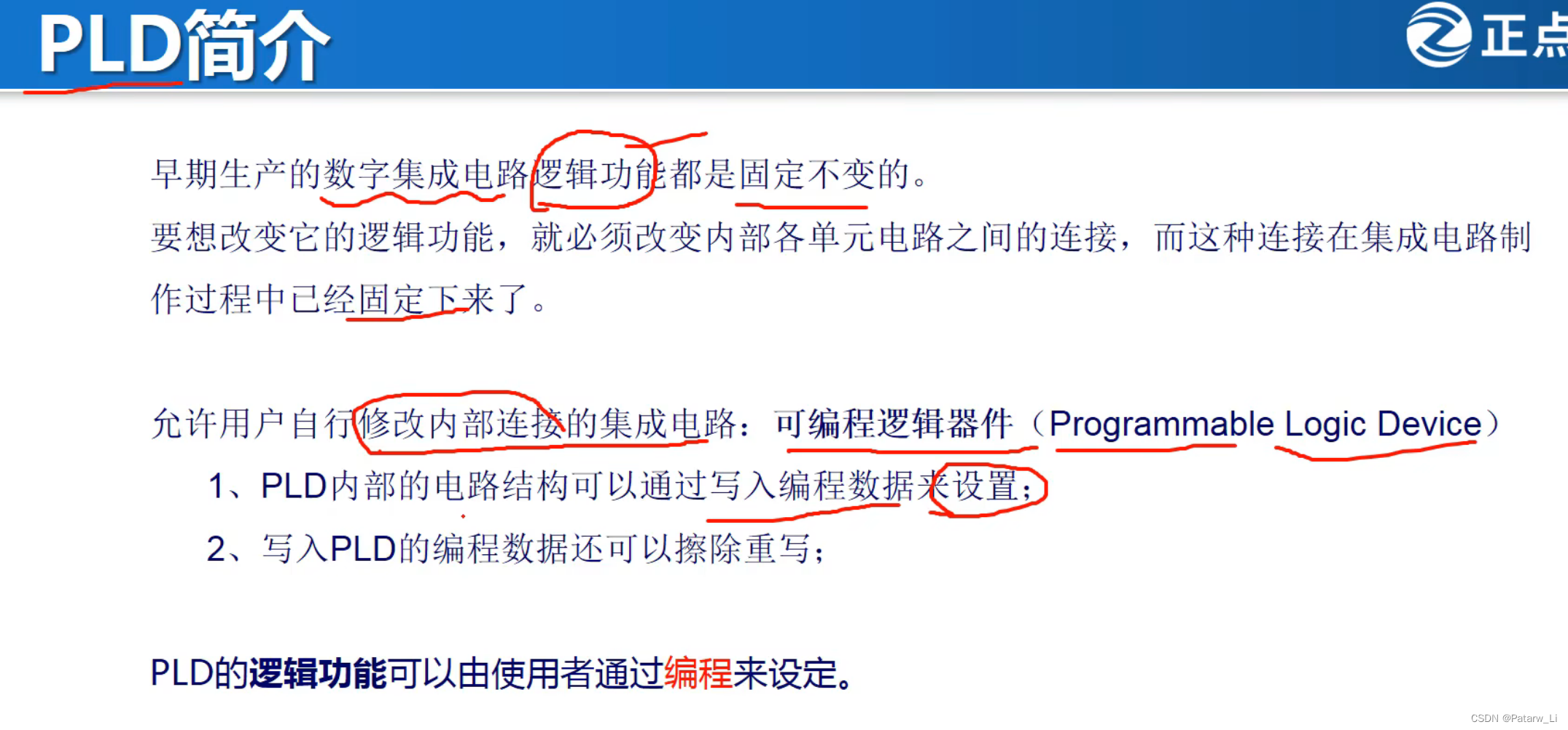

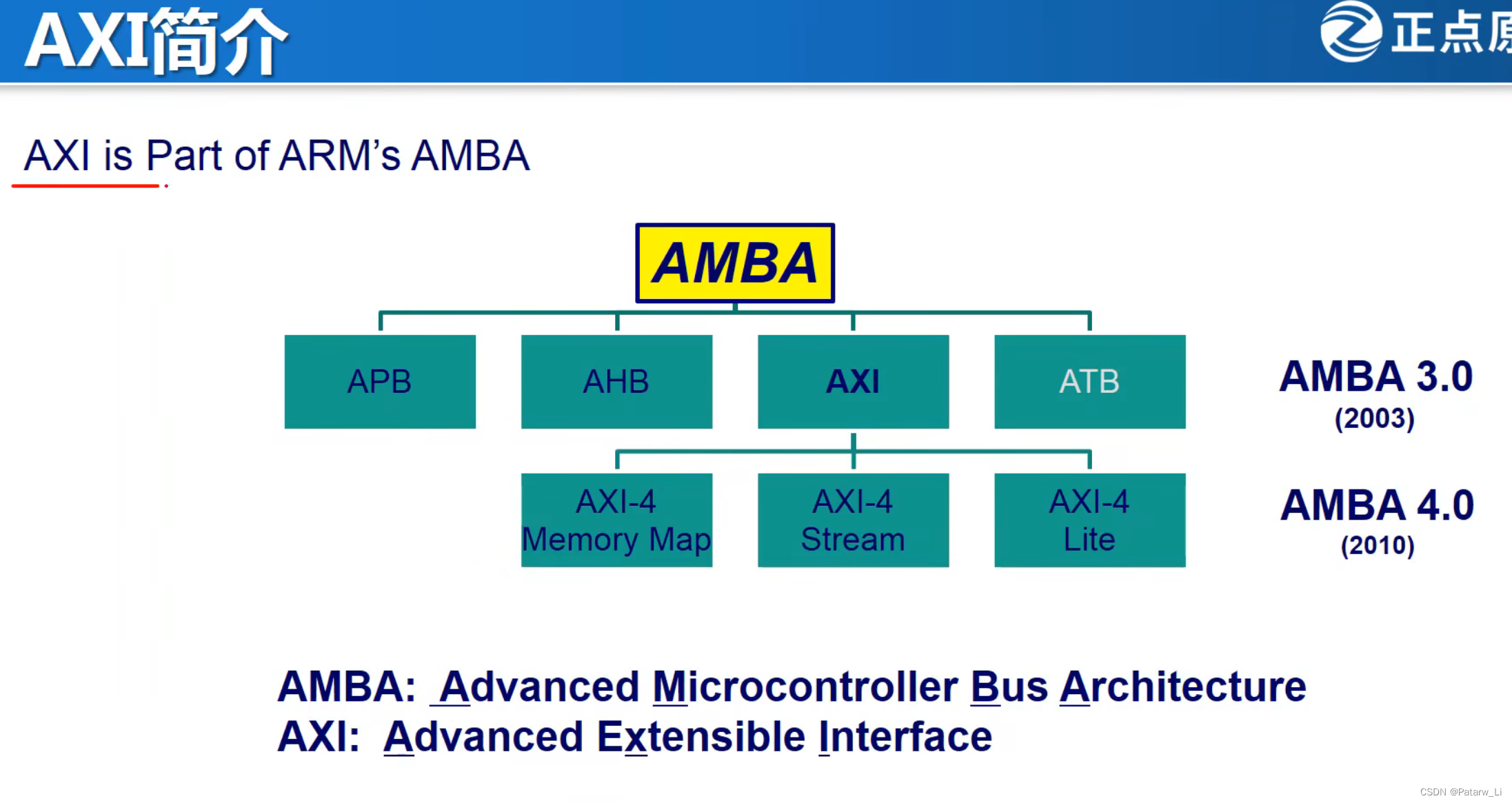

一、简介

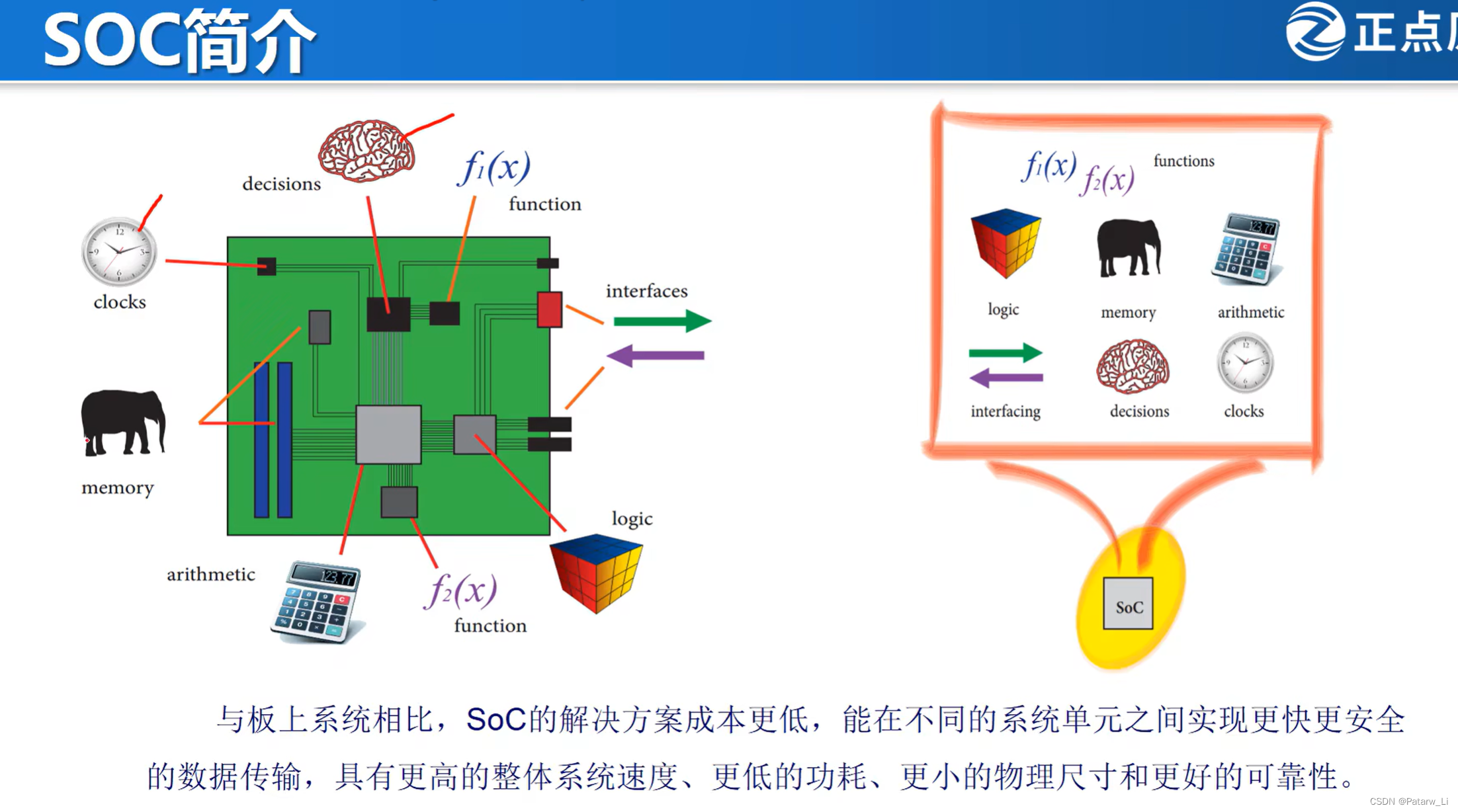

板上系统(sob)和片上系统(soc)

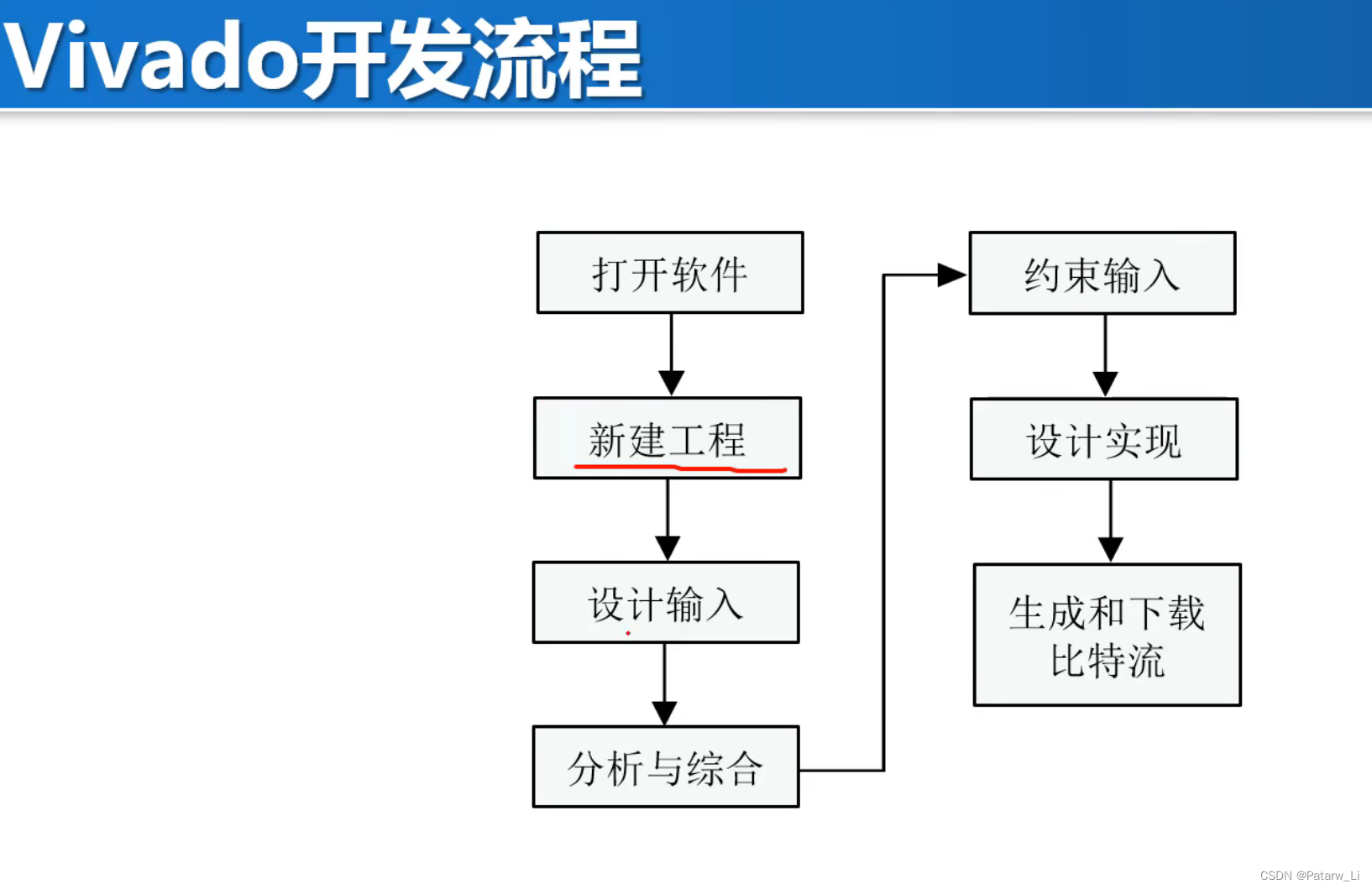

二、PL部分开发流程

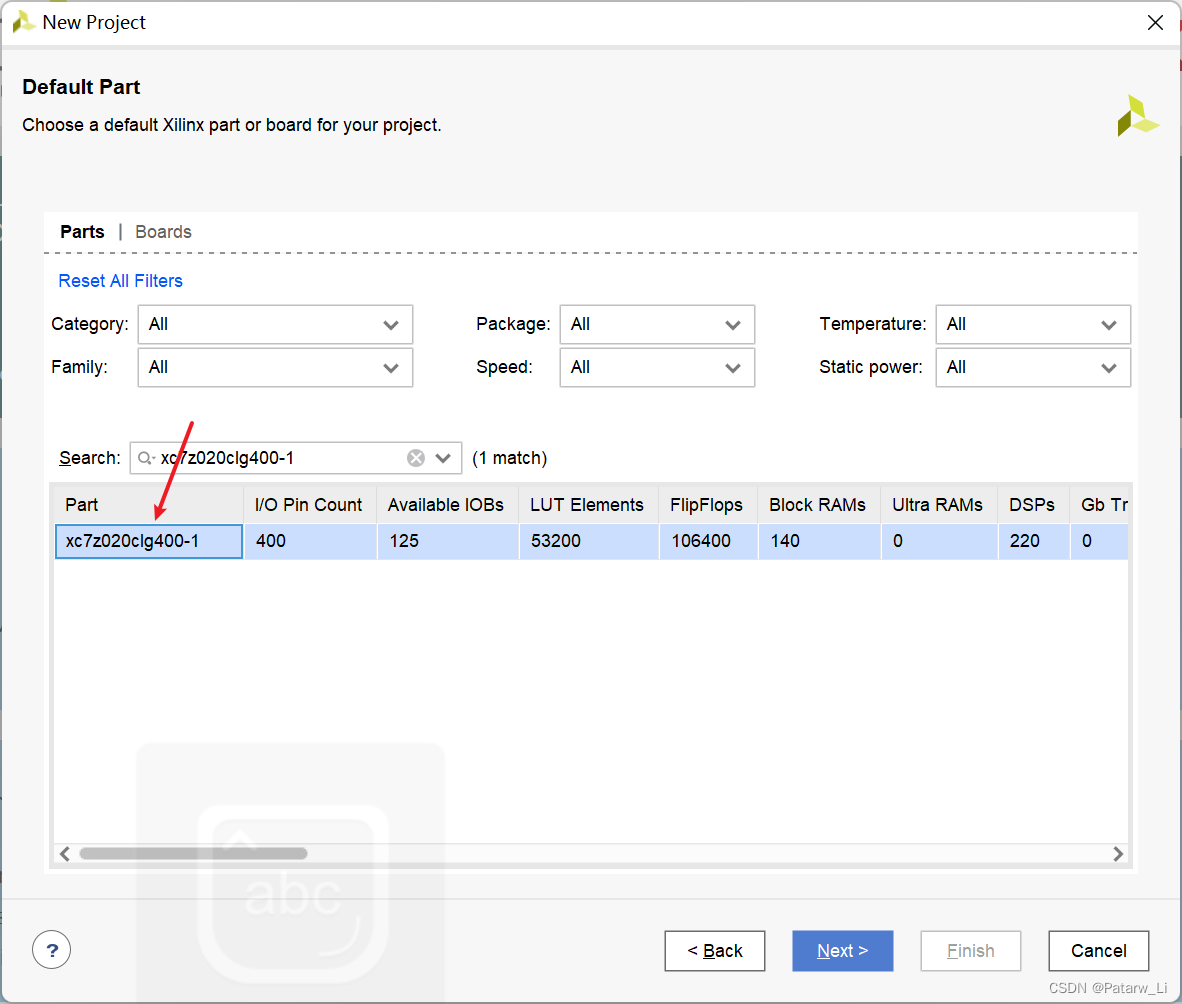

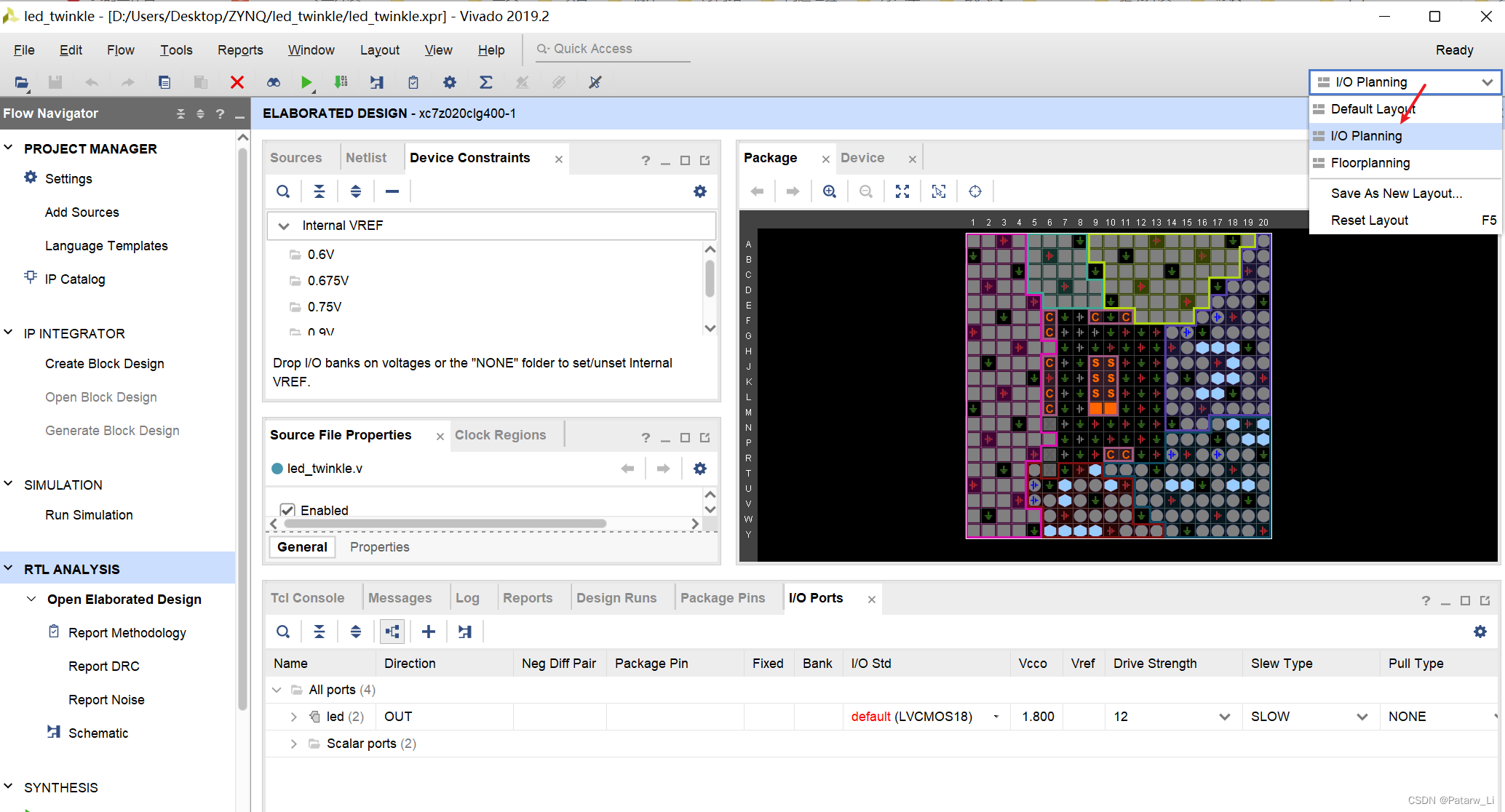

创建工程,选择芯片型号,我们这里用的是xc7z020clg400-1(ZYBOZ7):

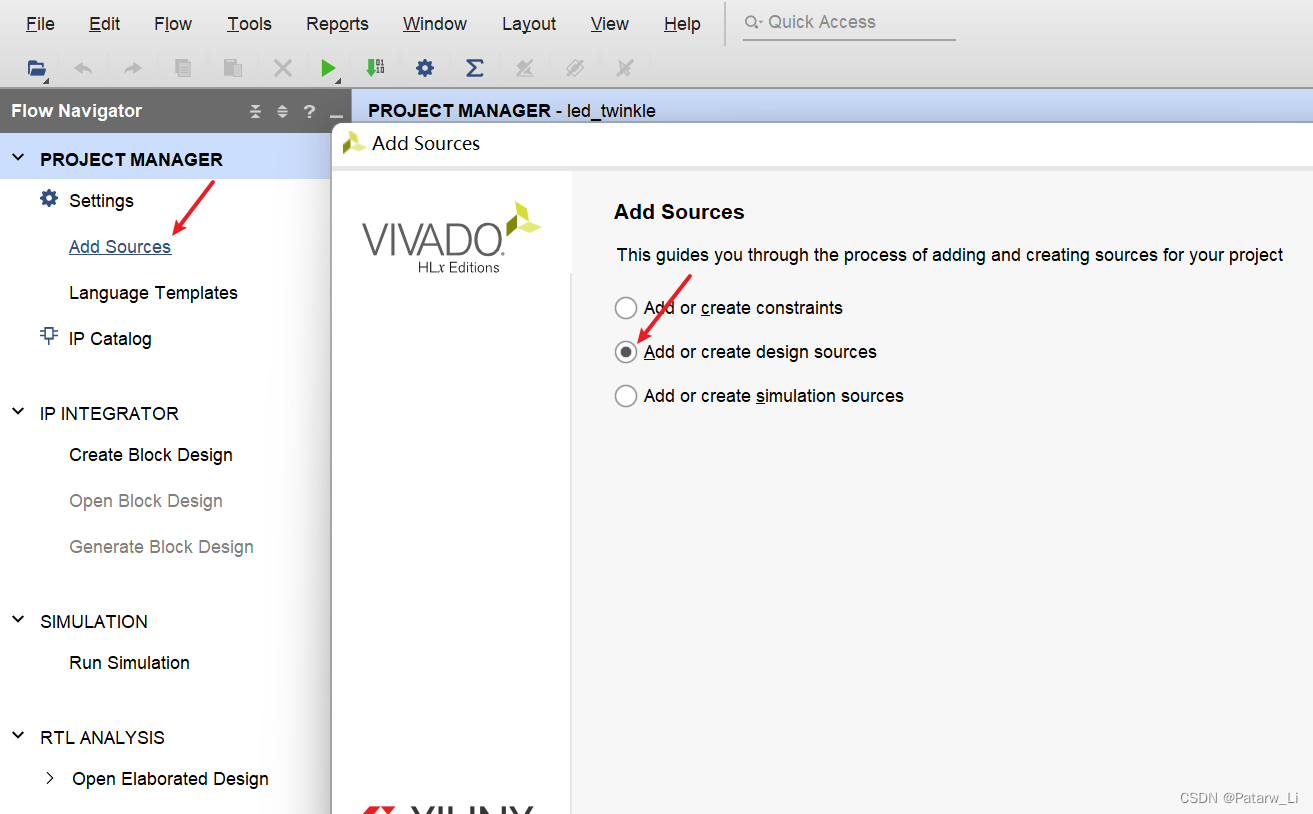

添加文件:

添加文件:

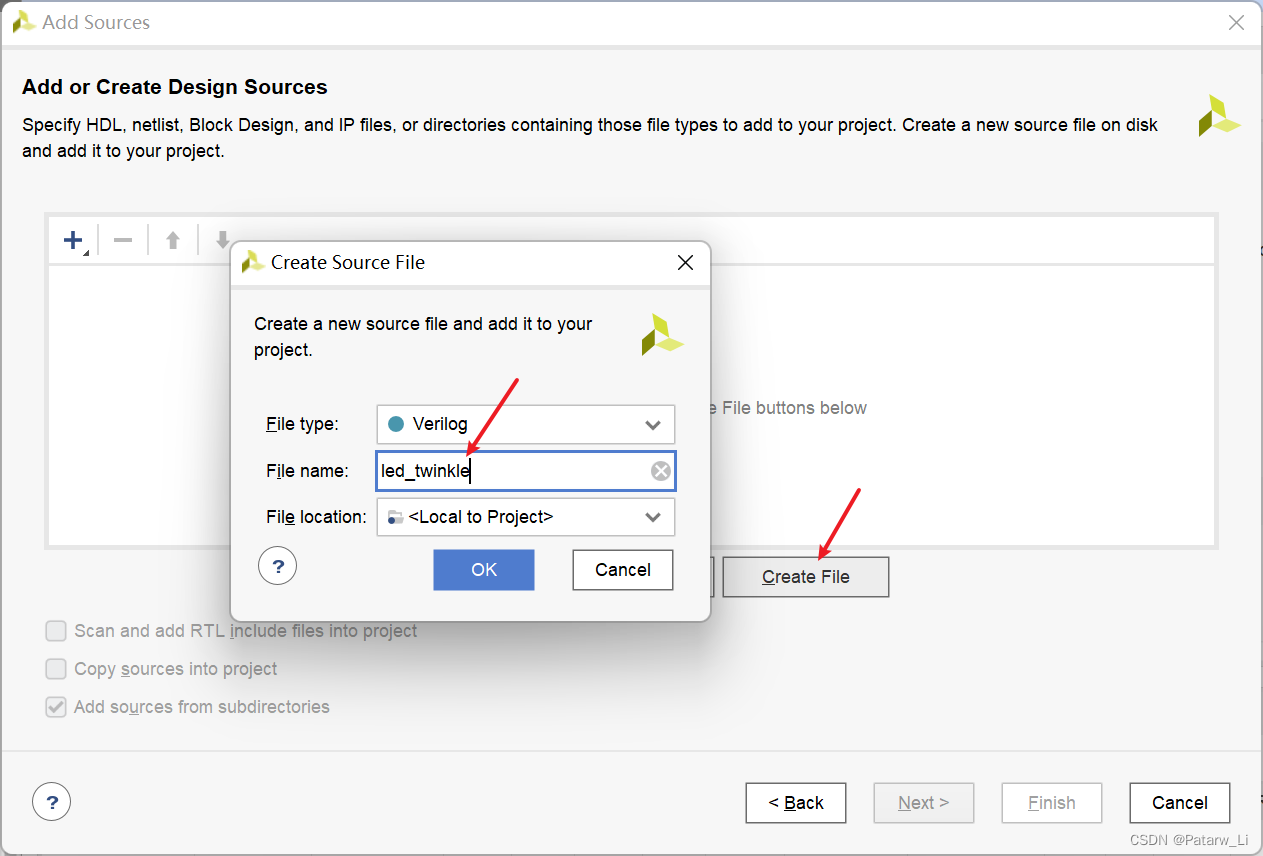

创建verilog文件,一般顶层文件名称和工程名称相同:

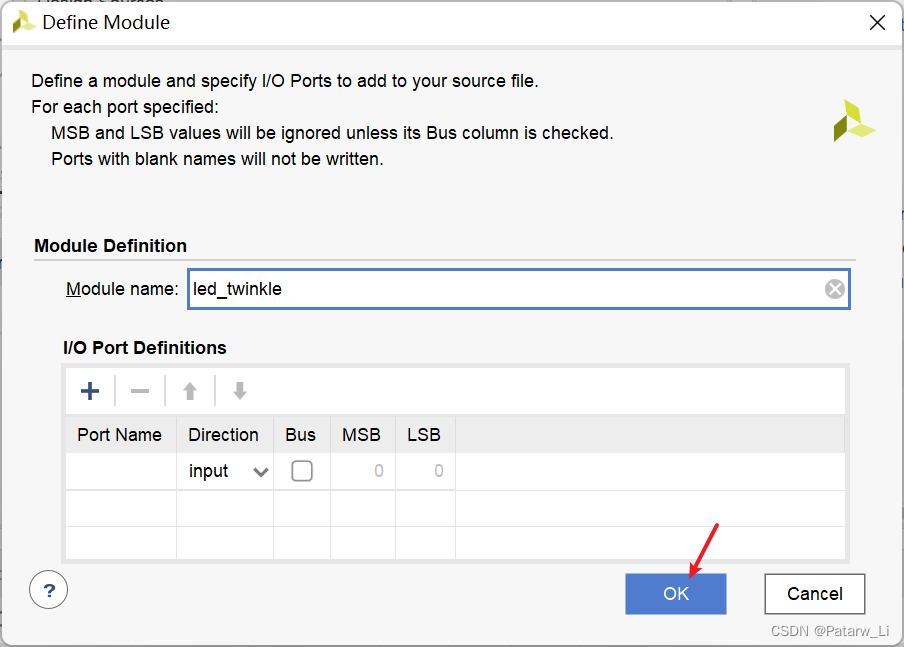

Finish后跳出下面页面,点击OK:

Finish后跳出下面页面,点击OK:

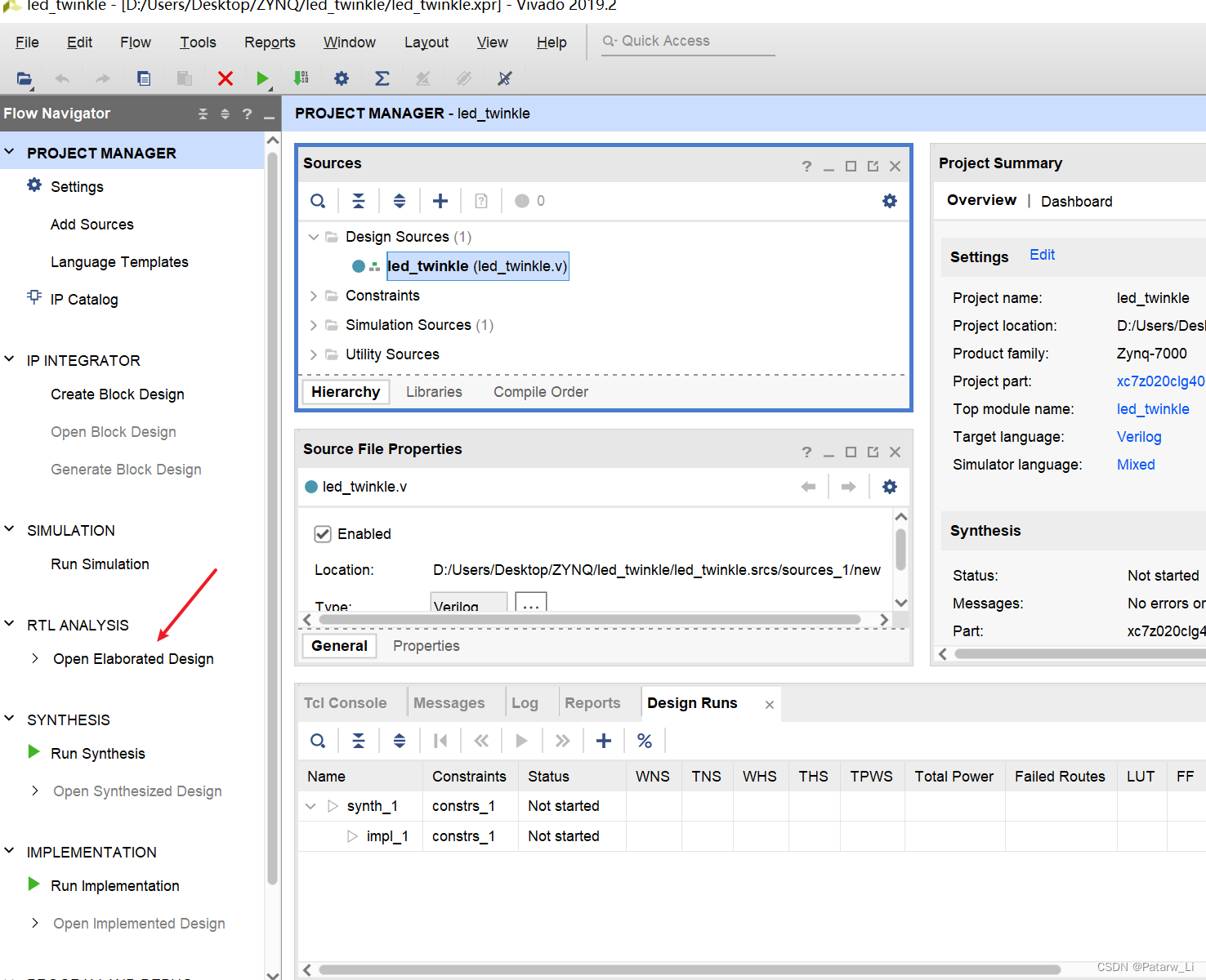

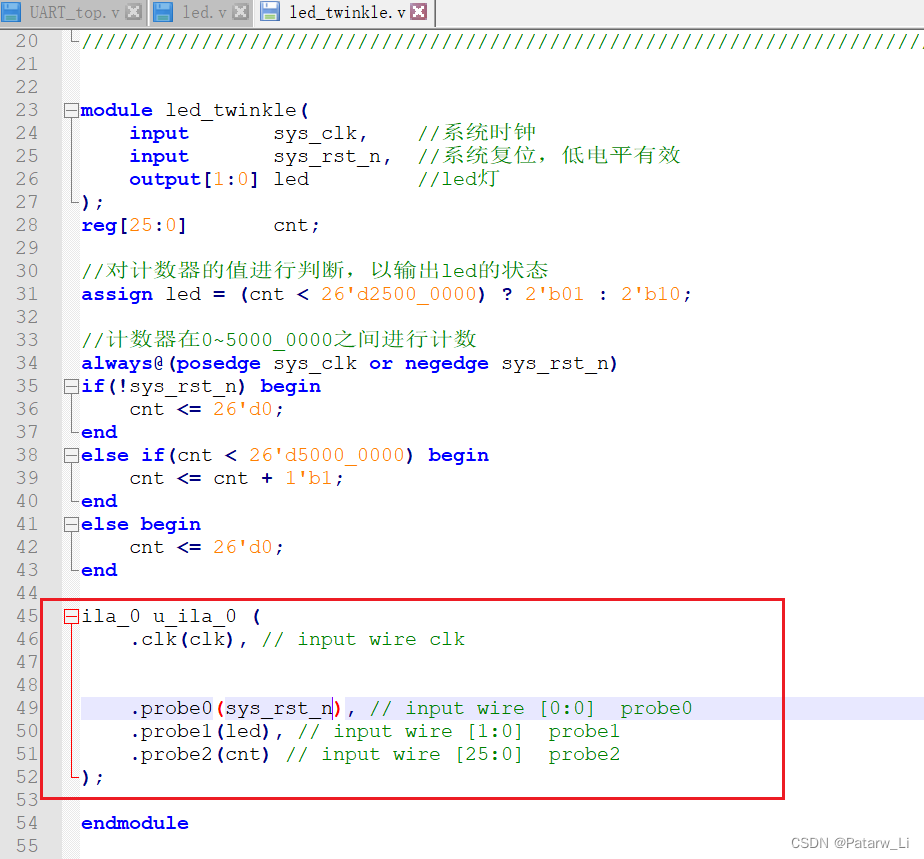

点击生成的.v文件,编写verilog代码:

`timescale 1ns / 1ps

module led_twinkle(

input sys_clk, //系统时钟

input sys_rst_n, //系统复位,低电平有效

output[1:0] led //led灯

);

reg[25:0] cnt;

//对计数器的值进行判断,以输出led的状态

assign led = (cnt < 26'd2500_0000) ? 2'b01 : 2'b10;

//计数器在0~5000_0000之间进行计数

always@(posedge sys_clk or negedge sys_rst_n)

if(!sys_rst_n) begin

cnt <= 26'd0;

end

else if(cnt < 26'd5000_0000) begin

cnt <= cnt + 1'b1;

end

else begin

cnt <= 26'd0;

end

endmodule添加引脚约束:

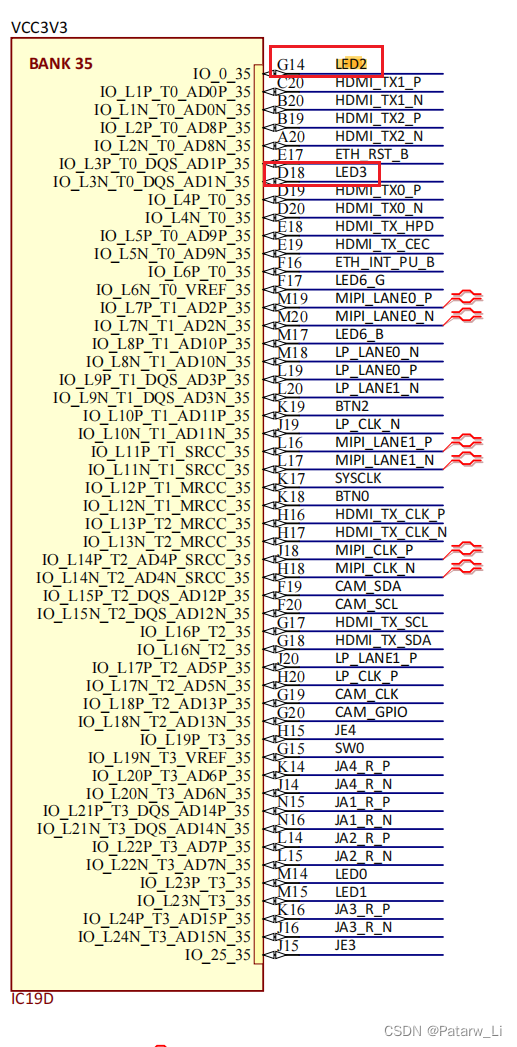

led2、led3引脚如下:

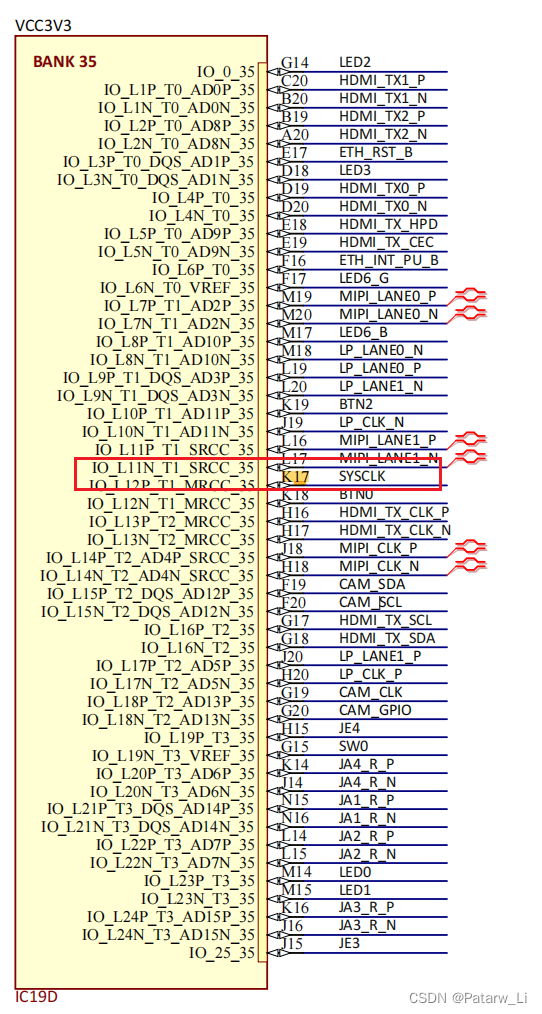

系统时钟引脚如下:

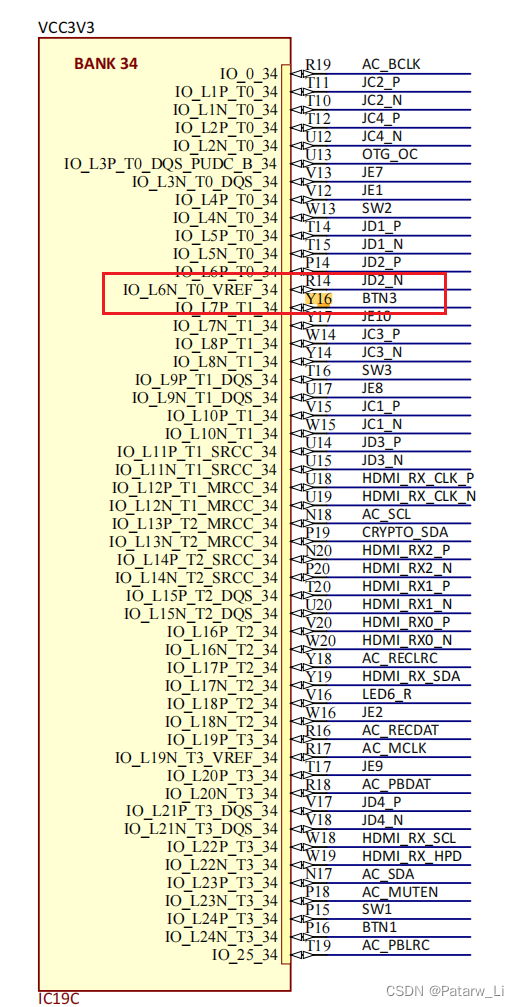

选择BTN3作为复位按钮:

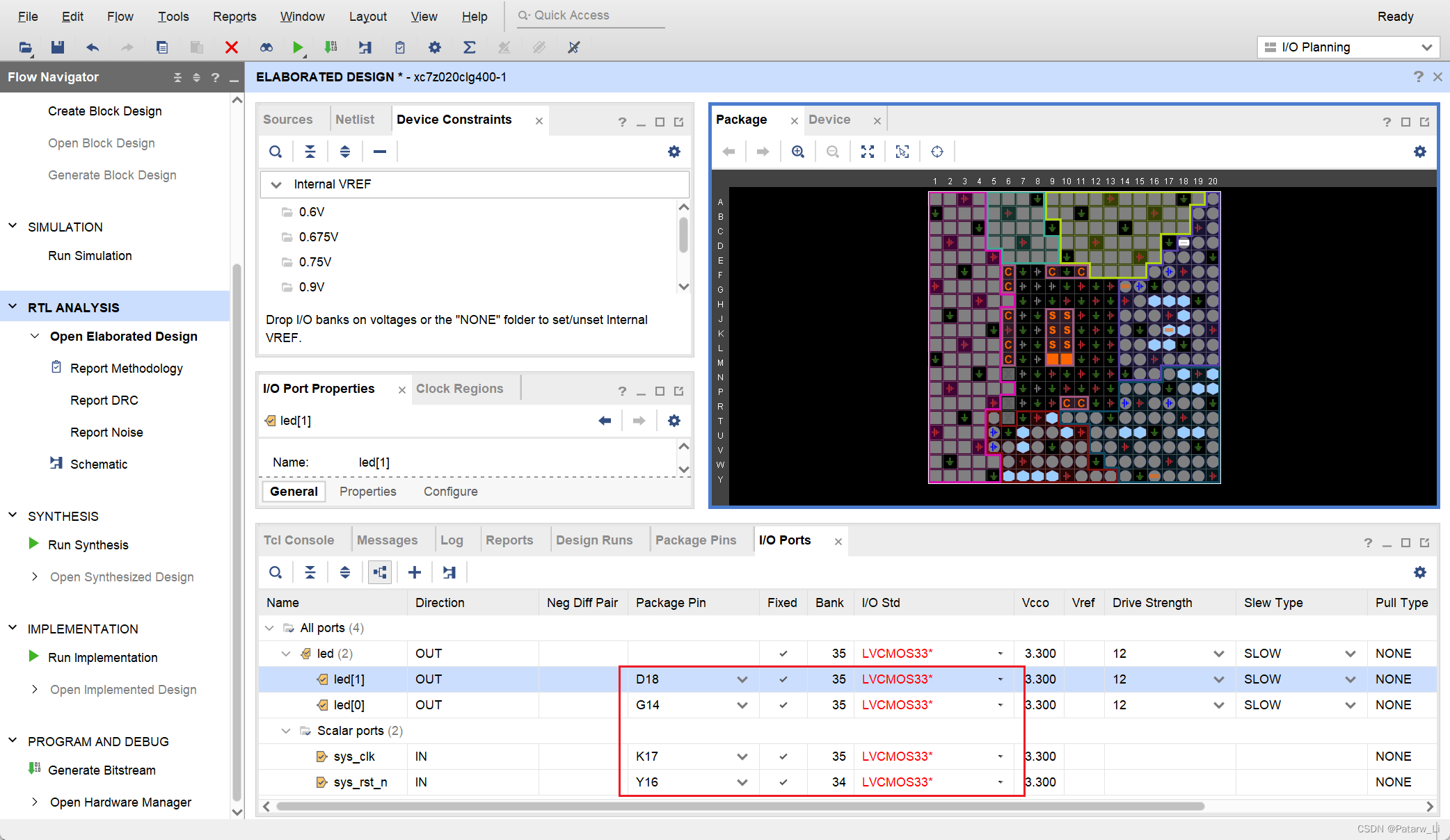

引脚配置如下,按ctrl+s保存配置:

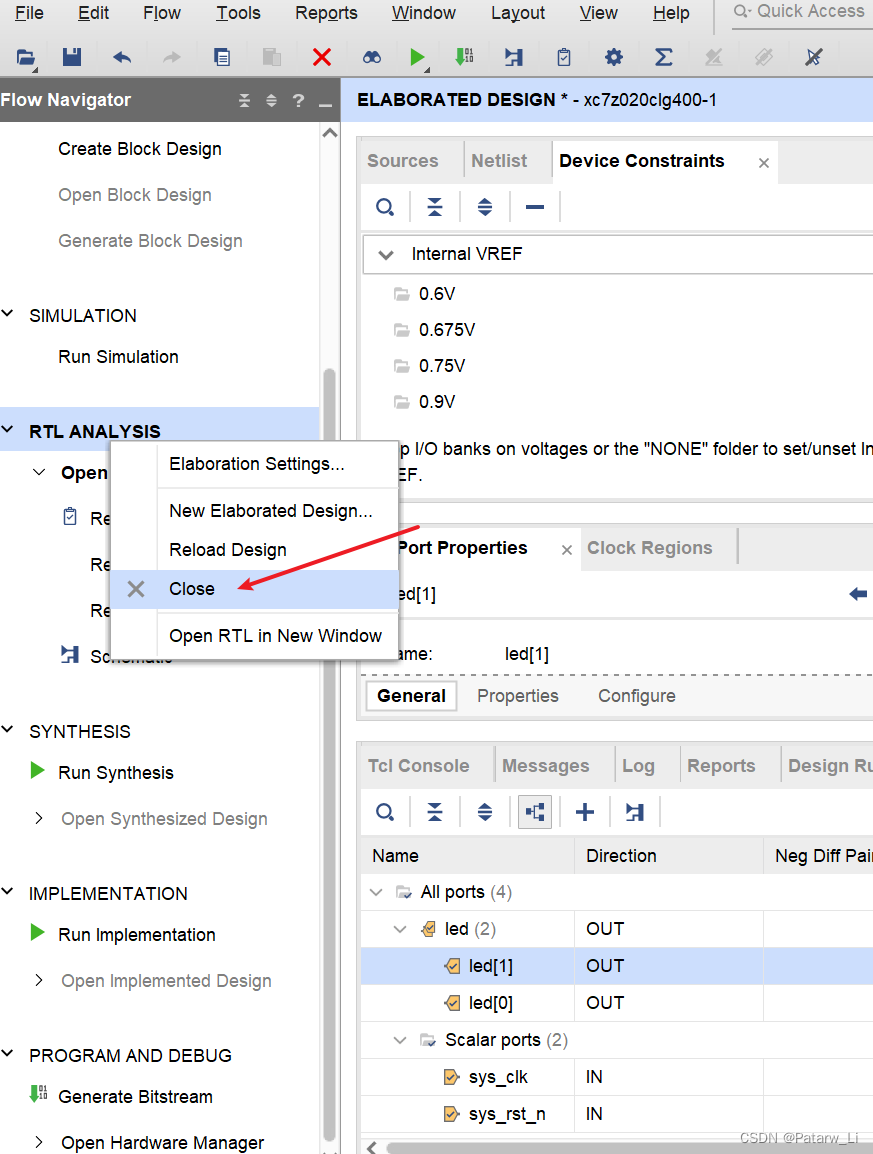

关闭引脚配置页面:

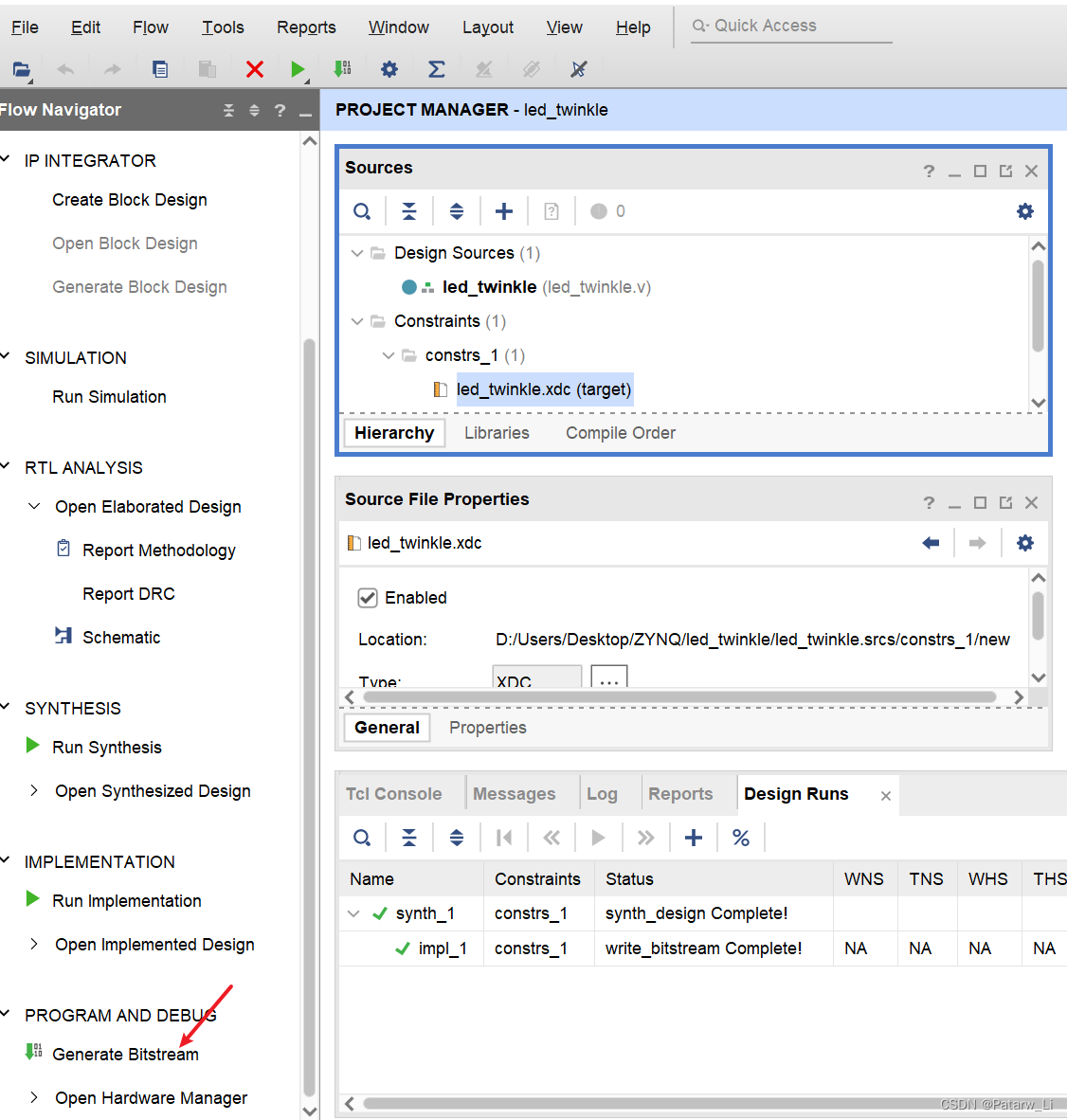

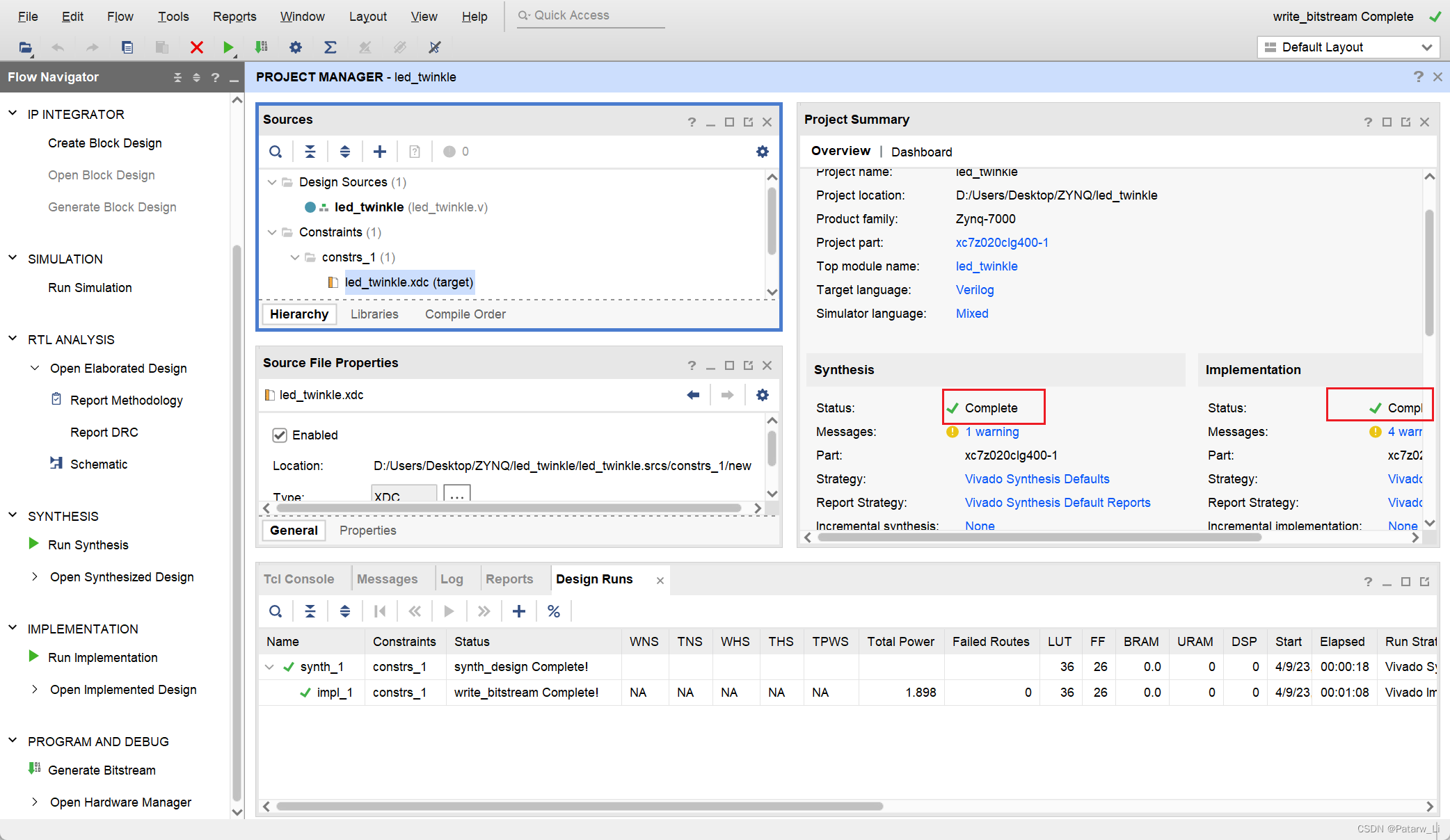

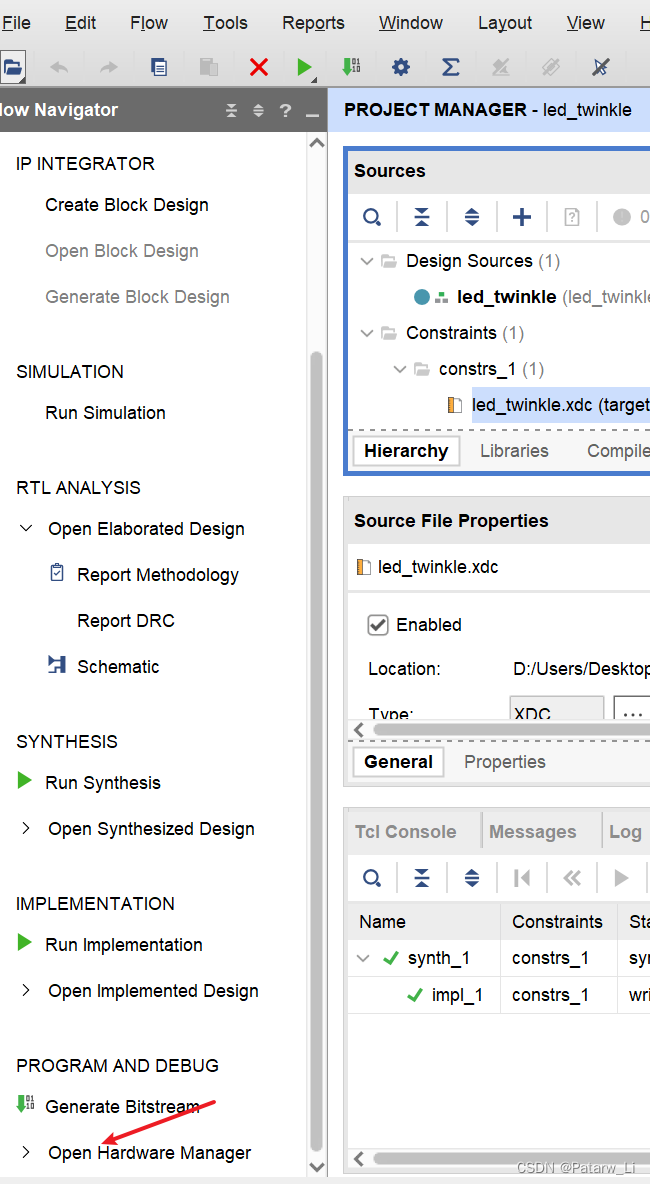

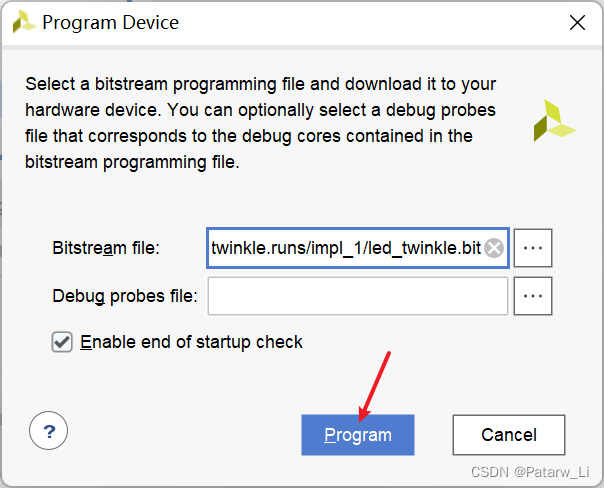

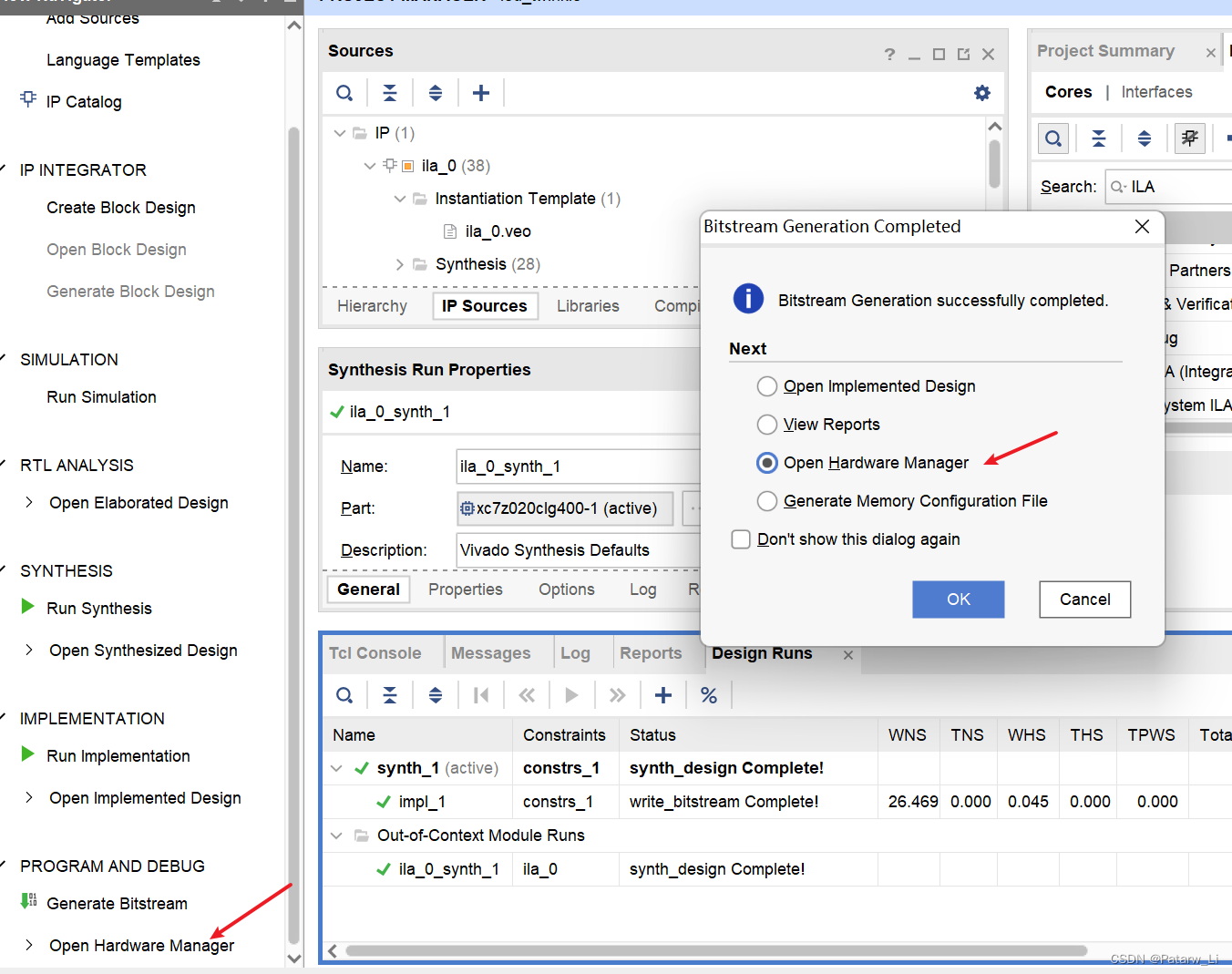

生成和下载比特流:

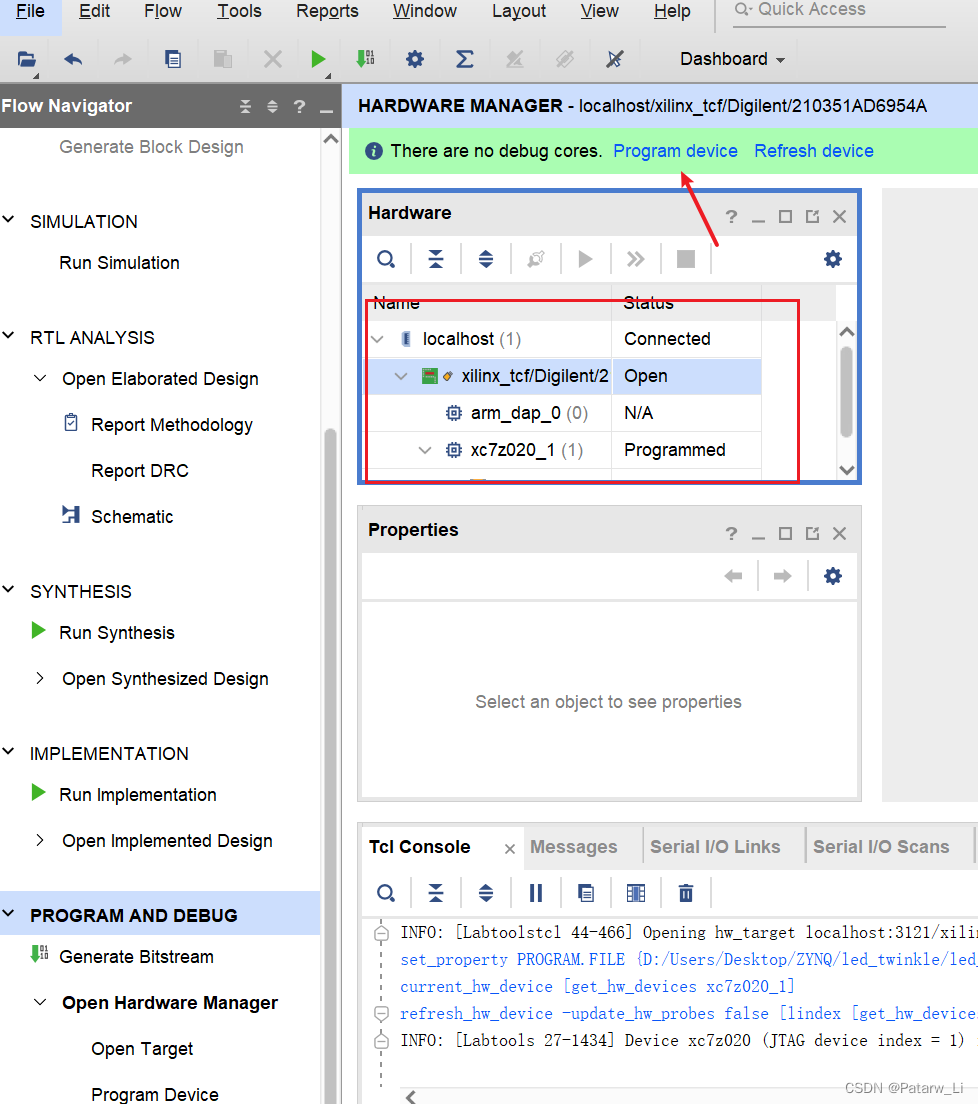

最后打开硬件管理:

此时已经把代码烧录进板子里面,按下复位按钮即可看到led2和led3交替闪烁。

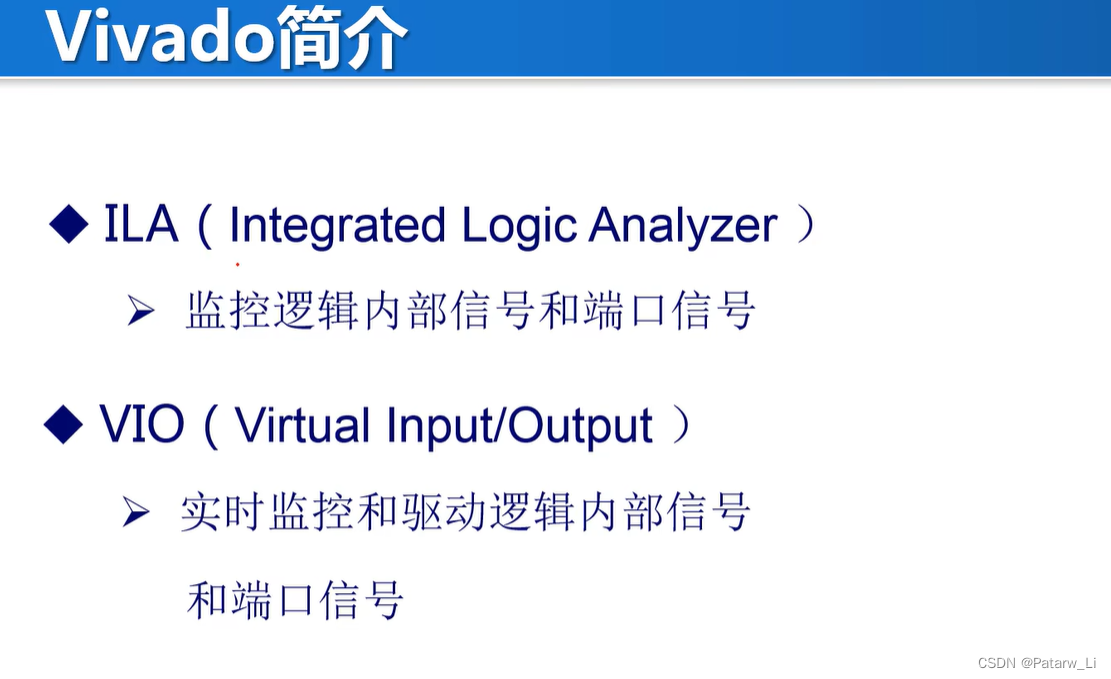

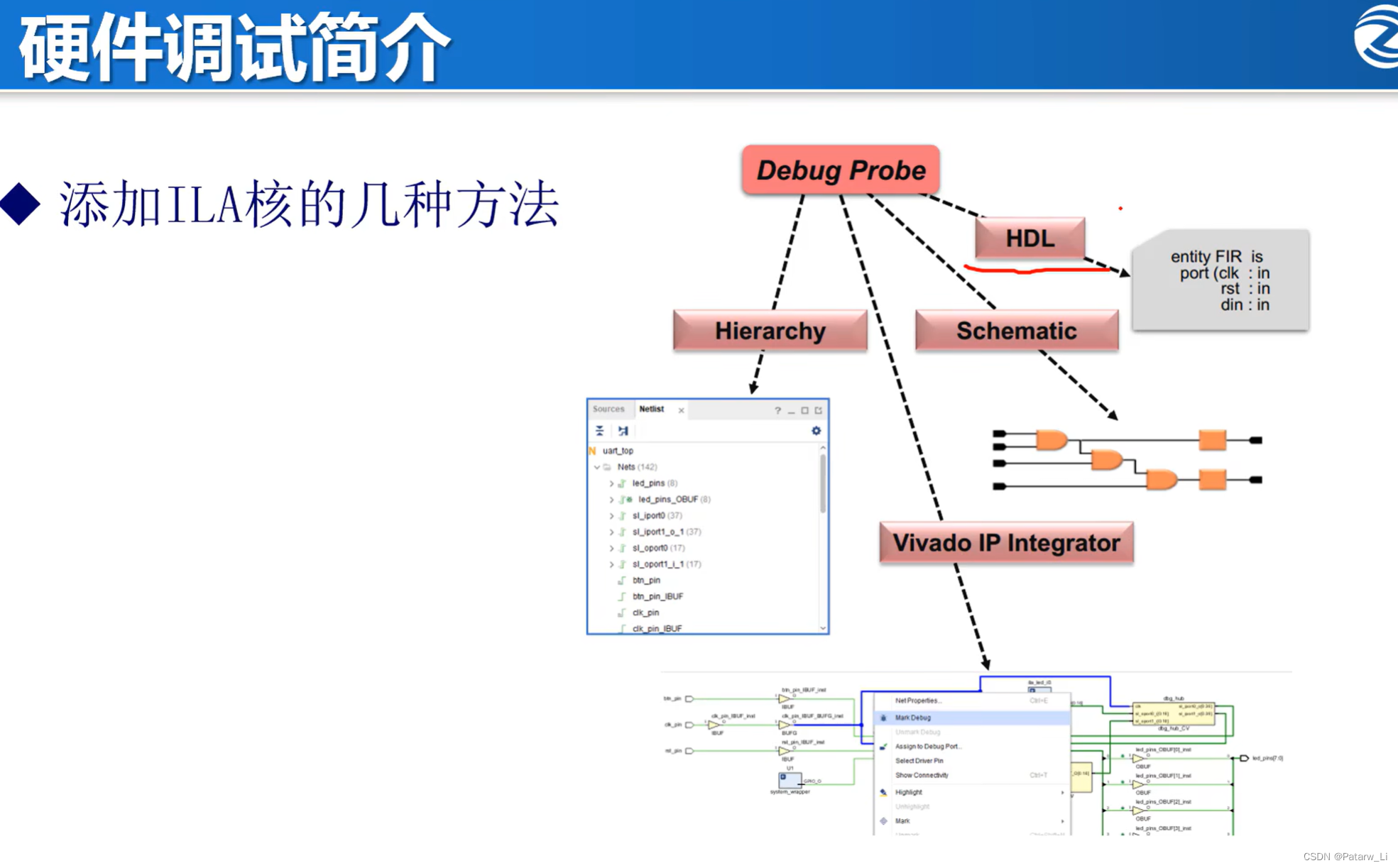

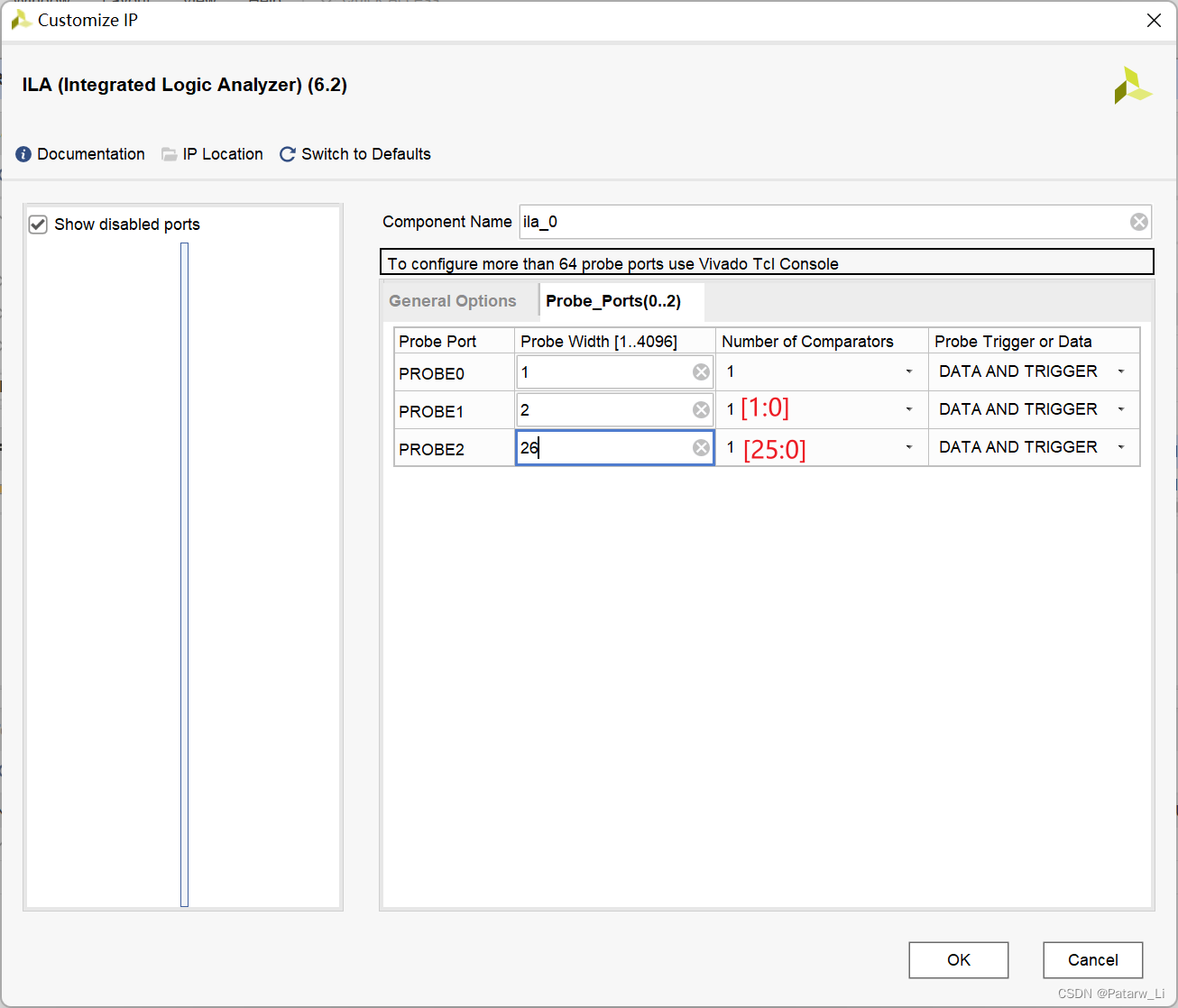

三、硬件调试,ILA的使用

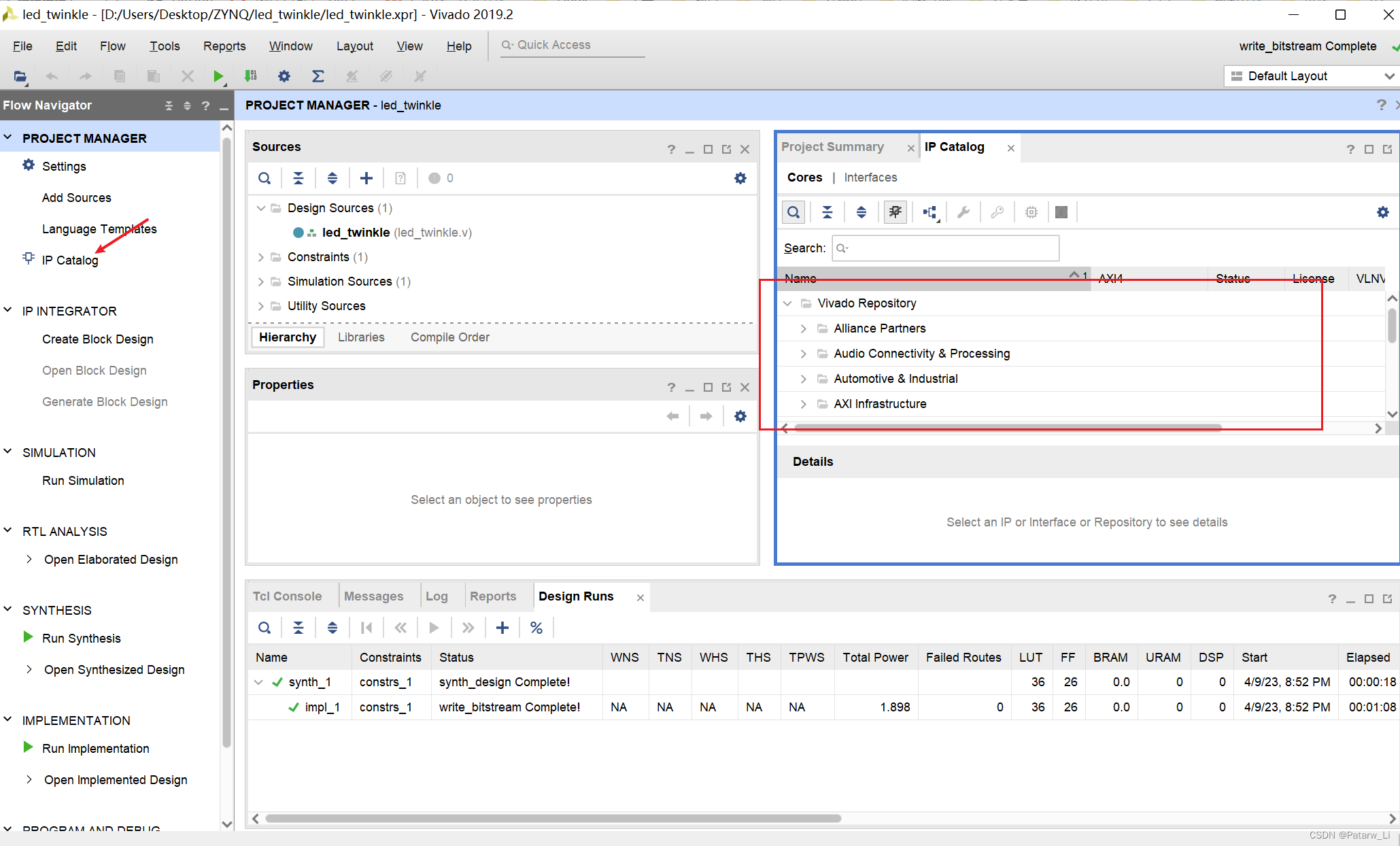

找到对应IP核:

找到对应IP核:

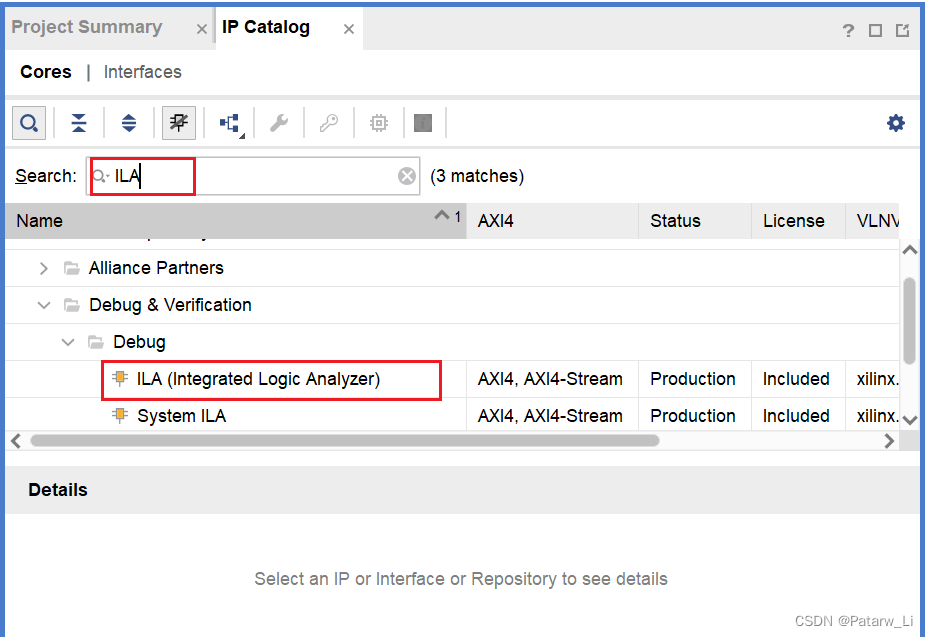

搜索ILA:

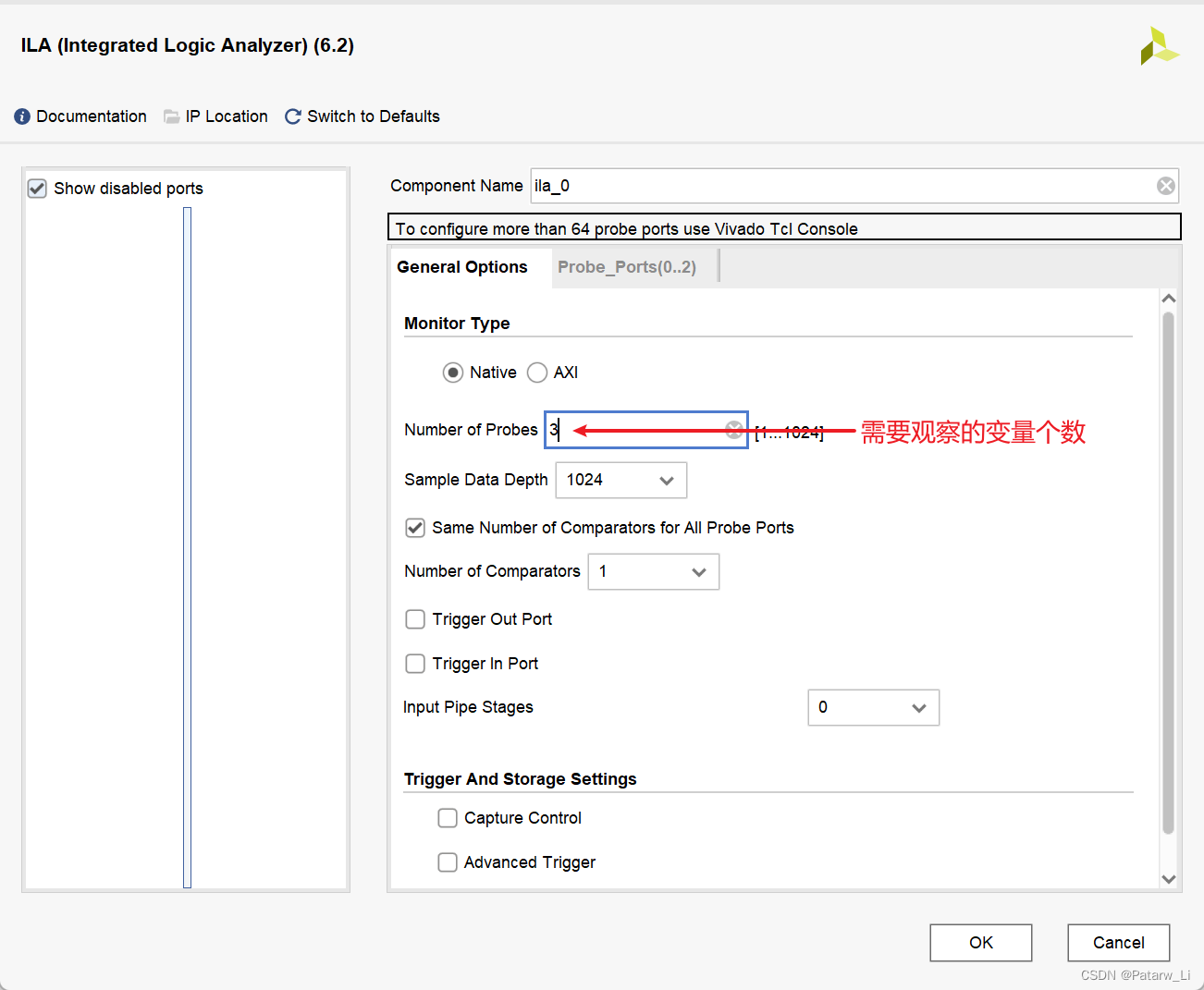

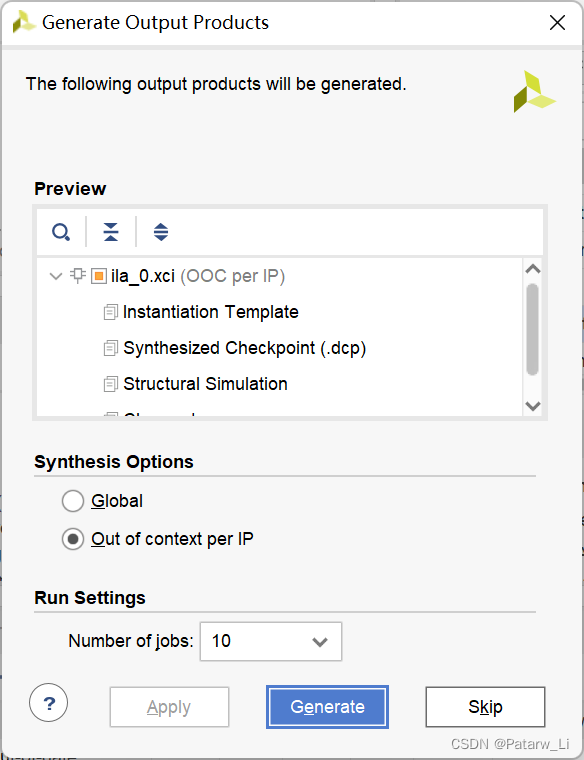

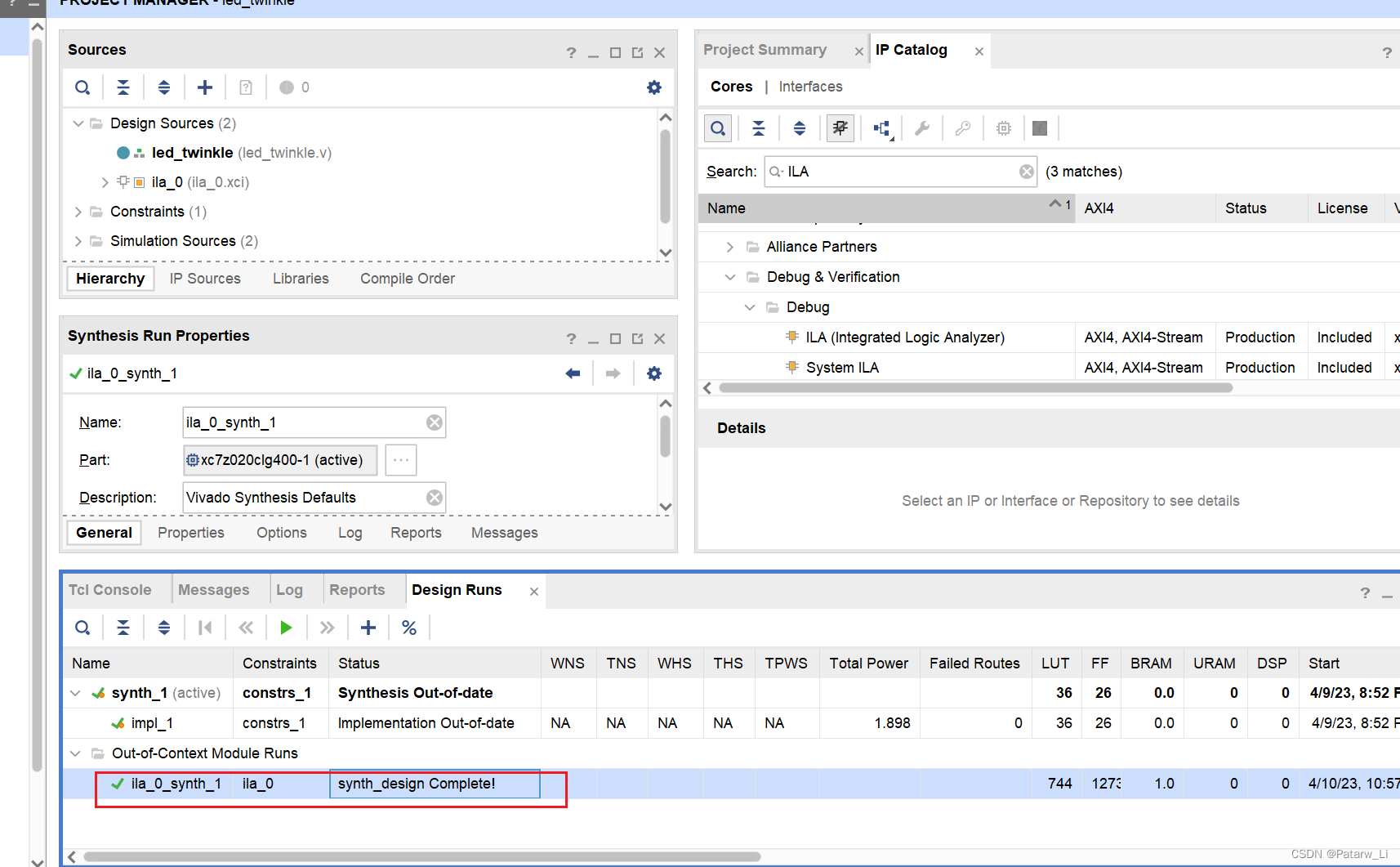

出现如下所示即为成功生成了IP核:

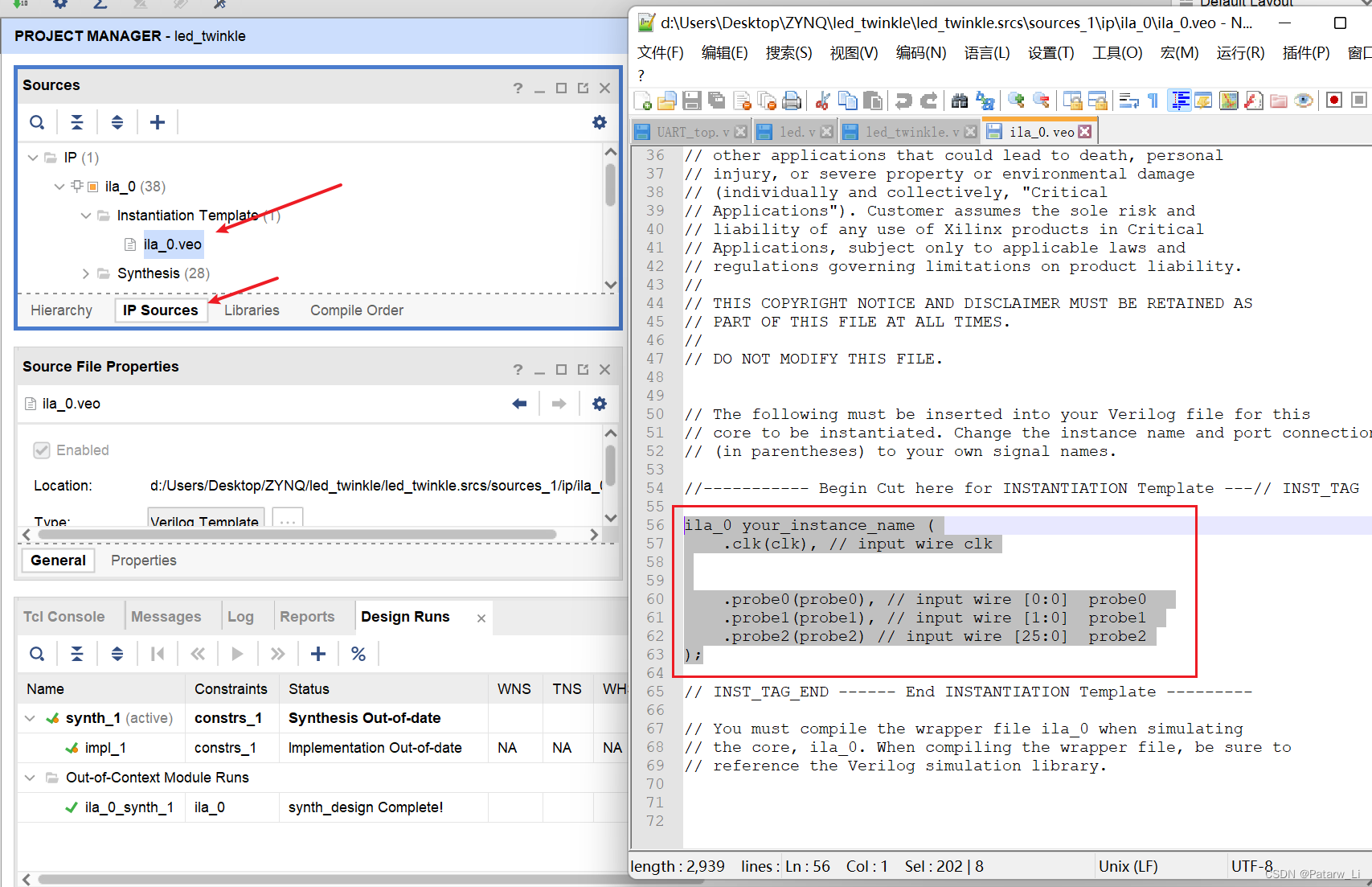

选择例化模板,复制到之前的led文件里面:

选择例化模板,复制到之前的led文件里面:

然后生成比特流,生成完会显示如下窗口,点击打开硬件管理:

2053

2053

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?