提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

文章目录

前言

简单差动放大器实验

本实验包括对简单差动放大器进行DC扫描、AC分析,并学习根据输出波形确定相位裕度、输入输出共模范围、共模增益、共模抑制比(CMRR)以及电源抑制比(PSRR)。

提示:以下是本篇文章正文内容,下面案例可供参考

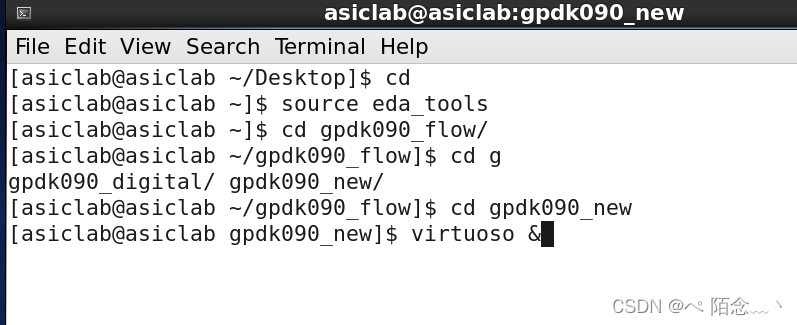

1.启动cadence

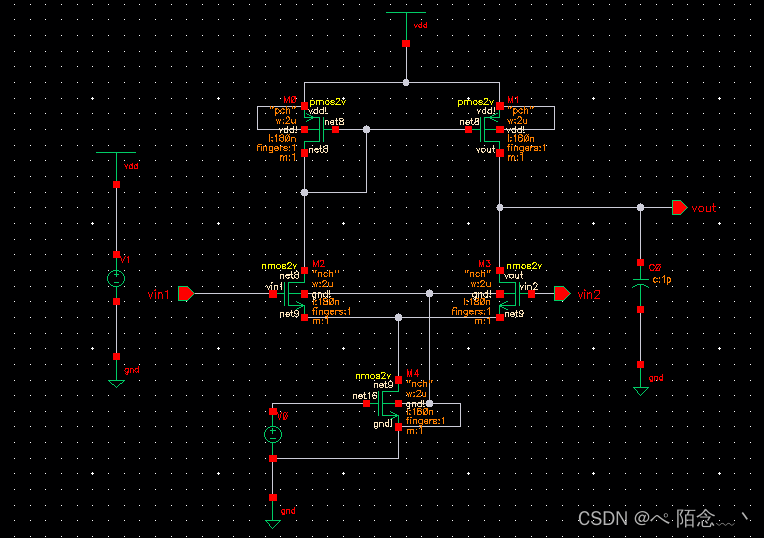

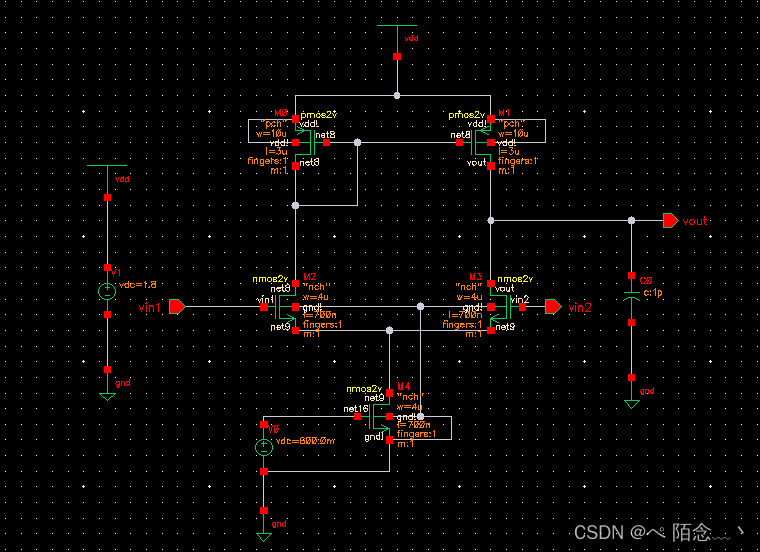

2.电路图输入

按下图输入简单差动放大器电路图,其中的元件参数我们在下一步中设置,图中用到的元件(vdc, pmos4,nmos4,vdd,gnd,cap)都在analogLib库中能找到。

3.计算、设置元件参数

根据放大倍数,功耗,输出摆幅等要求确定各个mos管的宽长比(W/L)和栅压。由于我们实验时间有限,请同学们直接按下面的步骤设置好元件值(选中元件后按q键调出如下的元件属性设置框):

M0,M1,M2:于Model name 栏输入n18,于Width栏输入4u,于Lenth栏输入700n,最后点击ok。

M3,M4:于Model name 栏输入p18,于Width栏输入10u,于Lenth栏输入3u,最后点击ok。

直流电压源V0,V1的值分别设为1.8,0.6。设置完毕后点击工具栏上的进行保存。

4.仿真

4.1 DC扫描及输入输出共模范围

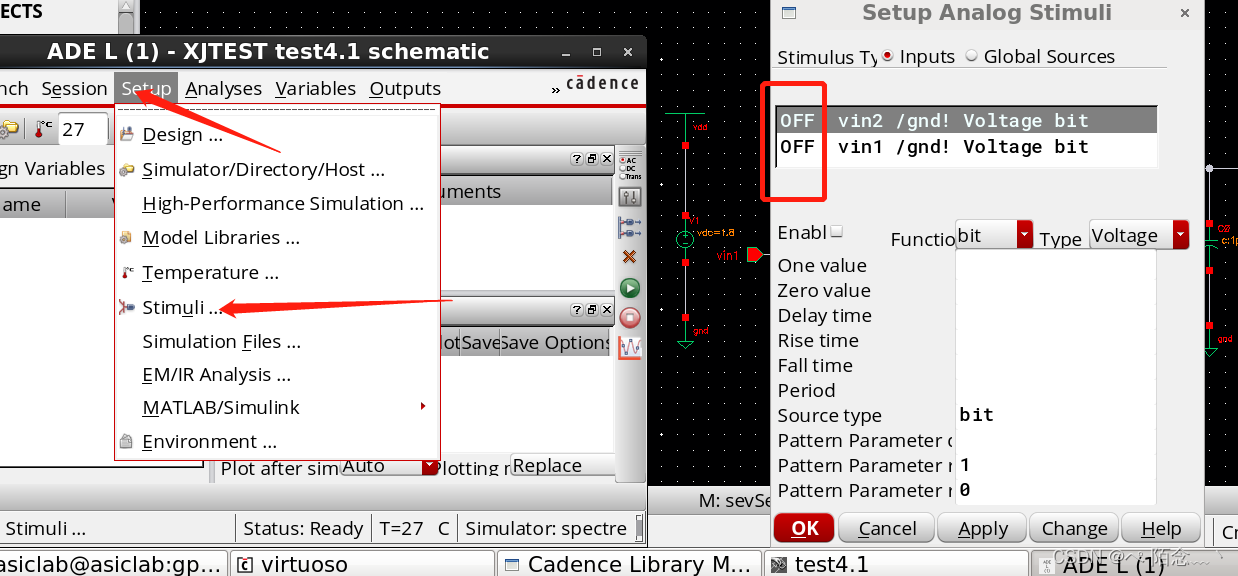

在菜单栏依次选择Tools→Analog Environment,弹出如图4.1所示的Simulation窗口:

点击Setup→Model Libraries在弹出的对话框中设好Model Library。点击Browse…按钮,选择/cad/smic018_tech/Process_technology/Mixed-Signal/SPICE_Model/ms018_v1p6_spe.lib,在Section(opt.)中填入tt,点Add,再点ok退出。

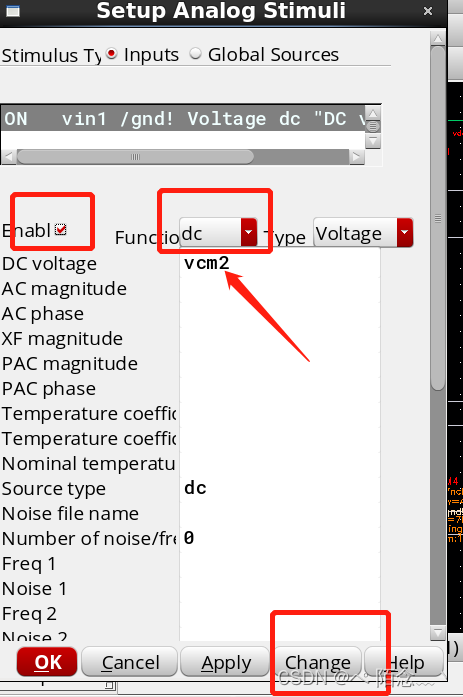

点击Setup→Stimuli,弹出如下图所示对话框,在其中可以设置输入信号。我们可以看到VIN1和VIN2前面有“OFF”字样,表示此时它们都不起作用。

选中VIN1,此时该行处于高亮状态。点击Enabled后的方框,当其变为黑色时表示已经选中,然后在DC voltage栏输入VCM1,最后点击Change保存修改(这一步一定要做!)。以同样的方法修改VIN2,不同的是在DC voltage栏输入VCM2。此时VIN1和VIN2前面的“OFF”应该变成了“ON”,表示它们都被激活了。最后点击OK退出。

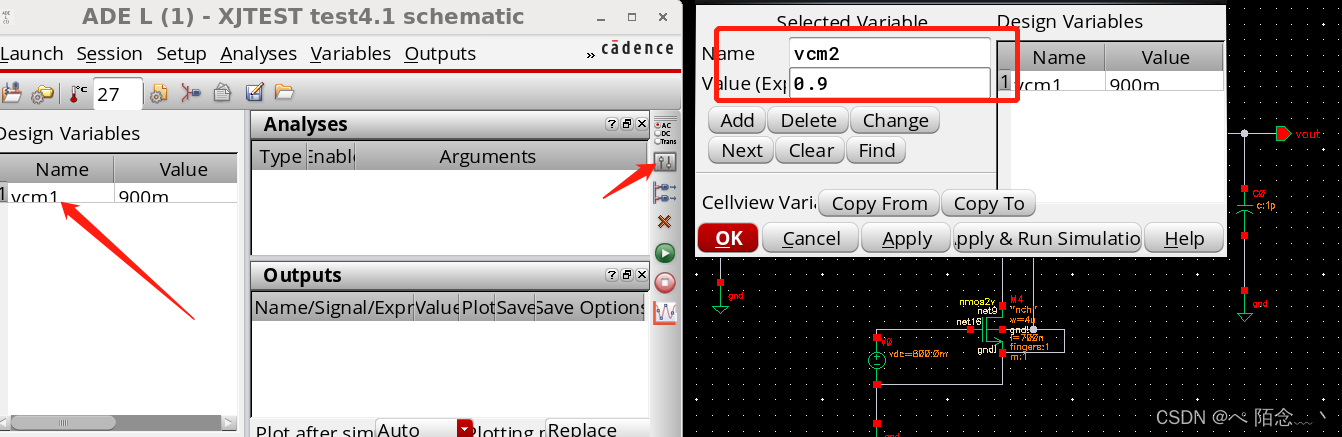

点击右边工具栏上的,将VCM1,VCM2添加为设计变量,值设为0.9。点ok保存。

设置直流扫描参数,点击右边工具栏上的,按图4.7设置好,点ok保存。这里我们让VCM1从0v扫描到1.8V。

设置输出信号,依次选择Outputs→To Be Plotted→Select On Schematic。

点击电路图中的VOUT PIN,然后按ESC。我们可以看到Outputs栏里已经有了刚才选择的VOUT。

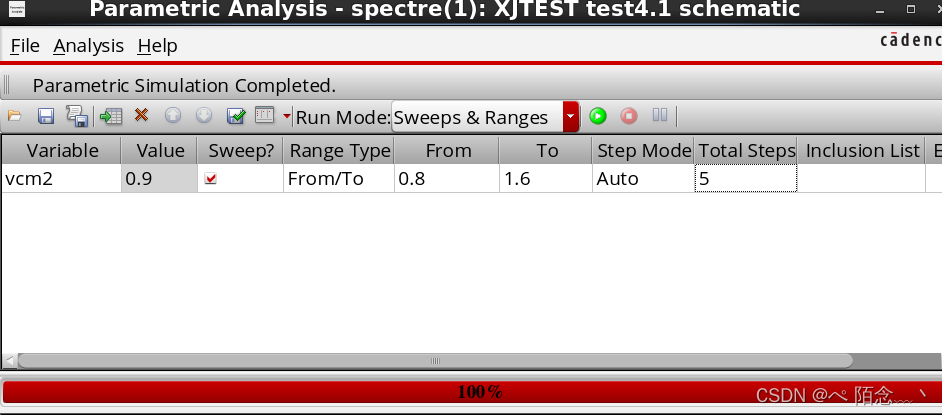

依次点击Simulation窗口的Tools→Parametric Analysis弹出参数分析窗口,按图4.10设置好:

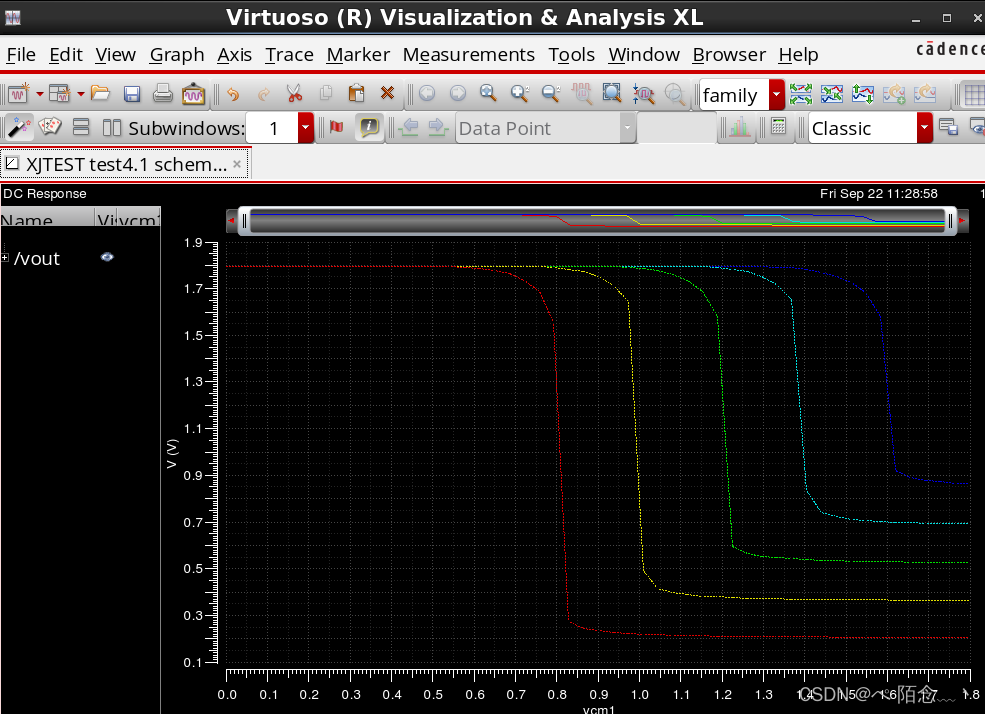

依次点击参数分析窗口的Analysis→Start,可以看到如图4.11所示的结果:

为使电路正常工作,输入共模电压的范围应为:

VGS1+( VGS0- VTH0)≦Vin,CM≦VDD-(VGS3- VTH3)+ VTH1 (1.1)

输出共模范围应为:

VOD0+VOD1≦Vout,CM≦VDD-|VOD3| (1.2)

本实验中最小输入共模电压为0.8V左右,小于 0.8V的输入共模电平会使M0进入线性区,M1,M2进入亚阈值导通状态;最大输入共模电压为1.4V左右,大于该值的输入共模电压很容易使M1,M2进入线性区。从图4.11中我们可以观察到随着VCM2的增大,输出摆幅越来越小。

4.2 AC分析,观察相位裕度

点击Setup→Stimuli,将VIN1的AC magnitude为0.5,将VIN2的AC magnitudee设置为-0.5(别忘了点Change保存修改!)。

设置交流分析参数,频率范围从10到200M,点ok 保存

点击观察输出波形:

依次点击波形显视窗的Tools→Calculator,弹出如图4.16所示窗口,在Caculator窗口的函数列表窗里选择PhaseMargin,然后点击就可以得到相位裕度。

4.3 共模增益,共模抑制比(CMRR)

回到Simulation窗口,点击Setup→Stimuli,将VIN1,VIN2的AC magnitude都设为1。

点击开始仿真,得到如下波形图:

从图4.17我们可以看到,即使电路是完全对称的,输出信号也会因为输入共模变化而变差,这个缺点在全差动电路中不存在。为了合理地比较各种差动电路,必须用所需要的差动增益与不希望的共模增益的比值来衡量对共模扰动的抑制能力。定义“共模抑制比”(CMRR)如下:

CMRR= (1.3)

本实验中,低频时ACM大约为0.035,ADM大约为185,因此CMRR大约为75dB。

4.4 电源抑制比(PSRR)

回到电路图编辑窗口,将V0的AC Magnitude设为1,点击ok退出。

之后点击保存电路图。

回到Simulation窗口,点击Setup→Stimuli,将VIN1,VIN2的AC magnitude设为0。

点击开始仿真,结果如图4.21所示。

我们可以看到在低频时从VDD到VOUT的增益接近1。电源抑制比(PSRR)的定义为:从输入到输出的增益除以从电源到输出的增益。在低频时,PSRR为:

PSRR≈gmN(rop||roN) (1.4)

在本例中,PSRR就是差动放大器的低频增益。

1506

1506

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?