由于仿真FIFO需要时钟资源,故使用了前一篇文章中使用的PLL模块。

在仿真FIFO模块时,我使用了一个数据发生模块,参考的下面这篇文章中的源码

datagene.v (可以去链接网址下载源码)

数据发生模块的输入输出框图如下所示:

我在Modelsim中利用了该模块进行FIFO的仿真。若对FIFO的IP核不熟悉,可以参考官方文档:http://www.altera.com/literature/ug/ug_fifo.pdf

下面是具体仿真过程:

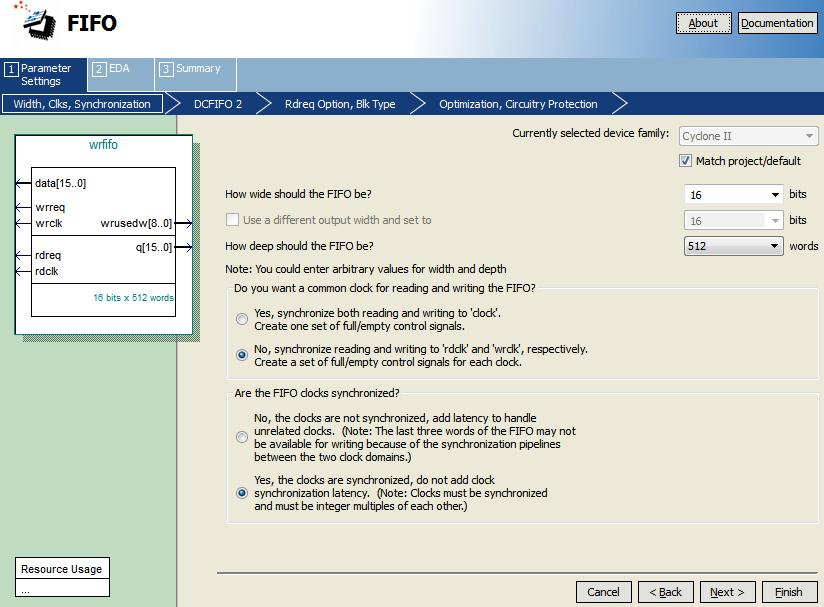

首先,看一下FIFO配置:

数据单元位宽:16

FIFO最大数据量:512个

读和写使用不同的时钟

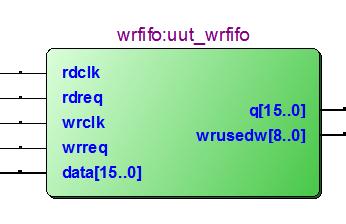

OK,下面给出FIFO模块的框图:

找到Quartus中生成的FIFO模块的 verilog文件,把它复制到Modelsim工程中;此外,FIFO仿真还需要的文件是:

- Altera库文件:altera_mf.v ,220_model.v (前一篇有提到这两个文件的位置)

- 数据发生器文件:datagene.v (参考特权同学的博客,里面可以下载到)

本文介绍如何在ModelSim中仿真FIFO,包括配置FIFO参数,使用PLL模块,数据发生器,以及详细解析FIFO的写入和读取时序。通过波形图分析了FIFO在不同时钟下的工作情况,展示了数据从写入到读出的过程。

本文介绍如何在ModelSim中仿真FIFO,包括配置FIFO参数,使用PLL模块,数据发生器,以及详细解析FIFO的写入和读取时序。通过波形图分析了FIFO在不同时钟下的工作情况,展示了数据从写入到读出的过程。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5863

5863

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?