随着现代电子技术的发展,数字电子时钟在家庭,车站,医院,办公等各个场所有着广泛的应用,成为人们生活的必需品,由于生产工艺上的进步大大降低了现场可编程门阵列(FPGA)的成本,使其成为目前设计数字电路的首选器件之一[1]。电子时钟的精度远远大于老式钟表,而且在钟表的报时能功能的基础上不断发展,诸如自动定时报警装置,定时广播,闹钟设置,甚至各种大型医疗设备的定时启用,智能仪表,机器人,所有这些都是在数字钟表的基础上实现,为其他电路的设计提供一定借鉴作用[1]。因此对简单数字钟的研究有极大的意义。

1.软件与verilogHDL介绍1.1软件引入

Altera® Quartus® II设计软件是适合单芯片可编程系统(SOPC)的最全面的设计环境[2]。建立工程项目和verilog HDL文件设计之后,可以使用 Quartus II 软件中的 Settings 对话框、Assignment Editor 和 Floorplan Editor 指定初始设计约束条件,例如,引脚分配、器件选项和时序约束条件[2]。Quartus II还提供Compiler Settings 向导(Assignments 菜单)协助用户指定初始设计的约束条件。

ModelSim仿真工具是Model公司开发的,它支持Verilog、VHDL以及他们的混合仿真,它可以将整个程序分步执行,使设计者直接看到程序下一步将要执行的语句,而且在程序执行的任何步骤任何时刻都可以查看任意变量的当前值。可以在Dataflow窗口观察某一单元或模块的输入输出连续变化等,比Quartus 自带的仿真功能强大的多,支持Testbench,是目前业界最通用的仿真器之一[2]。

1.2语言介绍

Verilog语言形式简单,与C语言相近,容易掌握,在门级开关电路描述方面比VHDL强的多[3]。相比传统电路原理图输入法,verilogHDL设计周期短,无需专门的设计工具即可很轻松的将完成的设计移植到不同厂家的不同芯片中去[3],并在不同规模应用时比较方便的作修改调整。由于verilog HDL的信号位数是很容易改变的,故可对它进行修改来适应不同的规模你应用[4]。且在仿真验证时,仿真测试文件可采用同一种描述语言来对设计电路进行测试。Verilog HDL 程序是由模块构成的,每个模块的内容都是嵌在module和endmodule两个语句之间,每个verilog程序包括四个主要部分:端口定义,I/O说明,内部信号声明,功能定义。每个模块实现特定的功能,模块是可以进行层次嵌套的。正因为如此,才可以将大型的数字电路设计分割成不同的小模块来实现特定的功能,最后通过顶层模块调用子模块来实现整体功能[4]。

2.数字钟的设计方案及原理2.1设计方案

本文以FPGA为实验平台,采用VerilogHDL语言在Quartus II 11.0开发环境下设计数字时钟[5-6],具有计时,校时,整点报时的功能,具体功能为:1)能够对小时、分钟、秒钟进行正常计时,每日按24小时计时制,能用四个七段式数码管清晰显示时和分,八个LED采用二进制形式来显示秒钟。2)具有复位功能,按下reset键可以对当前时间清零。3)校验功能,能够对数字钟进行分时设置,方便在时钟跑错时进行校正。4)整点报时功能,当为12:00时和00:00时,蜂鸣器以1Hz的频率响起12下,报整点功能实现。

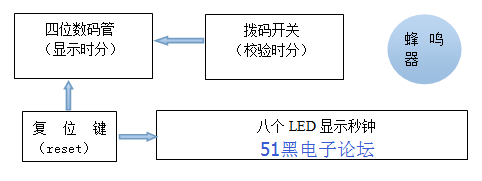

数字钟的硬件框图如图1所示。

图1 数字钟的硬件框图

2.2设计原理2.2.1数字钟组成框图

数字时钟组成框图如图2所示。可见,它由2个60进制计数器、1个24进制计数器和2个2选1数据选择器共5个模块组成。3个计数器共用一个时钟信号CP,CP是50M系统时钟分频后的1Hz信号。在时和分的输出端接上译码电路,用四个共阳极的七段数码管显示出时间[7] ,秒的输出用8个LED的二进制形式来表示。两个选择器分别选择时计数器和分计数器的使能控制信号,对时间进行校正时,在控制端(Adj_hour和Adj_min)的作用下,使能信号接高电平,此时每来一个时钟信号,计数器加1计数,从而实现对小时和分钟的校正[8]。正常计时时,使能信号来自于低位计数器的进位输出,即秒计数达到59s时,产生输出信号(Sco=1)使分计数器加1,分、秒计数器同时计时到最大值(59s 59min)时 ,产生输出信号(Mco=1)使小时计数器加1。

图2 数字钟组成框图(见51hei附件)

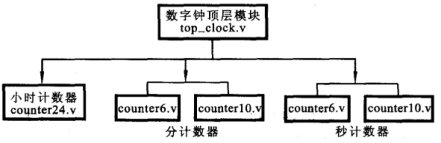

2.2.2数字钟层次结构图

数字时钟的层次结构图如图3所示。可以看出,整个程序分为两个层次4个模块,其结构层次如图2所示。底层由3个模块组成,6进制计数器模块(counter6.v)、10进制计数模(counter10.v)和24进制计数模块(counter24.v),顶层有一个模块(top_clock.v),它调用底层的3个模块完成数字钟的计时功能。

图3数字钟程序的层次结构图

3.核心模块设计3.1顶层模块

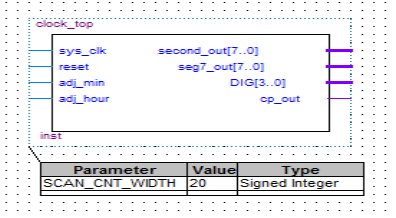

建立数字时钟工程new project clock,设计顶层模块top_clock.v,顶层模块包括1Hz分频电路、整点报时电路、数码管动态扫描(移位、选择)、译码、显示电路。其顶层框图如图4所示。

图4 数字钟顶层框图

(1)生成1Hz时钟信号模块

时分秒计数器的计时时钟cp为1Hz的信号,而系统时钟信号(sys_clk)为50MHz,因此需要对50MHz信号进行分频得到1Hz。具体分频的代码为:

always@(posedge sys_clk or negedge reset) begin

if(~reset)begin

cnt<=0;cp<=0;

end else begin

if(cnt=25’d24999999)begin

cp<=~cp;cnt<=0;

end else begin

cnt<=cnt+1;

end

end

end

(2)整点报时模块

正常计数时,当分秒计数达到59分59秒,下一个时钟信号cp的上升沿到来时蜂鸣器以1Hz的频率发出蜂鸣实现整点报时,且N整点时,蜂鸣器就发出N声“嘀”响,13时及13时以后的每个整点,蜂鸣器发出(N-12)声“嘀”响。具体整点报时代码为:

assign hour_num=hour[7:4]*10+hour[3:0]+1;

always@(posedge cp or negedge reset)begin

if(~reset) bp_cnt_end<={5{1'b1}};

else if(hour_en)

bp_cnt_end<=((hour_num==24)?12:(hour_num>=13)?(hour_num-12):hour_num)-1;

end

always@(posedge cp or negedge reset)begin

if(~reset) bp_cnt<={5{1'b1}};

else if(hour_en) bp_cnt<=5'b0;

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

4887

4887

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?