LVPECL是ECL电平的正电源、低电压版本。

ECL指发射极耦合逻辑(Emitter Coupled Logic),与TTL相同,ECL的主体结构由三极管构成,不同的是,ECL内部的三极管工作于非饱和状态(即截止或放大状态),符合高速信号逻辑状态迅速变化的要求,极适宜于高速应用。非饱和状态的缺点在于,始终有电流流过三极管,因此功耗相对较大。从这点上来说,ECL速率的提升是以功耗的增大为代价的。

由于 ECL 电平需使用负电源,给电路设计带来了许多不便,在高速设计中,真正获得广泛应用的是其正电源、低电压版本LVPECL。

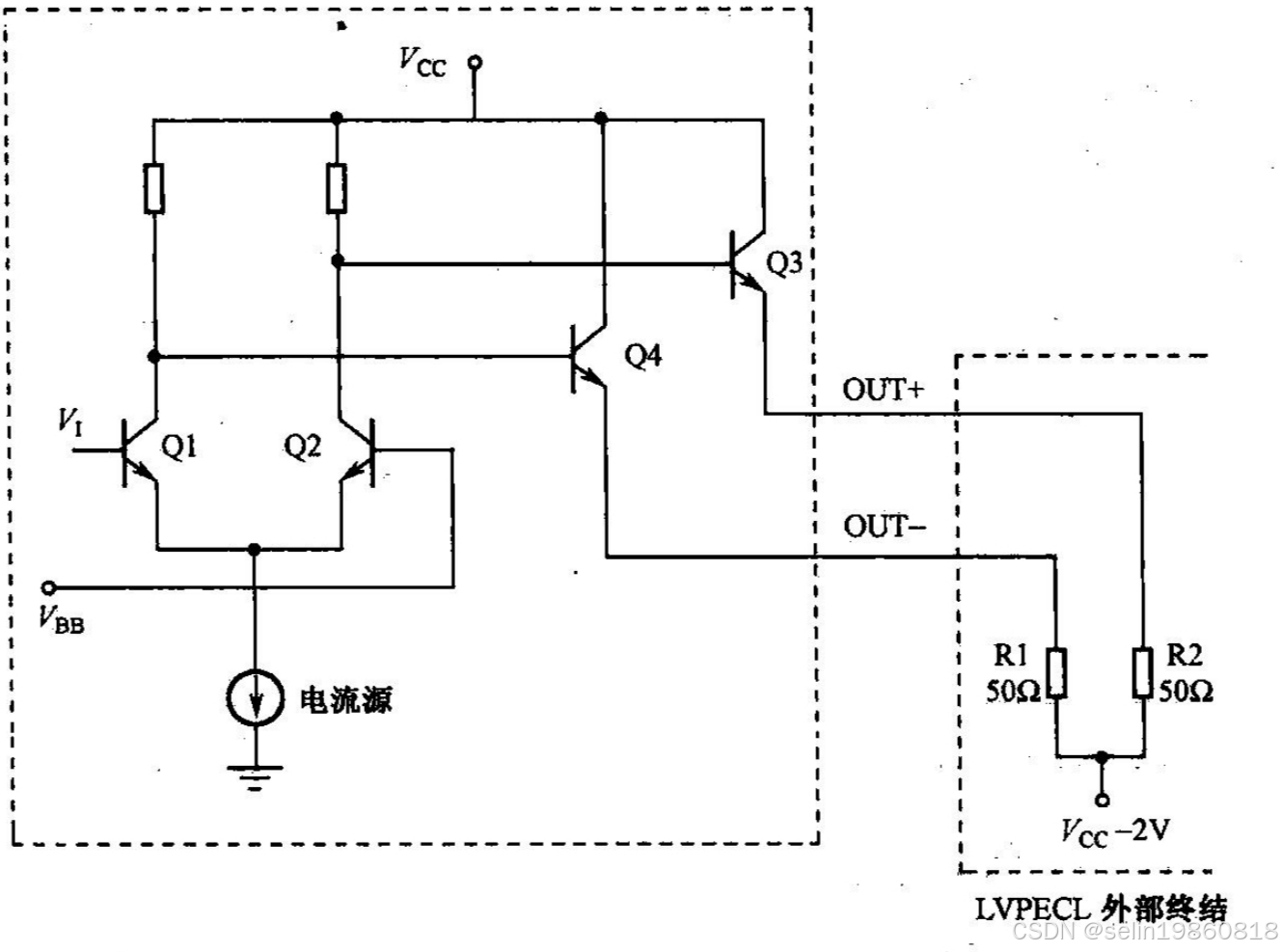

如下图所示,LVPECL输出端的关键部分是一对差动放大器Q1、Q2,以及一对射极输出器Q3、Q4,不仅拥有差分对信号抗干扰能力强的优势,还拥有射极输出器输出电阻小、驱动能力强的优点。

上图中,Vcc取值为3.3V或2.5V,VBB为内部参考电平。

基于差动放大器的特点,V1电平高于VBB时,Q1导通而Q2截止,在输出端,Q3导通而Q4截止,输出端输出逻辑1状态。

V1电平低于VBB时,Q1截止而Q2导通,在输出端,Q3截止而Q4导通,输出端输出逻辑0状态。

由于Q1和Q2是轮流导通的(即在任何一个时间段内,不是Q1就是Q2导通),Vcc和GND之间永远存在一条电流通路,这也是LVPECL功耗较大的原因。

LVPECL 属电流驱动型,OUT+和OUT-引脚通过 50电阻终结于Vcc-2V,输出电流14mA,因此 OUT+和 OUT-的共模电平值为 Vcc-1.3V,其计算方法是 Vcc-2V+14mA×50Ω=Vcc-1.3V。外部终结电平 Vcc-2V 和共模电平Vcc-1.3V,这两个参数对LVPECL匹配电路的设计至关重要,其具体应用将在高速电平互连一节讨论。

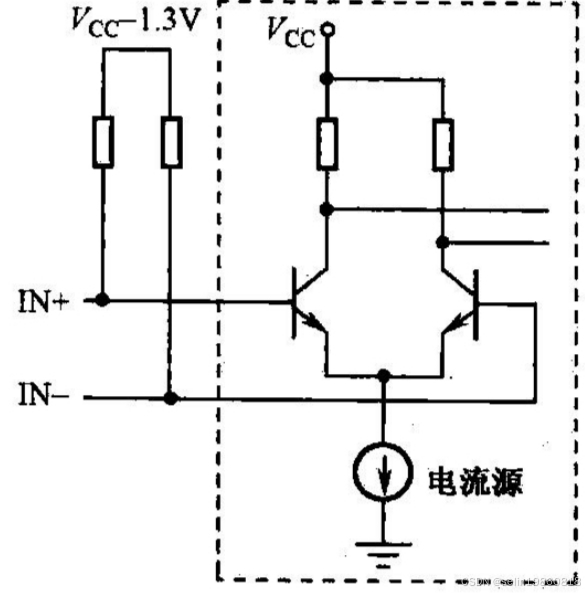

如下图所示,LVPECL的输入结构是一对高输入阻抗的差动放大器。由于输出信号的共模电平为Vcc-1.3V,输入信号应偏置到该电平上,以获得最大的动态范围。

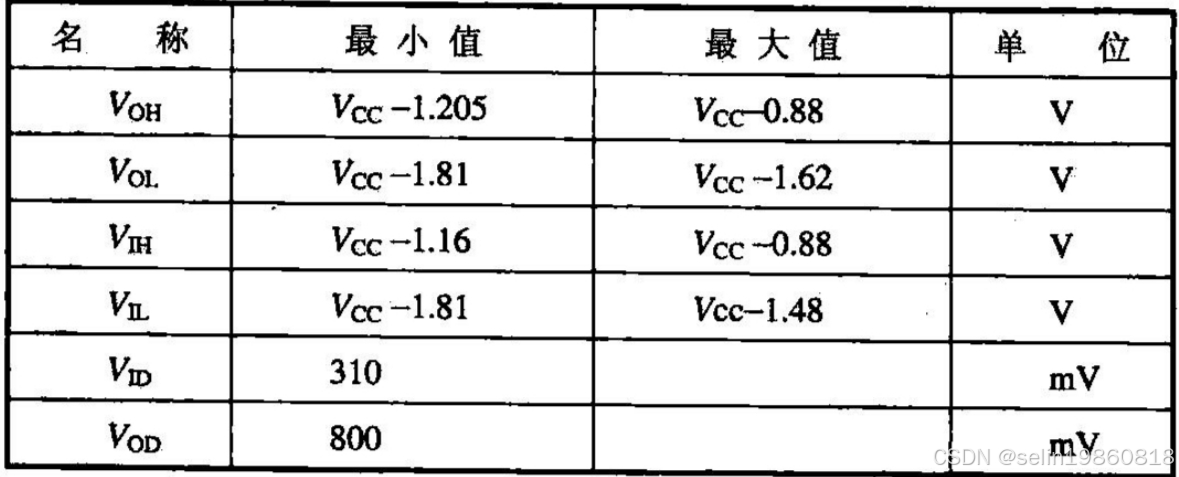

如下表所示,列出了某厂家LVPECL电平的输入/输出规格参数。对于LVPECL电平,国际标准组织尚未制定任何标准,因此不同厂家器件的参数并不一致,在应用中需仔细分析器件资料上的对应参数。

设计中,应重点关注LVPECL的以下特点:

(1)与 LVDS相比,LVPECL功耗更大,匹配电路的设计也更复杂,但支持更高的速率,抗抖动性能也更佳。在高速设计中,LVPECL常被用做高速时钟和数据的电平,如许多百兆或千兆PHY芯片的MDI(媒质相关接口)接口,以及许多PLL(锁相环)时钟信号都采用LVPECL电平。

(2)由于内部三极管工作于非饱和态,LVPECL的传输延时极小。

(3)由于始终存在一条 Vcc到GND的电流通路,因此LVPECL功耗较大,但LVPECL的功耗与工作速率基本无关。

(4)由于 LVPECL 采用电流驱动模式,电源 Vcc的作用只是提供电流通路和外部偏置电平,电源纹波对信号的影响相对较小。但当LVPECL 作为时钟信号的电平时,为防止电源纹波耦合到时钟信号上,仍应尽量提高电源的质量。

(5)LVPECL的外部端接电路较复杂。LVPECL的输出端需偏置到Vcc-2V,输入端需偏置到Vcc-1.3V,为减少电源种类,设计中往往通过分压电阻实现不同的偏置要求,以至于与LVDS、CML相比,LVPECL的外部电路显得尤为复杂。这些电路会造成高速信号线上的分叉,因此,LVPECL并不适用于要求极高的高速信号,如10Gbps以太网的MDI接口一般采用CML电平而不是LVPECL电平。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?