//参考高速电路设计实践

目录

一、LVPECL

1、基本原理

它是ECL电平的正电源、低电压版本。

ECL与TTL的比较:

ECL是指发射极耦合逻辑,主体有三极管构成(与TTL类似),不同点:工作在非饱和区(截止或放大状态),使得符合高速信号逻辑状态变化的要求,适用于高速应用。

ECL的缺点:始终有电流经过,功耗较大。速率的提升是以功耗增大为代价的。需要使用负电源,不方便。

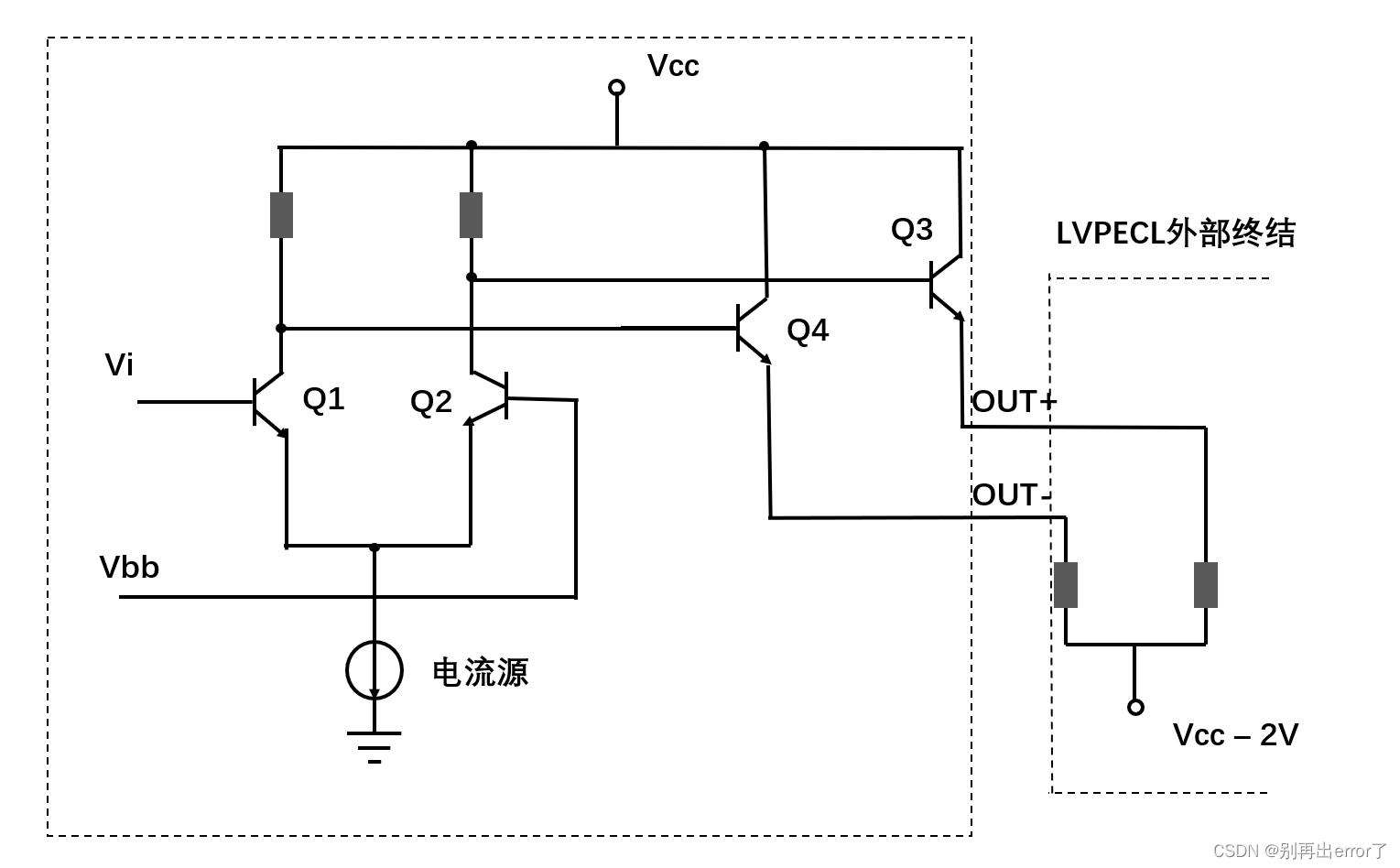

LVPECL:正电源,低电压,结构如图:

输出端有一对差动放大器Q1和Q2,以及一对射极输出器Q3、Q4。

差分对信号抗干扰能力强,射极输出器输出电阻小、驱动能力强。

原理:Vcc取值3.3V或2.5V,Vbb为内部参考电压

Vi高于Vbb时,Q1导通,Q2截止;在输出端,Q3导通,Q4截止,输出高电平,逻辑1;反之,逻辑0。

在两种情况下都存在一条电流通路从Vcc流向GND,使得功耗大。

2、特点

(1)与LVDS相比功耗更大,匹配电流更复杂,但支持更高频率,抗抖动性能也更好。常被用作高速时钟和数据的电平。

(2)三极管处于非饱和态,LVPECL的传输延时极小。

(3)存在一条电流通路从Vcc流向GND,使得功耗大,但功耗与工作速率基本无关。

(4)采用电源驱动模式。

(5)外部端接电路较复杂,输出端要偏置到Vcc-2V,输入端要偏置到Vcc-1.3V,设计中为减少电源种类常常利用分压来得到相对于电压值,导致结构十分复杂,不适于要求极高的高速信号。

二、CML

指电流模式逻辑(Current Mode Logic),它的输入输出端口的匹配已集成于片内,基本不用外部端接,应用简单。

在功耗上,CML低于LVPECL,极高速信号更适合匹配简单的CML;而LVPEL的优势在于抗干扰能力强,当需要有精度和抖动要求时,考虑LVPECL较多。

三、三种高速电平的比较:LVDS\LVPECL\CML

(1)驱动模式:都属于电流驱动,适用于高速电路设计。

(2)外部端接:CML最简单,其次是LVDS,需要增加一个100Ω的终结电阻,最复杂是LVPECL.

(3)功耗方面:LVDS差分摆幅最小,功耗最小;其次是CML,功耗略低于LVPECL。

(4)工作速率:LVPECL和CML都工作与非饱和态,翻转速率高,能支持极高的信号传输。LVDS的噪声容限较小,无法支持极高速率传输。

LVDS基本概念见上一篇

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?