1. DDR多通道技术

从DDR的访存特性来说,对同一块DDR,两个访存操作之间需要一些时间间隔,这里面包括CL (CAS时延), tRCD(RAS到CAS时延),tRP(预充电有效周期)等。

为了提高DDR的访存速度,可以使用多通道(channel)技术。如果数据存储在不同通道的内存条上,内存控制器就可以并行的读取这些数据:

总带宽 = 单个内存条带宽 * 通道数

但是由于程序的局限性,一个程序并不会把数据放到各个地方,从而落入另一个DIMM里,往往程序和数据都在一个DIMM里,加上CPU的Cache本身就会把数据帮你预取出来,这个多通道对速度的提高就不那么明显了。

另外一种提高访存带宽的技术就是让同一块内存分布到不同的通道中去,这种技术叫做交织(Interleaving), 此时多通道的技术才能发挥更大的用处。

2. 内存交织

2.1 SOC各组件访问内存架构

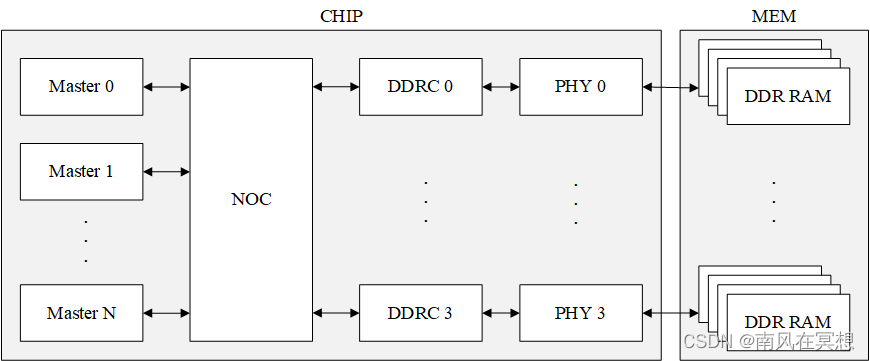

SOC中通常有多个master经过NOC访问DDR,结构如下图:

- master数量多,访问行为不一致

- 包含多个DDRC(DDRC可能支持多通道技术)

内存交织的实现方式:

- 内存交织将内存按照粒度(256B, 512B, 1KB, 2KB …)分配到不同的memory controller

- 内存交织将内存按照粒度(256B, 512B, 1KB, 2KB …)分配到同一个memory controller的不同通道上

各组件的视角:

- 从master视角看(该视角也是软件视角),此时看到的仍然是一块连续的内存

- 从NOC视角看,此时一块连续的内存已经被均匀的分布到不同的memory controller(或同一个memory controller不同通道)所控制的内存中。

由于软件看到的是连续内存,故不需要关注如何高效利用DDRC,各master的内存交织由NOC统一管理。若master发出跨粒度的trans,会被NOC拆分。

内存交织的优点:

- 统一的地址空间

- 自动负债均衡

- 带宽与交织的通道数成正比

内存不交织的优点:

- 根据流量类型、功能或其他考虑因素显式地划分工作负载

- 独立电源模式切换和/或频率变化

本文探讨了DDR多通道技术及其对访存速度的影响,并详细介绍了内存交织技术的工作原理及其实现方式。通过多通道技术和内存交织技术,可以显著提升内存访问带宽。

本文探讨了DDR多通道技术及其对访存速度的影响,并详细介绍了内存交织技术的工作原理及其实现方式。通过多通道技术和内存交织技术,可以显著提升内存访问带宽。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?