前面介绍了PI评估时用到的CPM中的Rdie(芯片电源完整性中芯片Rdie参数的影响和分析),本文来介绍另一个重要的参数Cdie。

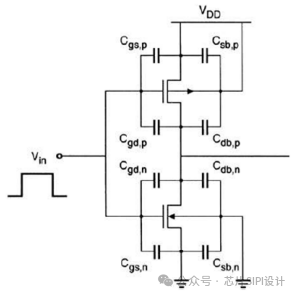

随着晶体管尺寸的减小,在电路的有源业务模式期间,预计会有更大的di/dt。由于这种现象,电流绘制的较大尖峰对设计不增加片上电容(Cdie)的稳健供电解决方案提出了巨大挑战。有各种众所周知的有意去耦方法来增加Cdie,例如金属指电容(metal-finger),金属绝缘-金属电容(MIM)和晶体管电容(transistor cap)。由于硅面积和制造成本方面的缺点和权衡,增加晶体管电容的方法不太有利。在晶体管器件中有一些固有的参数也对整个Cdie做出了贡献。下图描述了存在于互补金属氧化物半导体(CMOS)器件内的栅电容和结电容。

下图为CMOS器件中寄生电容的实际出现的位置,栅极到硅衬底的电容由栅极与沟道之间的氧化电容(C1)和沟道与硅衬底之间的耗尽电容(C2)等元件组成。多晶硅栅极与源极和漏极之间的重叠产生栅极到漏极(C3)和栅极到源极(C4)电容。通常情况下,由于边缘电场线,C3可能不等同于C4。同时,在源-衬底(C5)和漏极-衬底(C6)边界区域建

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1481

1481

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?