随着计算机技术日新月异的发展,对于I/O传输速率的需求愈发提高,PCI总线由于是并行传输,在时钟频率提高之后会带来信号偏移和串扰的问题从而使信号衰减失真,同时在数据传输速率不断提高之后PCI总线还面临着管脚限制,传输速率有限,以及缺乏服务质量和电源管理等多种问题。鉴于PCI总线的一些缺点,在21世纪初由PCISIG组织公布了新一代I/O总线,即PCIe(Peripheral Component Interconnect Express)总线。PCIe总线采用了一些全新的设计规范,在技术上有极大的提升,能有效的解决PCI总线残留的种种难题,它的技术优势主要有以下几个方面:

1、PCIe总线采用串行传输方式,相较于并行传输,有效解决高速传输下的信号串扰问题以及管脚数量需求的问题。

2、点对点串行互联。相较于PCI总线的共享模式,点对点方式解决了多个终端争抢总线需要仲裁的问题,提高了终端到终端的传输效率。

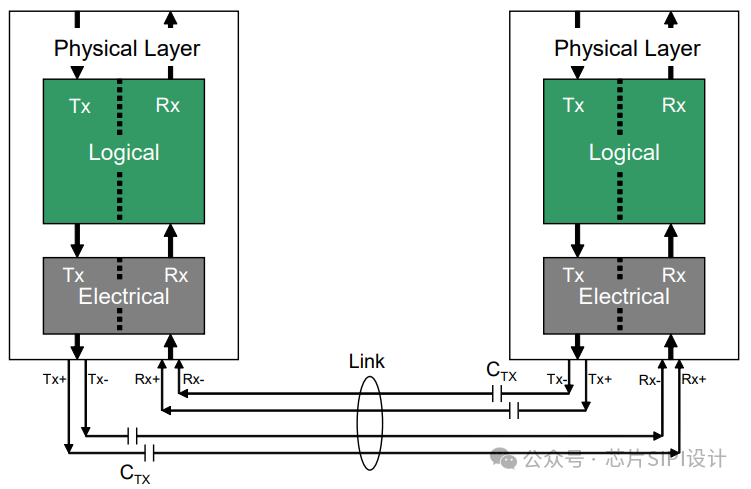

3、全双工,差分对传输。PCIe在物理层使用了4条信号传输线组成两组差分对,可以同时传输和接收,极大提高传输效率。

4、低功耗和电源管理。PCIe加入了对于低功耗的处理,增加电源管理功能,在不同的使用要求情况下采用不同的电源状态以节省功耗。

5、灵活拓展性。支持多种终端设备通过PCIe相连。

6、支持热插拔。使用更加方便快捷。

7、支持Q0s(服务质量)。对于数据传输包定义优先级,从而使优先级高的优先级进行传输。

8、具有分层结构。PCIe体系结构可分为设备层,事务层,数据链路层和物理层,每个层次各司其职,共同协作进行数据的传递。

9、错误检测与处理。在分层架构中,对于数据的错误传递具有检测与处理能力。如数据链路层接收到了数据包会在本地备份,等到接收端反馈,如果反馈错误,则将备份的数据包再次进行传递。

10、在软件层保持与PCI兼容。

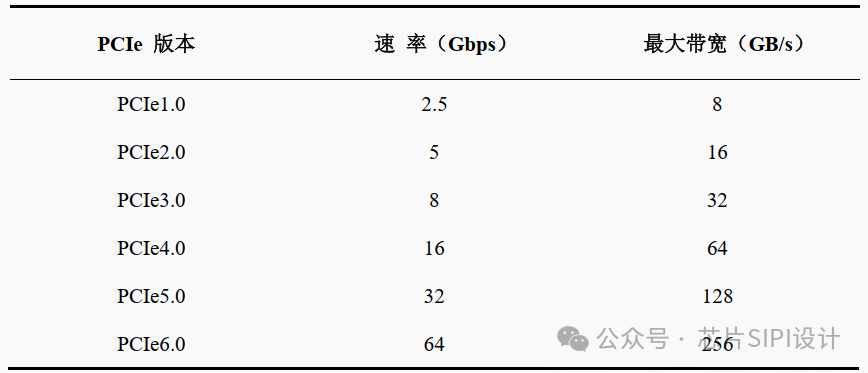

由于PCIe的众多优势,自协议公布以来得到迅速的推广和使用。在2003年公布的第一代至今,PCIe已经经历了多次迭代,数据的传输速率也是每次翻倍的增加,如下表所示,单通道速率从最初PCIe1.0的2.5Gbps,到PCIe2.0的5.0Gbps和PCIe3.0的8.0Gbps,再到PCIe4.0的16.0Gbps和PCIe5.0的32.0Gbps,2022年刚出的PCIe6.0传输速率已经达到惊人的64.0Gbps。

PCIE的提出在I/O总线技术领域实际具有突破性的,凭借众多的优势使得其应用前景非常广泛,其发展势头必然随着信息技术的进步而变得越发迅猛。

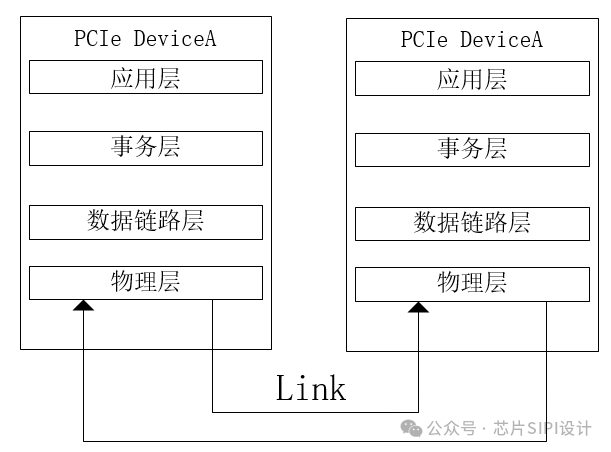

绝大多数总线都是分层结构,PCIe同样如此。在分层结构中,每层都有各自的功能和职能,这种层层协作进行数据交互的方式,使用层次设计,当接口版本升级时,比如从PCIe3.0升级到4.0,在硬件电路设计上,如果只有某层的逻辑发生更改。则只需要改动该层,其它层次的电路可以维持原样,这样带来了易维护性和可升级性。

PCIe的分层结构如下图所示,按照协议规定,PCIe主要是由应用层,事务层,数据链路层和物理层构成。从主体功能上来看,应用层定义了PCIe设备的类型功能。事务层的主要职责是通过设备层的指令进行TLP(Transaction Layer packet)的发送和接受,其他功能包括服务质量、事务排序、流量控制等。数据链路层的主要职责是对DLLP(Data Link Layer packet)进行发送或者接收,其他功能包括Ack/Nak协议、电源管理和流量控制等。物理层的主要职责是负责所有的包数据物理传输,发送端把数据分发到各个通道,接收端把各个通道上的数据打包处理。

应用层

应用层在PCIe中决定了相应设备的一些基础功能和属性,通常情况下,该层逻辑可以使用硬件完全实现或者使用软硬件共同实现。如果该设备为端点,最多可以使用8项功能(Function)。另一种情况下,若该设备为交换开关,这种情形下,应用层需要实现交换开关所涉及到的逻辑功能,如包路由等相关逻辑。最后一种情况,如果该设备为Root,在此情形下,应用层在总线系统中被看做虚拟的PCIe总线0,从而代表整个PCIe的系统和CPU进行数据通信。

事务层

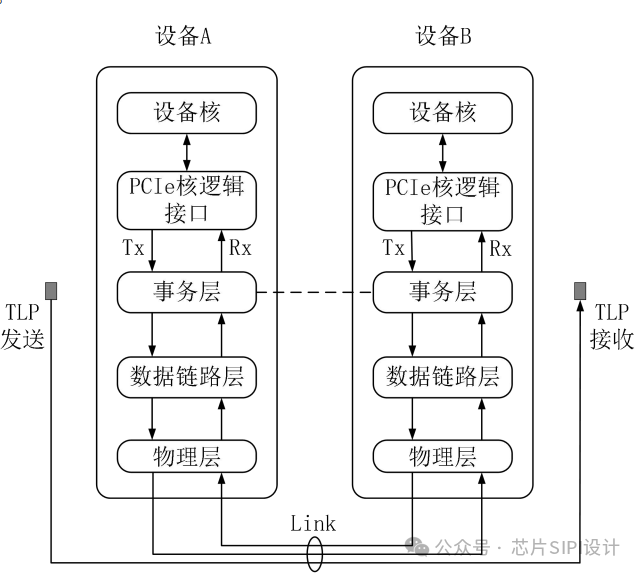

事务层的主要功能是对TLP进行逻辑操作,如创建(发送)或者解析(接收)。如下图事务层图所示,由应用层下发到事务层发送侧逻辑数据,在事务层对数据包加上Header在尾部加上端对端循环冗余校验码(End-to-endCyclicRedundancyCheck,ECRC),并将打包后的数据发往数据链路层。事务层在接收逻辑部分会接收下层逻辑即数据链路层发来的数据包,此时需要对数据包中的ECRC逻辑进行检测,以确定包在发送到接受的过程中是否产生了CRC错误,若检查没有错误,则去掉ECRC部分并将TLP中的剩余的Header和数据负载转发到应用层,若检查到错误,则将数据抛弃。

对于事务层而言,除了最基本的对于发送端对于包的发送和接受端对包的接受检测之外,还可以通过配置Header来实现其他功能逻辑,比如事务优先级排序、虚通道、流量控制、端口及虚通道仲裁、传输类别、服务质量、电源管理等能力。

数据链路层

数据链路层的主要功能对DLLP进行逻辑操作。如创建(发送)或者解析(接收),除此之外,该层还实现Ack/Nak协议,数据备份,流量控制等。

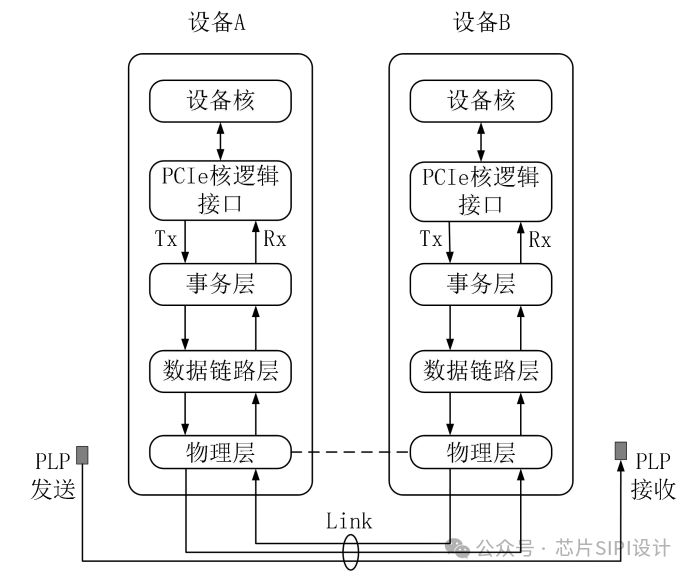

如下图数据链路层所示,由事务层装包的TLP下发到数据链路层发送侧,数据链路层对数据包加上包序列号,在尾部加上端对端链路冗余检测码(End-toend Link Redundancy Check, ECRC),构成一个DLLP,并将打包后的数据发往物理层。事务层接收侧接收数据链路层发送的数据包,此时需要对DLLP进行Ack/Nak机制,此目的是检测传输过程中是否产生了CRC错误,若检查没有错误,则会去掉LCRC部分和包序列号,然后将DLLP发送到事务层,若检查到错误,则会通知重传。

在PCIe协议中定义,数据链路层具有自发的错误校验功能(Ack/Nak机制)。发送侧的数据链路层会对每一个事务层传来的TLP在内部重试buff中做备份,当其接收到发出的接受反馈,以确认该包已经被成功的传递后,数据链路层会在重试bufffer中删除这个备份的TLP。如果在进行CRC检测时检测到包出现错误,则会向发送方反馈重发请求,发送逻辑检查到反馈信号后,会从重试Buffer中再次发送该TLP包

物理层

物理层的主要功能是对所有的包数据传输包进行处理,物理层在发送端将包分发到各个通道进行传输,在接收端把每一个通道上的数据进行汇总处理。

由于在PCIe体系的分层结构,物理层处于最底层,不管是物理层的TLP还是数据链路层的DLLP都需要依靠物理层完成包的发送和接受操作。按照协议规定,物理层可以细分为逻辑物理层和电气物理层。逻辑物理层是纯数字逻辑,连接到数据链路层,主要职责是实现对数据在数字逻辑层面的操作。物理电气子层连接到通道链路接口,主要职责是实现功能包括串并转换,时钟恢复和差分驱动器等。如下图所示意,来自上层逻辑发来的TLP和DLLP都会被加上1字节的开始字符(Start Characters)和1个字节的结束字符(End Characters)。在物理层的接收部分,在收到开始字符后,进行数据锁定直到检测到结束字符后,将去掉开始字符和结束字符的数据帧发回给数据链路层。

物理层还可以进行通道中链路的初始化和训练,该训练过程是基于硬件电路而完全自动进行的过程。当物理层的链路的初始化和训练完成之后,设计者可以通过定义寄存器的配置,确定当前使用的PCIe设备的一些基本链路属性:包括通路翻转、链路速率配置、极性更换等。

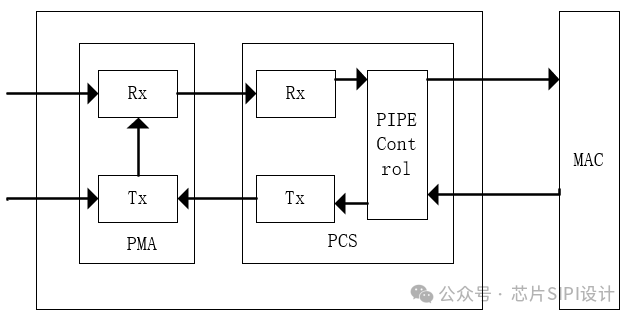

按照协议规定,逻辑物理层也可以分为 MAC 层和 PCS 层。如下图所示,数据链路层发来的数据经过 MAC 层进行逻辑控制后再通过 PIPE 接口发往 PCS 层, PCS 层对数据进行处理之后传递到 PMA 层, PMA 层经过并串转换和一系列操作之后把串行数据经过差分对进行传递。对于 Rx 方向而言,链路数据经过 PMA 层的串并转换后发往 PCS 层,由 PCS 层进行数据处理得到正确的数据后,再通过 PIPE 接口发往 MAC层,最有由 MAC 层发到上游逻辑。

PMA 层是整个物理层的最底层,从逻辑子层发送过来的数据经过电气子层处理之后发到 Tx 链路上。如下图所示,在电气物理层主要实现的逻辑功能包含时钟恢复电路、信号加重去加重、锁相环电路、并串和串并转换电路以及差分驱动接收电路。电气物理层发送逻辑会采用倍频后的高频时钟将 PCS 层输入的并行逻辑字符转变成串行逻辑字符,逻辑信号经过差分发送驱动器转化成电气信号后发送至差分链路通道。电气物理层接受逻辑通过对链路通道的电气信号进行判断和处理,再利用差分接收驱动器转换为逻辑信号,采用时钟数据恢复电路的恢复时钟同步数据并将串行逻辑字符转换为并行逻辑字符。

PIPE接口

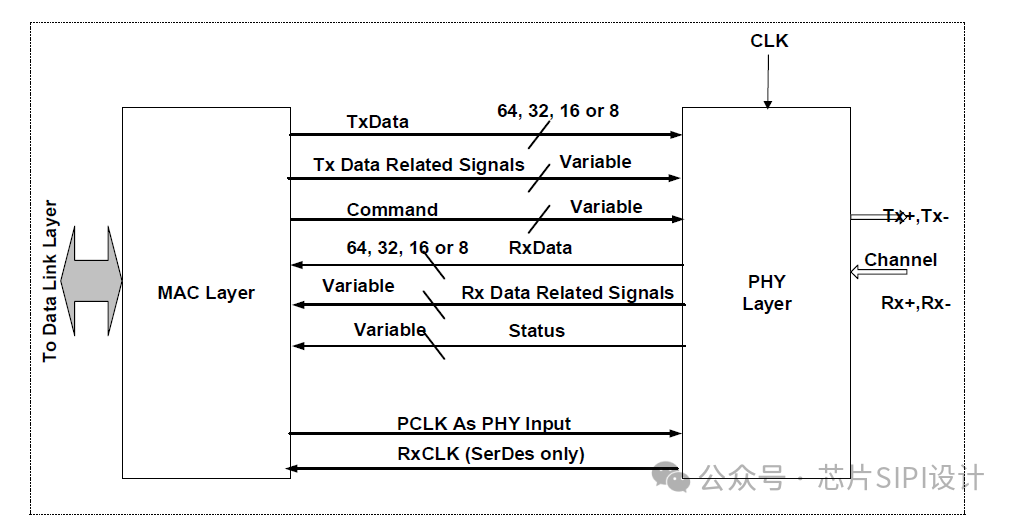

如下图所示,Intel提出的PCIe物理层接口(Physical Interface for PCIExpress,PIPE),对PCIe物理层中的媒介适配层(Media Access Layer,MAC),也被称之为控制器,和物理编码子层(Physical Coding Sub-layer,PCS)之间的接口进行了统一规范,为市场提供了市场准则。

由Intel提出的IPE规范只是处于行业建议,旨在为厂商提出参考而并非由PCI-SIG或者PCIe协议制定的统一标准。设备厂商可以根据自己需求决定需不需要采用PIPE接口。目前大部分厂商选择使用Serdes器件来实现PCIe中的PCS和PMA逻辑,大部分厂商也选择将MAC层(以及事务层和数据链路层等)和PCS层/PMA层进行独立设计。对于目前市场上也有专门做Serdes的公司,可以采用PIPE接口,为PHY厂商提供行业标准,对于其他厂商而言,有助于设备连接从而保持更好的兼容性。也有很多厂商选择独立设计PCIe相关设备(如部分基于PCIe的ASIC等),此时就以实现功能为主,可以选择不采用PIPE接口。

PIPE接口的出现,芯片的高速部分与低速部分得以分离,以IP核的形式通过PIPE接口相连,所以对于集成电路设计者来说,利用已有的可获取资源辅助开发,使用IP核的方式,可以大大的缩短研发时间,从而使相应产品快速上市。用户甚至可以基于FPGA[38]中的SerDes/PCS[35,37]相关IP来实现多种高速串行接口的设计。

PIPE规范最早提出是用于PCIe总线中的,但是随着厂商对该接口协议的认可,升级迭代后的PIPE接口支持了其他的串行接口,如PCIExpress、SATA、USB等多种高速串行接口。

1587

1587

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?