之前我们在UG934中了解到了Xilinx关于视频处理系统的相关概念,想要开始搭建系统,还得了解一下每个涉及到的IP。先从视频输入开始,Xilinx视频系统中通常使用AXI4-Stream视频协议来传输视频,本章学习的目标就是完成常用视频接口(XIlinx文档中称为clocked parallel video data with synchronization signals,具有同步信号的时钟并行视频数据)到AXI4-Stream接口的转换,也就是本章标题提到的IP——Video In to AXI4-Stream(官方文档PG043)。

Video In to AXI4-Stream IP的概览

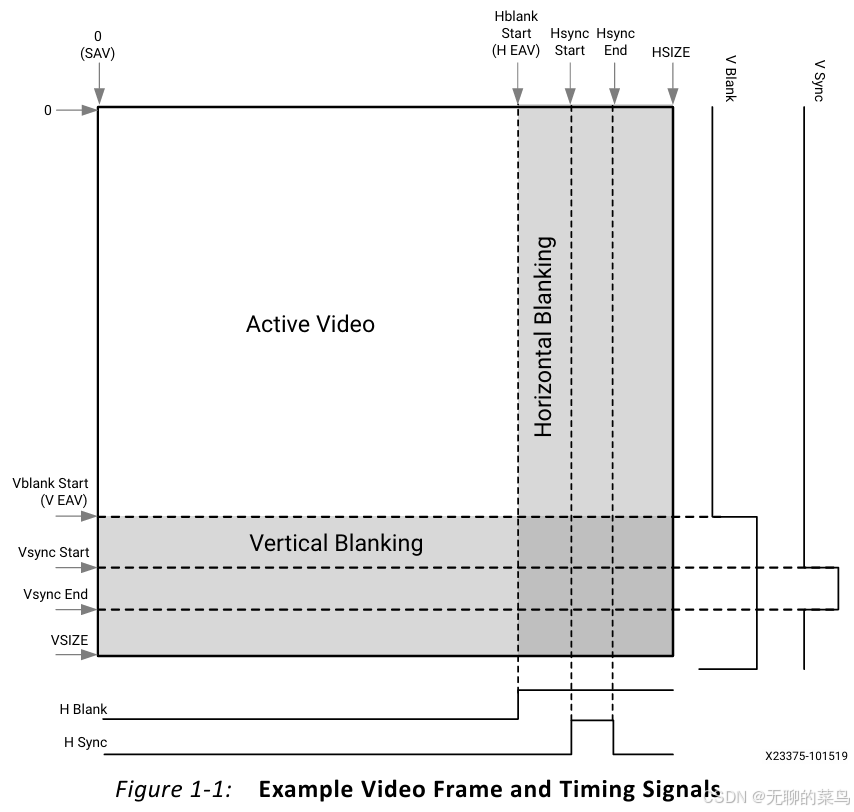

IP接收的时钟需要像素时钟和并行视频数据,以及如下之一的时序信号:

- Vsync,Hsync,and Data Valid(有时也称为Data Enable,DE)

- Vblank,Hblank,and Data Valid

- Vysnc,Hsync,Vblank,Hblank,and Data Valid

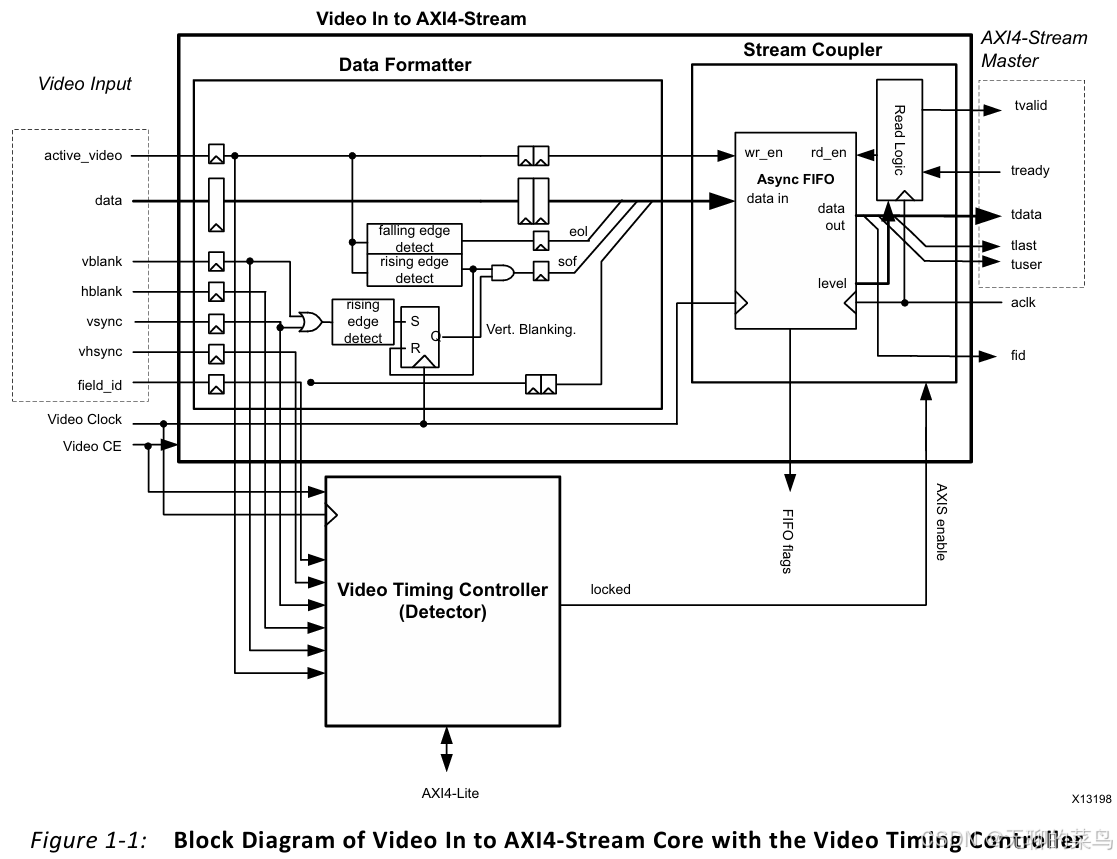

文档特意提及了VTC的设置与上述信号选择相关,并建议使用VTC的“locked”信号连接“axis_enable”,在视频输入丢失或者不稳定时控制AXI4-Stream总线,看一下IP的示意框图。

Xilinx建议在没有视频时钟的时候复位VTC和Video In to AXI4-Stream核。

性能

最大频率

这一点的影响因素很多,FPGA型号、速度等级、可用资源、Xilinx工具版本等。

延迟

当下游处理模块获取数据速率超过像素速率时,典型延迟为6个视频输入周期+3个AXI aclk。当下游处理模块获取数据速率低于像素速率时,需要使用FIFO来平衡输入输出速度的不匹配。此时会引入额外的延迟。

吞吐量

因为AXI4-Stream总线上不会传输消隐数据,可以在总线时钟速率低于视频时钟的情况下满足平均速率所需的带宽。

当总线时钟大于或等于输入视频时钟时,只需要最小的(深度32)的缓冲,当总线速度高于视频的平均速率(可简单理解为仅传输有效像素时的速率)低于输入视频时钟时,FIFO最小深度需要

FIFO depth min = 32 + Active Pixels * Fvclk / Faclk

Fvclk:视频输入时钟(像素时钟)

Faclk:总线时钟

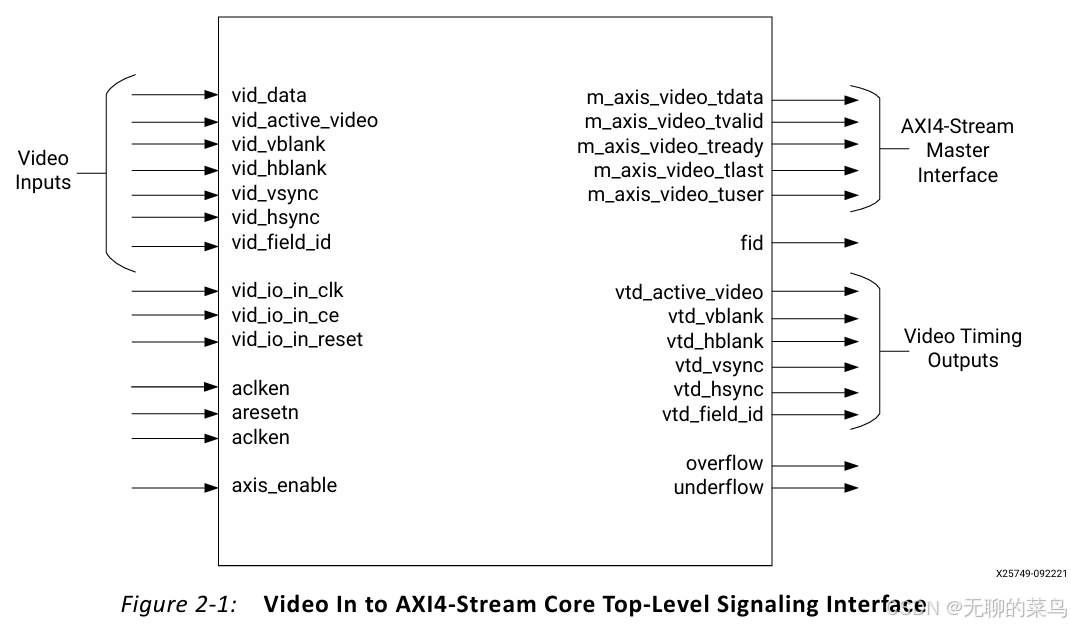

IP接口

端口描述

通用接口

| 通用接口 | |||

| 信号名称 | 方向 | 位宽 | 描述 |

| aclk | 输入 | 1 | AXI4-Stream时钟 |

| aclk_en | 输入 | 1 | AXI4-Stream时钟,高有效 |

| aresetn | 输入 | 1 | AXI4-Stream复位,低有效,ACLK时钟域 |

| axis_enable | 输入 | 1 | 写FIFO使能,高有效,vid_io_in_clk时钟域 |

| fid | 输出 | 1 | 隔行视频,0-奇数行,1-偶数行 |

| vid_io_in_clk | 输入 | 1 | 视频时钟,仅在独立时钟模式 |

| vid_io_in_ce | 输入 | 1 | 视频时钟使能 |

| vid_io_in_reset | 输入 | 1 | 视频时钟域复位,高有效 |

| overflow | 输出 | 1 | FIFO溢出(写满),vid_io_in_clk时钟域 |

| underflow | 输出 | 1 | FIFO下溢(读空),aclk时钟域 |

视频时序接口(VTC)

| 视频时序接口 | |||

| 信号名称 | 方向 | 位宽 | 描述 |

| vtd_vsync | 输出 | 1 | 垂直同步 |

| vtd_hsync | 输出 | 1 | 水平同步 |

| vtd_vblank | 输出 | 1 | 垂直消隐 |

| vtd_hblank | 输出 | 1 | 水平消隐 |

| vtd_active_video | 输出 | 1 | 1-有效视频,0-消隐视频 |

| vtd_field_id | 输出 | 1 | 0-偶数场,1-奇数场 |

视频输入接口

| 视频输入接口 | |||

| 信号名称 | 方向 | 位宽 | 描述 |

| vid_active_video | 输入 | 1 | 0-消隐视频,1-有效视频 |

| vid_vsync | 输入 | 1 | 垂直同步,高有效 |

| vid_hsync | 输入 | 1 | 水平同步,高有效 |

| vid_vblank | 输入 | 1 | 垂直消隐,高有效 |

| vid_hblank | 输入 | 1 | 水平消隐,高有效 |

| vid_data | 输入 | 8-256 | 并行视频输入数据 |

| vid_field_id | 输入 | 1 | 视频场,0-偶数场,1-奇数场,非隔行视频接0 |

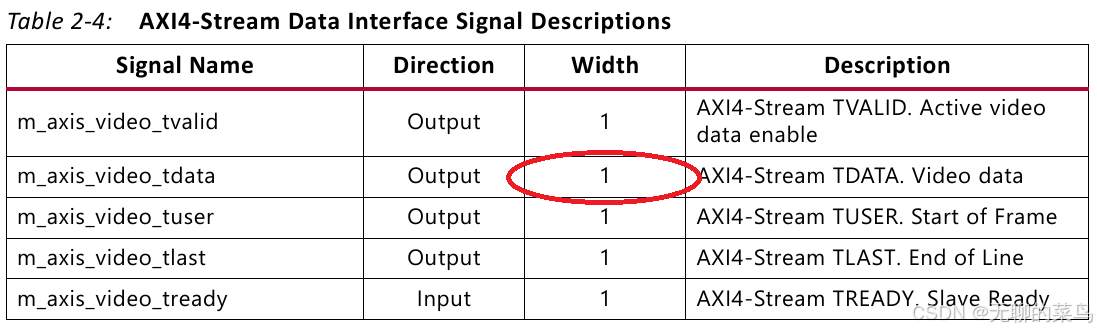

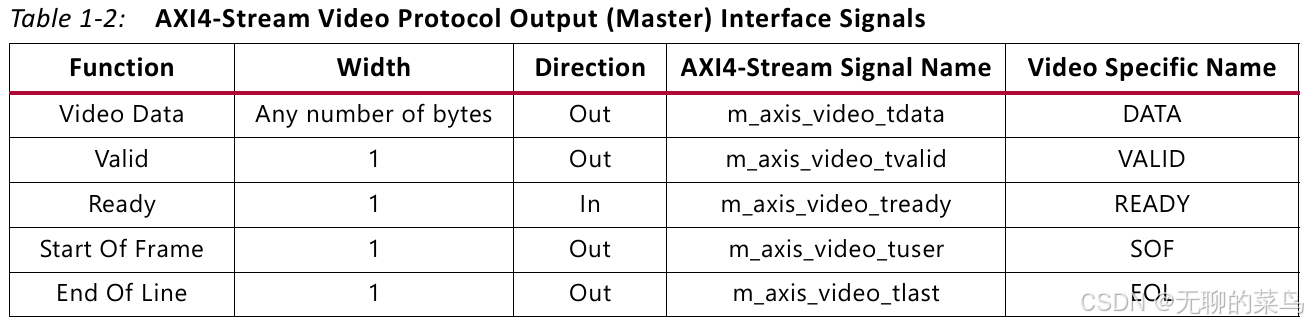

AXI4-Stream接口

这里需要注意,指南中位宽描述错误。

UG934中描述如下

整理后表格如下

| AXI4-Stream接口 | |||

| 信号名称 | 方向 | 位宽 | 描述 |

| m_axis_video_tvalid | 输出 | 1 | 视频数据有效 |

| m_axis_video_tdata | 输出 | nByte | 视频数据 |

| m_axis_video_tuser | 输出 | 1 | 帧起始 |

| m_axis_video_tlast | 输出 | 1 | 行结束 |

| m_axis_video_tready | 输入 | 1 | 从设备就绪 |

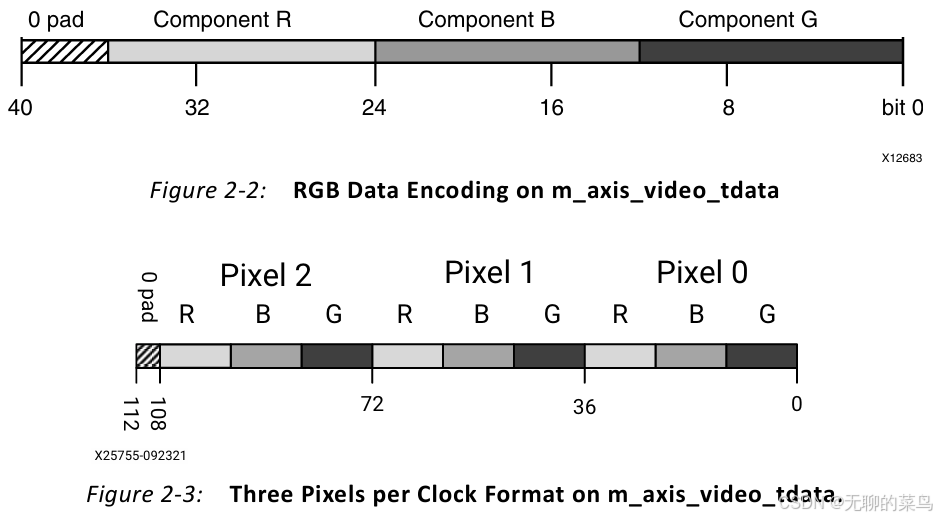

数据

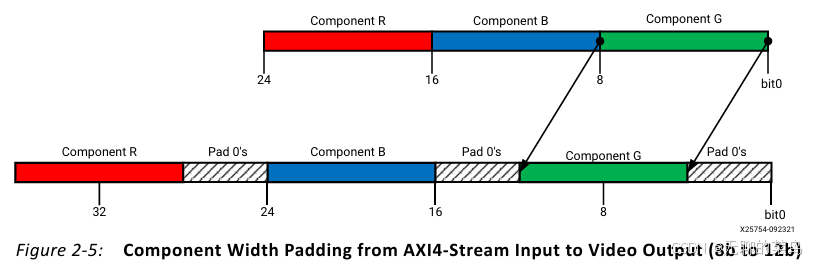

TDATA位宽是8比特的整数倍(按字节算),如果视频数据宽度不是8的整数倍,需要在高位补0。对于一个时钟多个像素数据的情况,AXI4-Stream输出会将其位宽填充到8的整数倍,但不会对数据进行解析(仅仅是一个转发功能,怎么进就怎么出)。

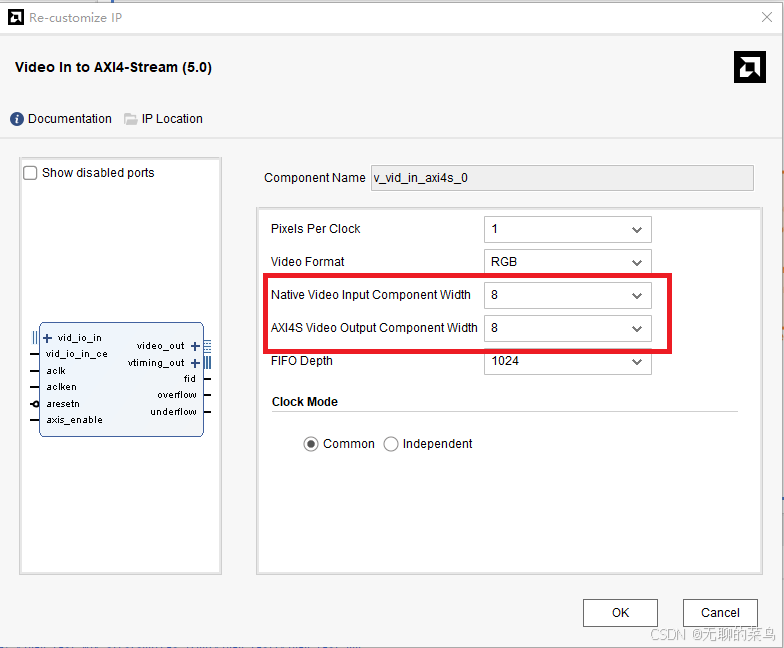

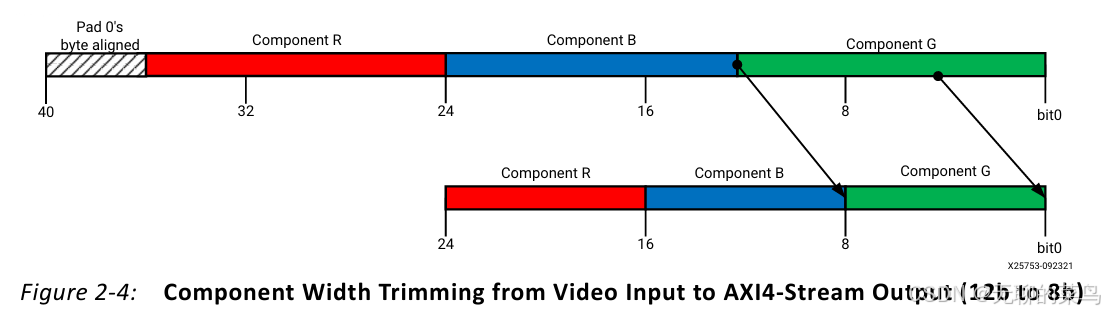

IP具有位宽转换功能,可以转换输入输出位宽,然后再将数据打包到AXI4-S总线上。直接在IP设置界面选择相应的位宽即可。

手册中对于位宽的示意如下,分别为输入视频位宽12位,AXI4-S总线上打包的视频位宽8位;输入视频位宽8位,AXI4-S总线上打包的视频位宽12位。

IP相关情况介绍完了,下一章介绍IP的使用。

3054

3054

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?