[SystemVerilog语法拾遗] 谈谈foreach使用时数组下标对遍历顺序的影响

通常我们在使用foreach遍历数组元素的时候不像for循环那么直观的知道循环变量的值的变化顺序以及step大小,foreach有自己一套遍历顺序,且默认step为1,在使用多维数组的遍历时遍历顺序有时候就会对结果产生重大影响,尤其是当我们在foreach循环中添加队列操作时,所以有必要通过一个实验来对foreach遍历顺序做个系统的总结。(当然,最直接的方法是去查IEEE sv的标准,不过标准中文字描述还是没有我们直接跑个仿真来的直观)

这里我们以二维bit数组为例(foreach认为是一个三维数组,bit数组的下标也被认为是一个维度),更多维的数组可以依此类推。

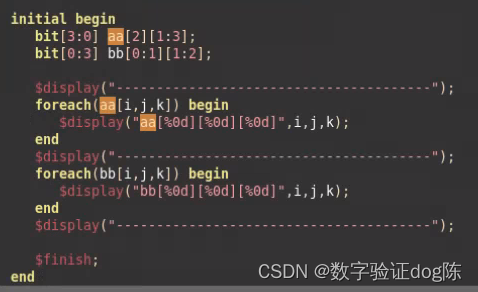

代码实例如下图所示:

仿真结果如下图所示:

由此我们得出如下结论:

以数组 bit [LSB0:MSB0] aa [LSB1:MSB1][LSB2:MSB2]; 为例(LSB和MSB只用来标识遍历顺序,不标识实际大小)

1、foreach的第一个维度是定义在[LSB1:MSB1],最后一个维度为[LSB0:MSB0],中间维度按顺序定义在[LSB1:MSB1]的右侧。

2、遍历顺序时钟是从第一个维度的LSB开始递归遍历其所有子维度的LSB到MSB,最终遍历到最后一个维度的MSB,即遍历顺序是aa[LSB1][LSB2]…[LSB0], aa[LSB1][LSB2]…[LSB0+1], …, aa[MSB1][MSB2]…[MSB0]

3、[LSB:MSB]也可以直接用维度简写[SB],相当于[0:SB-1]

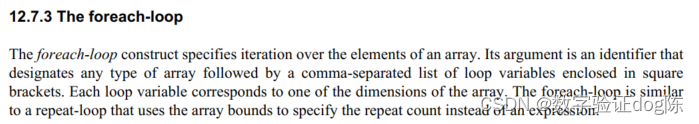

SystemVerilog IEEE 1800-2017标准上关于foreach使用的描述截图如下,大家可以结合上面的例子理解下

1234

1234

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?