DDR 是双倍数据速率(Double-Data-Rate)的英文缩写,千兆 PHY、DDR3 芯片的数据接口就使用了这一技术。本文主要讨论 Xilinx 7-Series FPGA SelectIO 资源的内部结构和使用方法。

目录

1 SelectIO 资源介绍

Xilinx 把可配置的 I/O 块资源称为 SelectIO 资源,SelectIO 可以实现不同的 I/O 标准,包括单端类型(例如 LVCMOS,LVTTL,HSTL 等)和差分类型(例如 LVDS,Mini_LVDS,RSDS 等)。

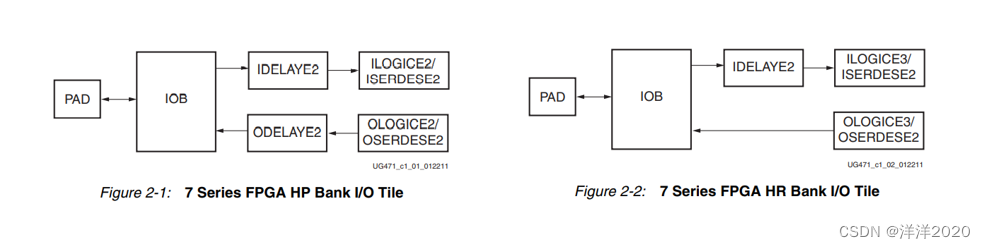

SelectIO 资源分布在两种 IO Bank 中,分别叫做 HP Bank 和 HR Bank,它们的内部结构如下图:

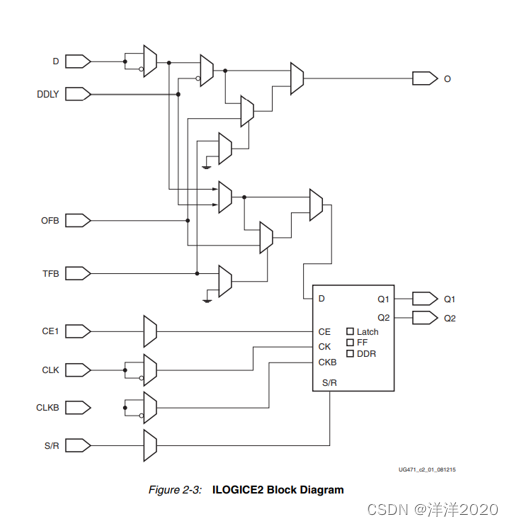

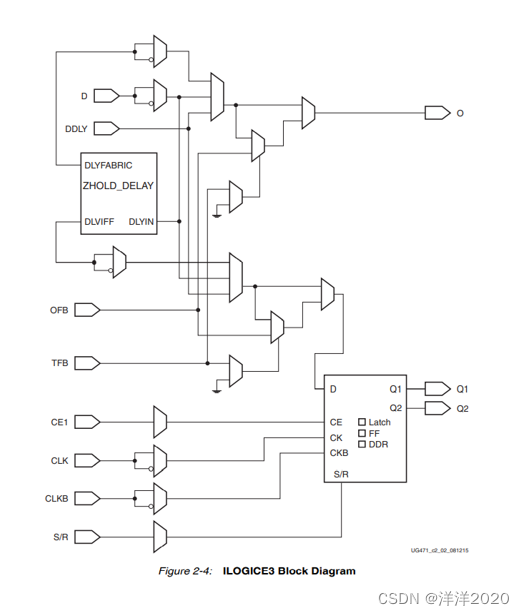

HP Bank 内部有单独的 IDELAY 和 ODELAY 资源,而 HR Bank 没有 ODELAY。ILOGIC 分两种,结构如下图:

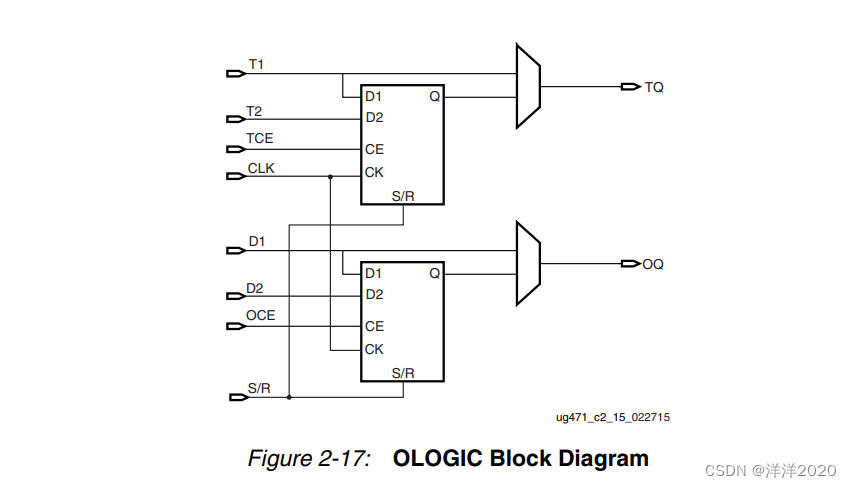

OLOGIC 的结构相对简单,包括两个 register 和两个 mux。

2 DDR 电路实现

千兆 PHY 芯片的 RGMII 接口采用了 DDR 技术,在使用 FPGA 千兆网口通信时,需要实现 RGMII 和 GMII 接口的转换电路。

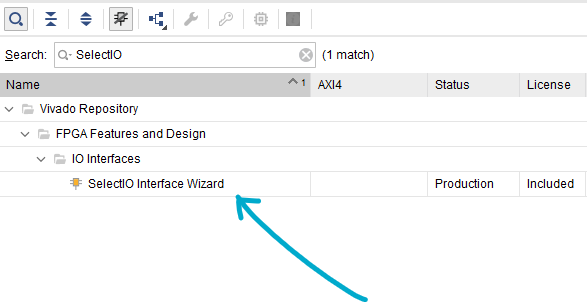

在 IP Catelog 中,输入 SelectIO,双击打开 SelectIO Interface Wizard。

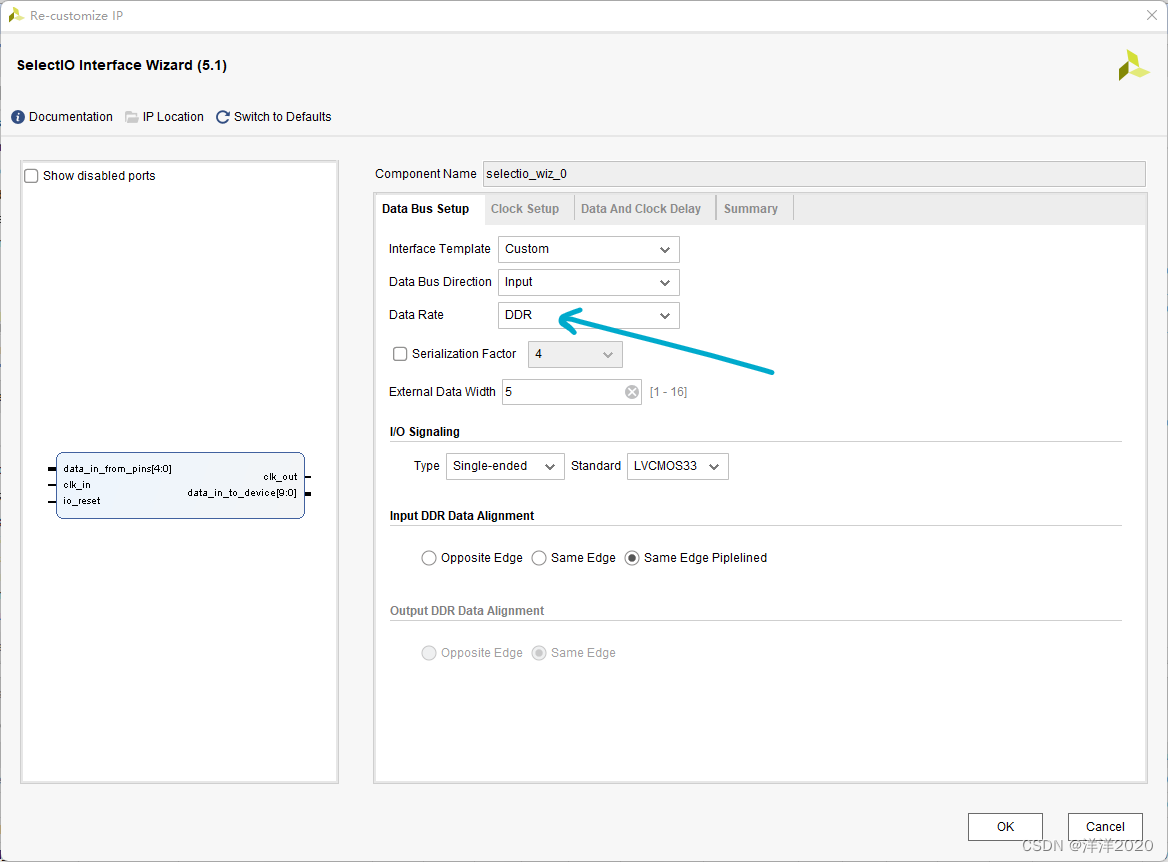

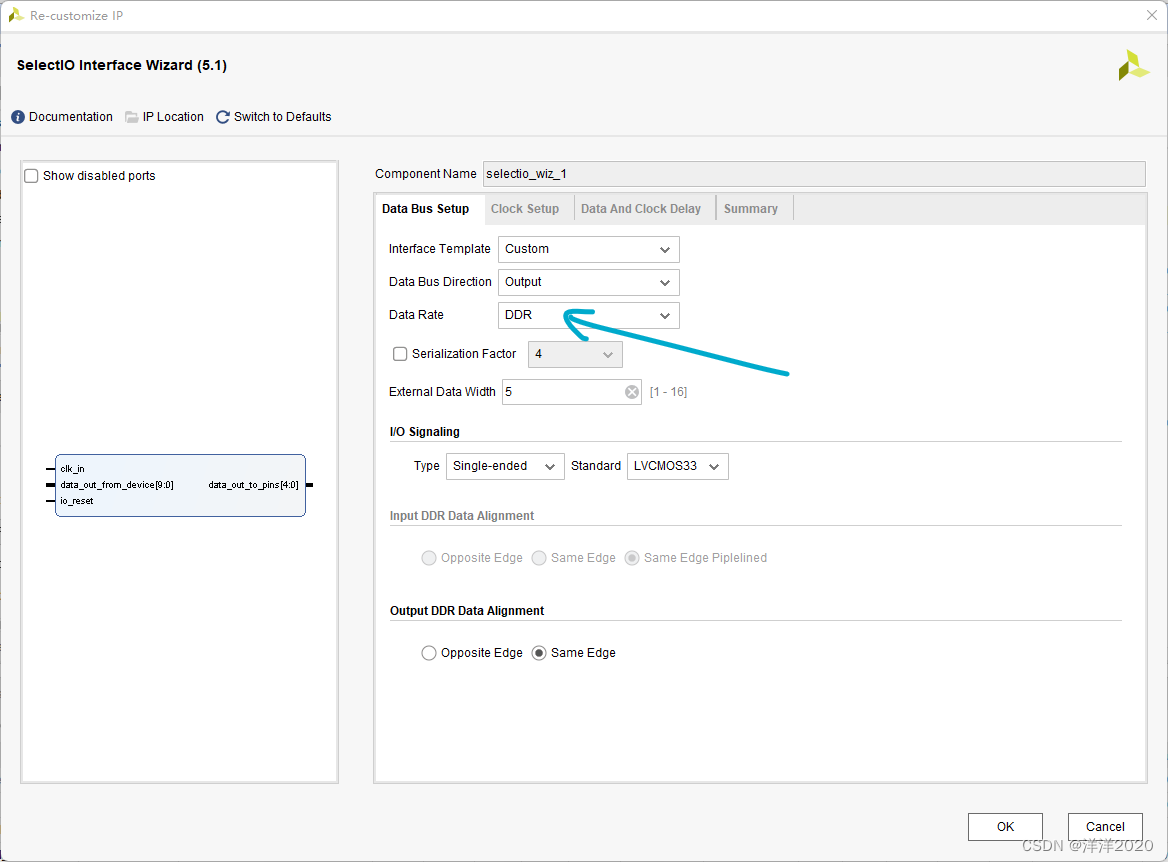

数据总线方向为 Input,Data Rate 这一项选 DDR,External Data Width 是 I/O 端口的个数,这里 RGMII_RXD 和 RGMII_RX_CTL 加起来共 5 比特。

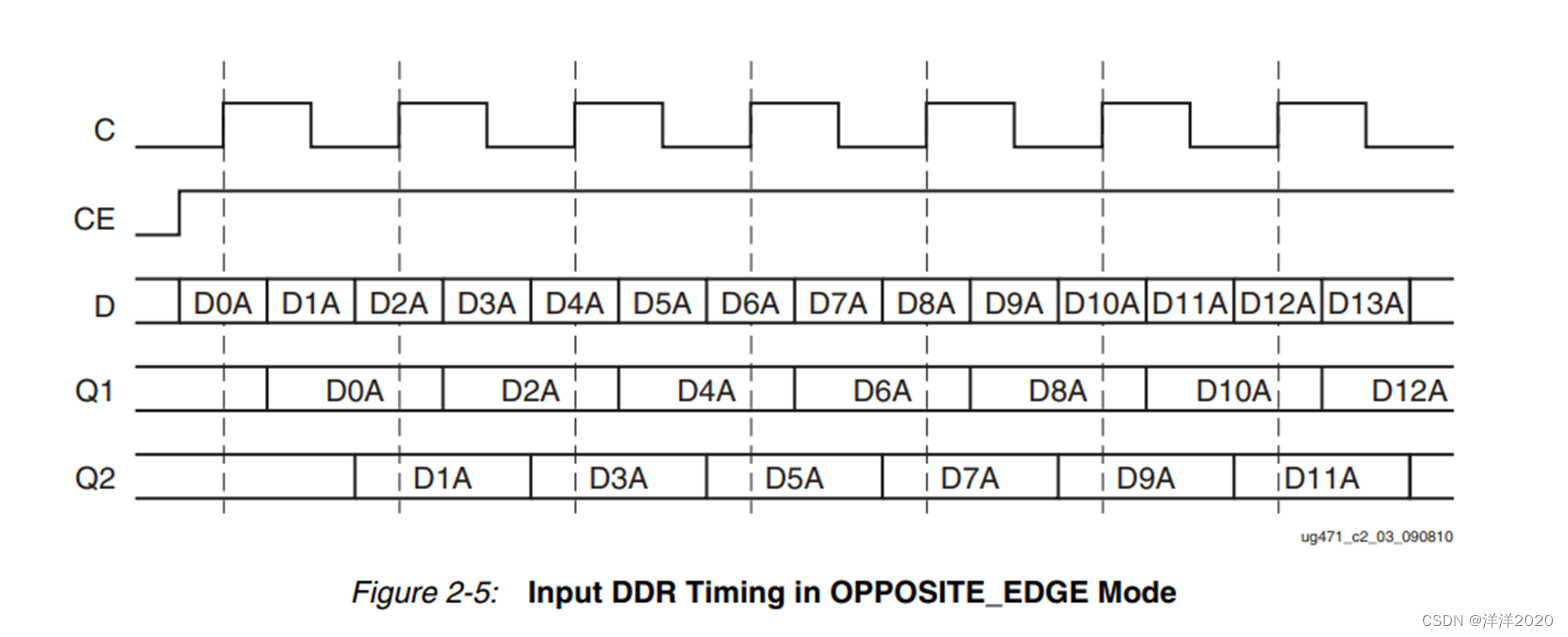

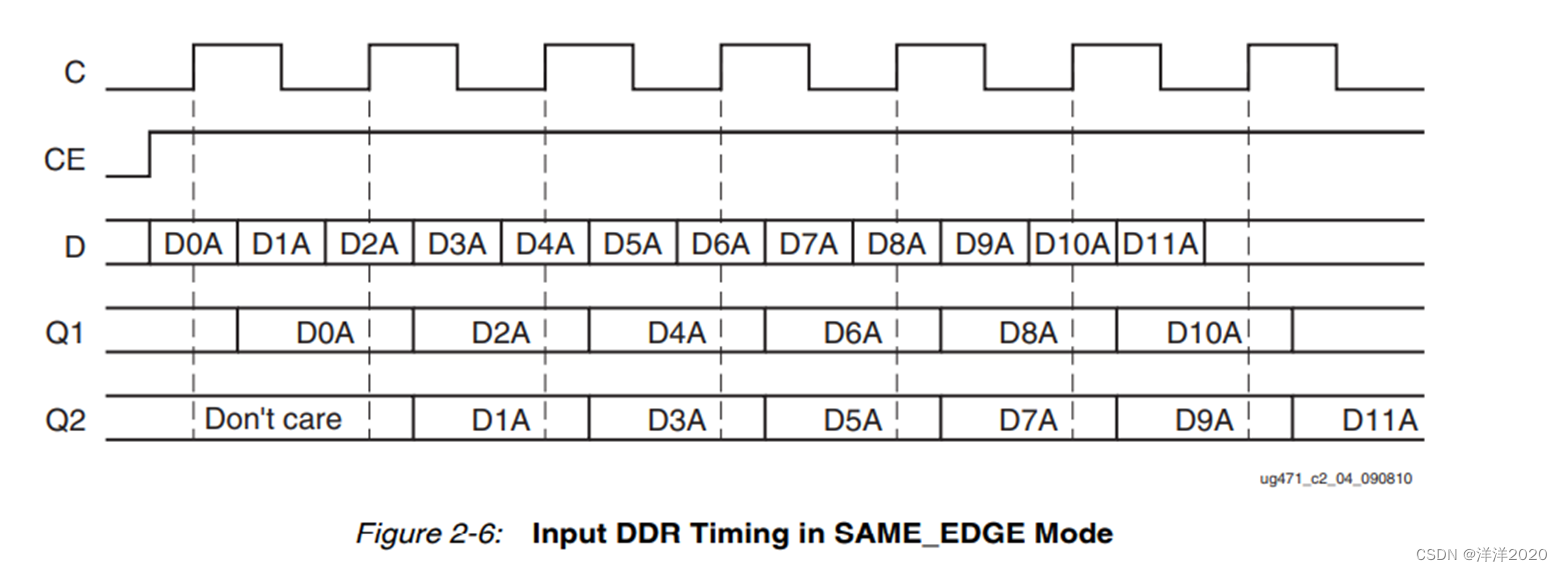

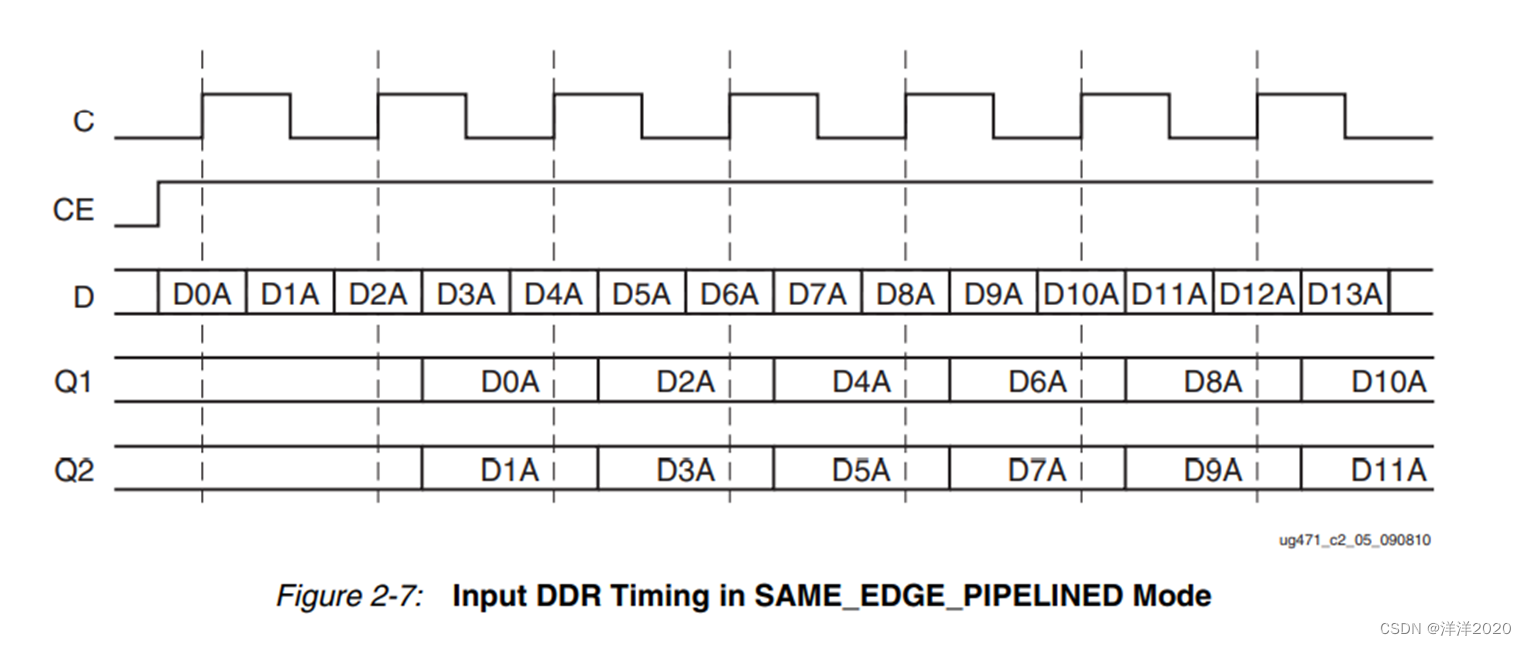

IDDR 数据对齐方式有三种,分别为 Opposite Edge, Same Edge 或者 Same Edge Pipeline,通常选择 Same Edge Pipeline 方式。

对于 ODDR,数据总线方向为 Output,Data Rate 这一项选 DDR,External Data Width 填写 5。

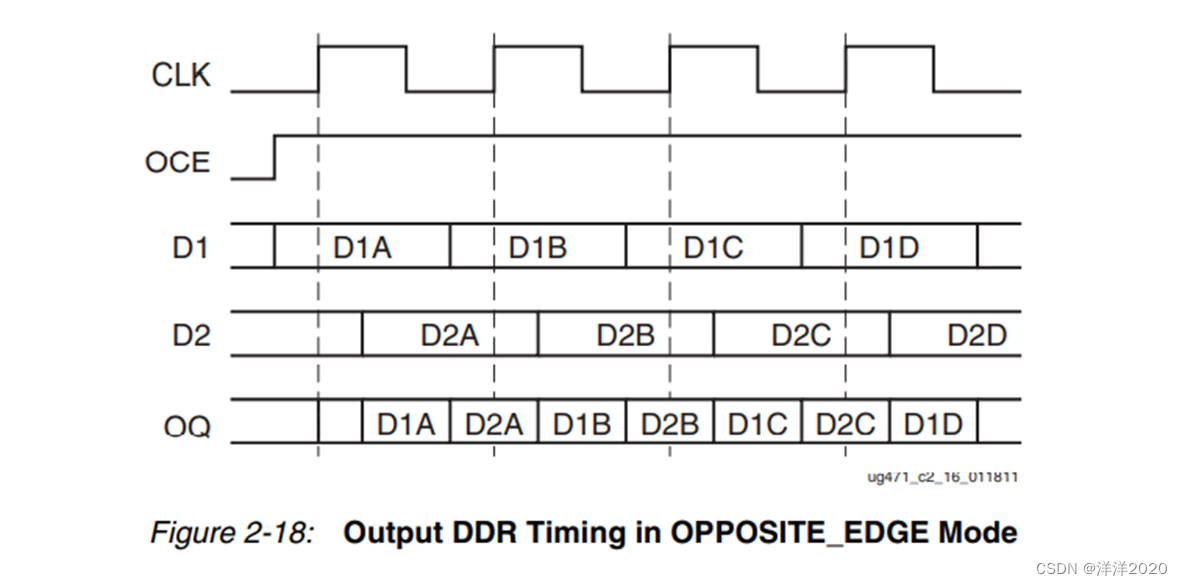

ODDR 数据对齐方式只有两种:Opposite Edge 或者 Same Edge,如果 D1 和 D2 在时钟同一个边沿发生变化,就对应 Same Edge 模式。

如果想检验 DDR 电路能否工作,可以借助 PHY 芯片自带的回环测试功能,参考以下博文。

https://blog.csdn.net/sxyang2018/article/details/127113911?spm=1001.2014.3001.5501

2294

2294

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?