1-是什么?

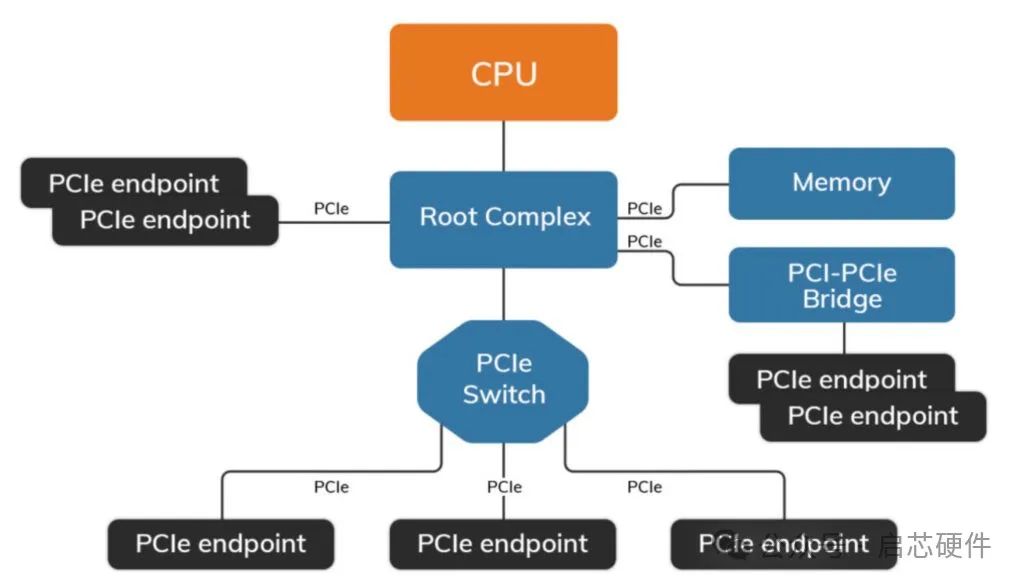

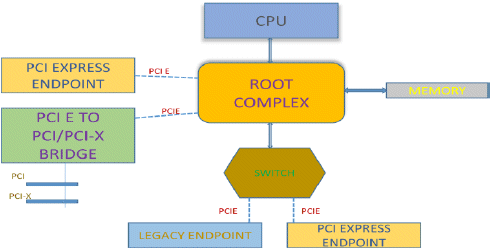

PCIe(Peripheral Component Interconnect Express)是一种高速串行总线标准,用于连接计算机的主板和外部设备,如显卡、网卡、存储控制器等。PCIe设备根据其功能和角色可以分为根端点(Root Complex,RC)、端点(Endpoint,EP)和插槽(Switch,SW)。

2-有什么区别?

1、RC:Root Complex

RC设备用于连接CPU/内存子系统 和 I/O设备;

RC模式下,PCIE配置头中的类型值为1;

RC模式下,支持配置和I/O事务

在RC模式下,设备扮演的是主机(Host)或根端点(Root Complex)的角色。

根端点是PCIe总线上的起始点,负责发起总线事务和管理总线上的所有设备。

在桌面计算机或服务器系统中,通常由主板上的芯片组或处理器内部的PCIe控制器扮演根端点的角色。

RC模式下的设备通常不会直接与其他设备通信,而是通过根端点来进行数据传输和控制。

2、EP:EndPoint

EP设备通常表示一个串行或I/O设备;

EP模式下,PCIE配置头中的类型值为0;

EP模式下,PCIE控制器接收针对本地内存空间的读写操作

在EP模式下,设备扮演的是端点(Endpoint)或从属(Slave)的角色。

端点是PCIe总线上的终端设备,负责接收来自根端点或其他设备的请求,并相应地进行数据传输。

EP模式下的设备通常是外部设备,如显卡、网卡、存储控制器等。

端点设备能够响应来自根端点或其他设备的总线事务,并执行相应的读取、写入或配置操作。

总的来说,RC模式和EP模式的区别在于设备扮演的角色不同。RC模式下的设备是总线的控制者和管理者,而EP模式下的设备是总线的终端设备,负责处理数据传输和响应请求。

3-PCIe RC模式的应用案例

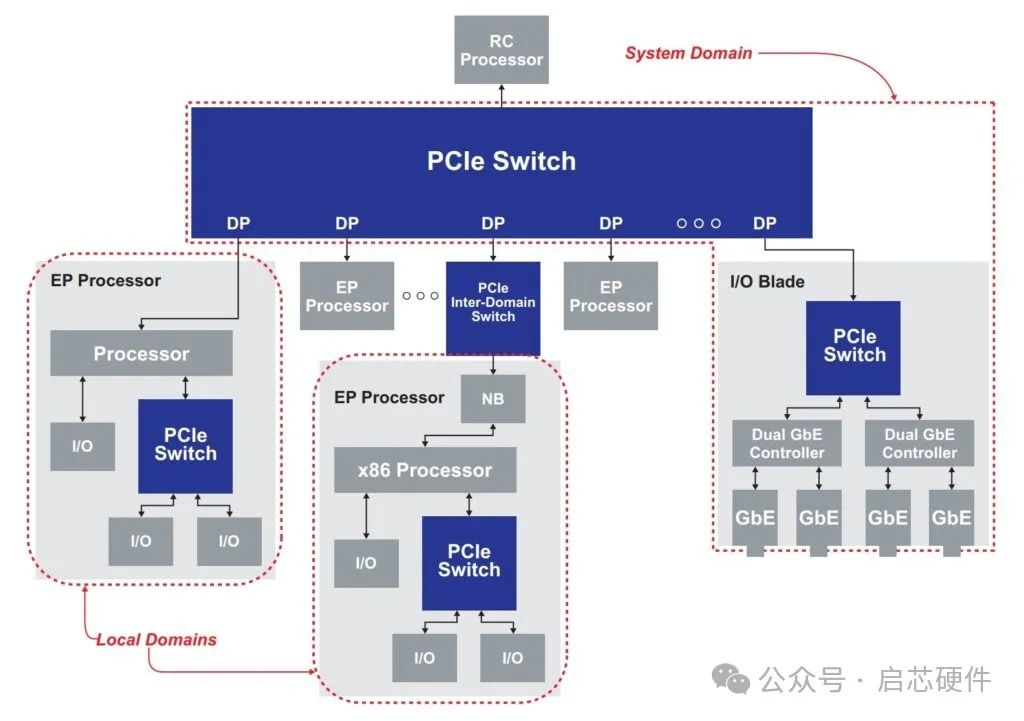

在服务器系统中,主板上的芯片组通常扮演RC模式的角色,负责管理系统中的所有PCIe设备,包括处理器、存储控制器、网卡等。

在嵌入式及PC系统中,处理器内部集成的PCIe控制器可以扮演RC模式的角色,管理系统中的外部设备。

4-EP模式的应用案例

显卡、网卡、存储控制器等外部设备通常扮演EP模式的角色,通过PCIe总线与主机或其他设备进行通信。

在桌面计算机中,显卡通过PCIe总线连接到主板上,以EP模式的角色接收来自主机的请求,并将图形数据传输到显示器上。

在服务器系统中,存储控制器通过PCIe总线连接到主板上,以EP模式的角色接收来自主机或其他设备的数据读写请求,并管理存储设备的访问。

1366

1366

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?