1 普通逻辑的复位

首先说结论,对于Altera的FPGA而言,因为里面的flip-flop只支持低有效的异步复位,所以推荐使用低有效的异步复位。

对于xilinx 7系列的FPGA而言,flip-flop支持高有效的异步复/置位和同步复位/置位。对普通逻辑设计,同步复位和异步复位没有区别,当然由于器件内部信号均为高有效,因此推荐使用高有效的控制信号,最好使用高有效的同步复位。输入复位信号的低有效在顶层放置反相器可以被吸收到IOB中。

下面细说原因

先比较一下同步复位和异步复位的区别:

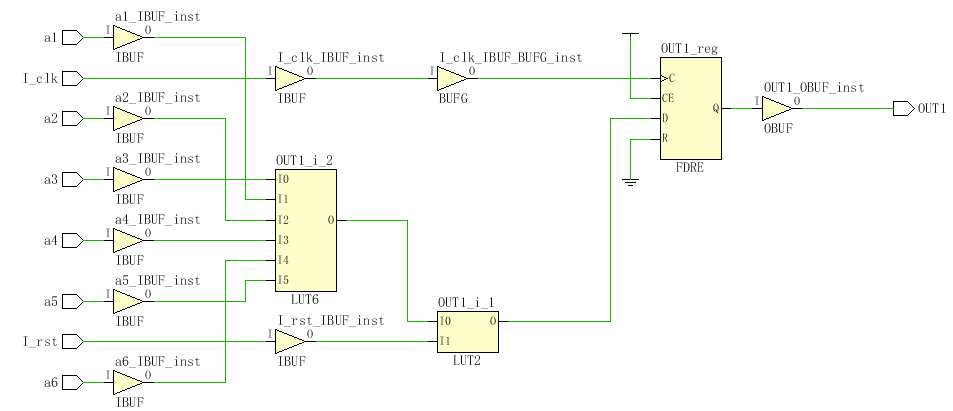

首先是同步复位,同步的控制信号包括同步置位/复位和使能,可以被吸收到LUT中,目的是为了防止控制集不同的LUT不能被综合到同一个slice中,这样虽然提高了了LUT的使用率,却降低了slice的使用率,得不偿失。

控制信号扇出不大于16的情况都可以尽可能的被吸收到同一个slice的LUT中去,在vivado中可以使用control_set_opt_threshold进行设置。

同步复位

always @(posedge I_sys_clk)

begin

if(I_rst)

begin

OUT1 <= 0;

end

else

begin

OUT1 <= &{a1,a2,a3,a4,a5,a6};

end

end

本文探讨了Xilinx 7系列FPGA中同步复位和异步复位的使用,建议优先使用高有效的同步复位,以避免Recovery/Removal风险。同步复位在控制集优化下能有效利用LUT,而异步复位需注意释放沿的时间要求。在处理特殊资源如SRL、LUTRAM、DSP48E1和BRAM时,复位处理方式有所不同,需谨慎处理以确保设计的正确性和效率。

本文探讨了Xilinx 7系列FPGA中同步复位和异步复位的使用,建议优先使用高有效的同步复位,以避免Recovery/Removal风险。同步复位在控制集优化下能有效利用LUT,而异步复位需注意释放沿的时间要求。在处理特殊资源如SRL、LUTRAM、DSP48E1和BRAM时,复位处理方式有所不同,需谨慎处理以确保设计的正确性和效率。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

873

873

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?