MMCM/PLL 的编程必须遵循一套流程,以确保配置的稳定性和性能。本文将描述了如何根据特定的设计要求来编程 MMCM/PLL。设计可以通过两种方式实现:直接通过图形用户界面(Clocking Wizard 时钟向导)或通过实例化来实现 MMCM/PLL。无论选择哪种方法,编程 MMCM/PLL 都需要以下信息:

• 参考时钟周期

• 输出时钟频率(最多七个)

• 输出时钟占空比(默认为 50%)

• 输出时钟相位偏移量(以度数为单位,相对于时钟的原始 0 相位)

• MMCM/PLL 期望的带宽(默认为 OPTIMIZED,软件将选择带宽)

• 补偿模式(由软件自动确定)

• 参考时钟抖动(以 UI 为单位,即参考时钟周期的百分比)

在获得上述信息后,可以按照以下步骤进行编程:

1、确定输入频率

通过使用最小和最大输入频率来确定D计数器的范围,通过VCO工作范围来确定M计数器的范围,以及输出计数器的范围,从而可以计算出所有可能的输出频率。

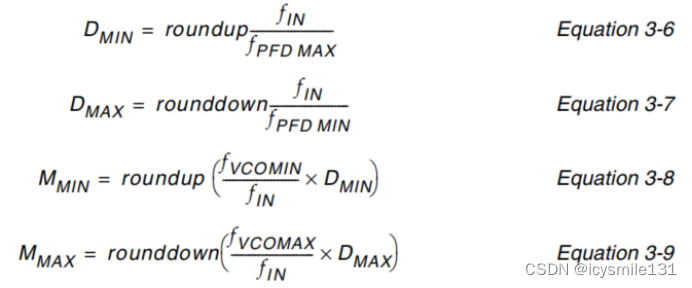

以 FIN = 100 MHz、FVCO = 600 MHz 到 1600 MHz 以及 FPFD = 10 MHz 到 550 MHz 为例。

对于 FPFDMIN = 10 MHz,D 的值只能在 1 到 10 之间。

DMIN(参见公式 3-6)= 1

DMAX(参见公式 3-7)= 10

• 当 D = 1 时,M 的值只能在 6 到 16 之间。

• 当 D = 2 时,M 的值只能在 12 到 32 之间。

• 当 D = 3 时,M 的值只能在 24 到 64 之间。

此外,D = 1 M = 4 是 D = 2 M = 8、D = 4 M = 16 和 D = 8 M = 32 的子集,因此这些情况可以被忽略。在本例中,只考虑 D = 1, 3, 5, 6, 7, 和 9,因为其他 D 值都是这些情况的子集。这大大减少了可能的输出频率数量。

输出频率是依次选择的。应将所需的输出频率与生成的可能输出频率进行比较。一旦确定了第一个输出频率,就可以对 M 和 D 的值施加额外的约束。这可以进一步限制第二个输出频率的可能值。继续这个过程,直到选择所有输出频率。

确定允许的 M 和 D 值的约束条件如下公式所示:

在实际应用中,这些公式和约束条件将用于编程 MMCM/PLL,以生成精确且稳定的输出频率。通过迭代尝试不同的 M 和 D 值组合,并验证它们是否满足所有条件,可以找到满足设计要求的最佳配置。

2、确定M和D的值

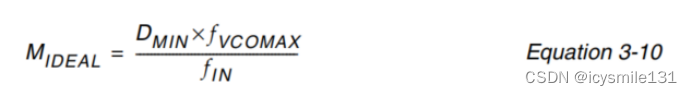

确定输入频率后,可能会得到多个M和D的候选值。下一步是确定最佳的M和D值。首先确定起始的M值。这基于VCO的目标频率,即VCO的理想工作频率。

目标是找到最接近VCO理想工作点的M值。

通常从最小的D值开始这个过程。目标是使D和M的值尽可能小,同时保持ƒVCO(VCO输出频率)尽可能高。

为了找到最佳的M和D值,可以遵循以下步骤:

①确定VCO的理想工作点:查阅VCO的规格文档,了解它的最佳工作频率范围。这个范围通常是VCO性能最优、稳定性最好且功耗较低的频率区间。

②设置初始D值:从最小的D值开始,通常是1。较小的D值有助于保持较高的输出频率,同时减少相位噪声和抖动。

③计算初始M值:使用公式 FVCO = FIN * M / D,将已知的输入频率FIN和初始D值代入,解出M值,使得计算出的FVCO尽可能接近VCO的理想工作点。

④验证M值:确保计算出的M值在允许的范围内,并且不会导致VCO频率超出其规格范围。

⑤检查输出频率:使用相同的公式计算输出频率FPFD,验证它是否满足系统的要求。如果不满足,需要调整M和D的值。

⑥迭代优化:如果初始的M和D值不满足所有要求,尝试增加D的值(同时相应地调整M值以保持FVCO接近理想工作点),然后重新计算输出频率FPFD。重复这个过程,直到找到满足所有约束条件的M和D值组合。

3、MMCM时钟输入信号

MMCM的可能时钟源包括:

• IBUFG - 时钟功能输入缓冲器,MMCM将补偿此路径的延迟。IBUFG代表同一区域内的时钟功能时钟引脚。

• BUFGCTRL 或 BUFG - 内部全局时钟缓冲器,MMCM不会补偿此路径的延迟。

• IBUF - 常规输入缓冲器,不推荐使用,因为输入缓冲器可以使用通用路由。IBUF时钟输入必须在路由到MMCM/PLL之前先路由到BUFG。MMCM/PLL不会补偿此路径的延迟。

• BUFR - 区域时钟输入缓冲器,MMCM/PLL不会补偿此路径的延迟。

• GT - 千兆收发器可以直接连接到MMCM。

这些时钟源提供了多种方式来将外部或内部生成的时钟信号连接到MMCM。在选择时钟源时需要考虑延迟、抖动、功耗和其他相关因素。

值得注意的是,对于某些时钟源(如IBUF),可能需要先通过BUFG进行缓冲,然后再连接到MMCM/PLL。这是因为MMCM/PLL可能不会补偿通过某些路径引入的延迟。

1427

1427

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?