FPGA 是现场可编程门阵列的缩写,它是在PAL,GAL 及 EPLD 等可编程器件的基础上发展起来的。FPGA 具有速度快、密度高、功耗小的特点。采用 FPGA 芯片进行专用集成电路设计,既可以解决定制电路缺乏灵活性的不足,又可以通过相关的软硬件环境掌握芯片的最终功能,提高一次设计的成功率,所以,目前 FPGA 在电子设计中已被广泛使用。同时,由于 FPGA 经常要和外部存储器及 CPU 进行数据输入输出交换,而利用双向端口的设计来进行数据交换可以成倍地节省各自的引脚资源。

双向端口顾名思义是一种既可以作为输入端口接收数据,也可以作为输出端口发出数据,它对数据的操作是双向的。比如某个设计需要一个 16 位的数据输入口和一个16 位的数据输出口,并且数据输入和输出不会同时发生。如果数据输入口和输出口分别设计则需要32根数据线,而用双向端口来设计,则只需要16 根数据线,这样就节省了16 根数据线引脚。由于现在的大多数资料对双向端口的设计介绍很少,本文给出 FPGA 中双向端口的设计原理和方法,以及仿真和初始化双向端口的方法,同时选用Xilinx的Spartan2E 芯片进行实际应用。

1、 FPGA 中双向端口的设计原理和Verilog硬件语言程序设计

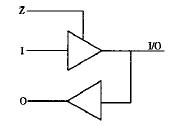

首先介绍双向端口在 FPGA 内部硬件资源是怎样实现的。在 FPGA 中它是通过对三态门控制来实现双向端口的,比如在 Xilinx 的Spartan2E 中的图例(如图1 所示):

图1 双向端口的硬件图

当z=0 时,上面输出的管子开通,此时数据可以从上面的管子中输出,这时双向端口就作为输出口;当z=1 时,上面的管子被置为高阻态,数据不能从上面的管子输出,此时数据只可以从下面的管子由外向内输入,这时的双向端口是输入口。限于篇幅,我们做一个简单的模型来说明双向端口的设计。下面我们用 Verilog 硬件语言进行双向端口的程序设计,为了看

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

425

425

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?