1、前言

PCI 设备都有独立的配置空间, HOST 主桥通过配置读写总线事务访问这段空间。 PCI总线规定了三种类型的 PCI 配置空间, 分别PCI Agent 设备使用的配置空间, PCI 桥使用的配置空间和 Cardbus 桥片使用的配置空间。在一个具体的处理器应用中, PCI 设备通常将 PCI 配置信息存放在 E2PROM 中。 PCI 设备进行上电初始化时, 将 E2PROM 中的信息读到 PCI 设备的配置空间中作为初始值。 这个

过程由硬件逻辑完成, 绝大多数 PCI 设备使用这种方式初始化其配置空间。

2、PCIE配置空间

PCIE配置空间是每个PCIe设备的一段独立空间,系统通过访问这段空间可以获取设备的信息并进行配置。配置空间的结构包括头标区和设备相关区,配置头长度为64字节,包含用于唯一识别设备的字段;剩余的字节则因设备而异,用于描述设备的特定功能。

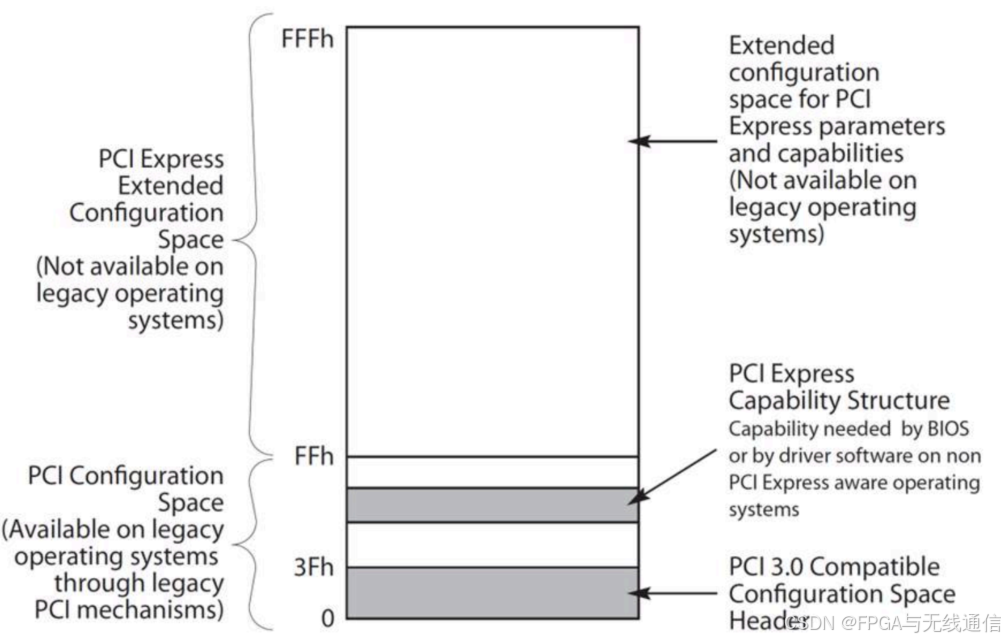

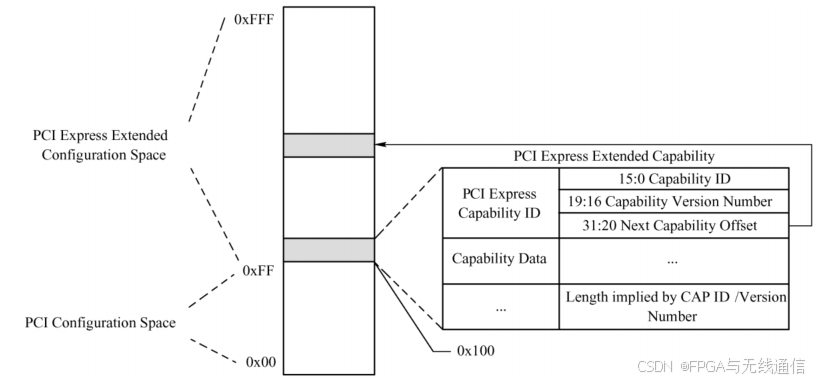

PCI设备配置空间为256字节,PCIE设备的配置空间为4K字节,两种设备配置头均为64字节,但由于PCIE设备的功能更强大,需要更多扩展

空间来描述其特定功能,又为了兼容PCI,PCIE扩展了地址0x100~0xfff用于PCIE扩展配置空间

在每次启动时,PCIe设备的配置空间地址一般有BOIS分配,分配完成后主设备系统启动后可扫描PCIe设备的配置空间,获取PCIe设备并完成PCIE相关配置。

PCI及PCIE配置空间分配如下图所示

2.1、PCIE配置头

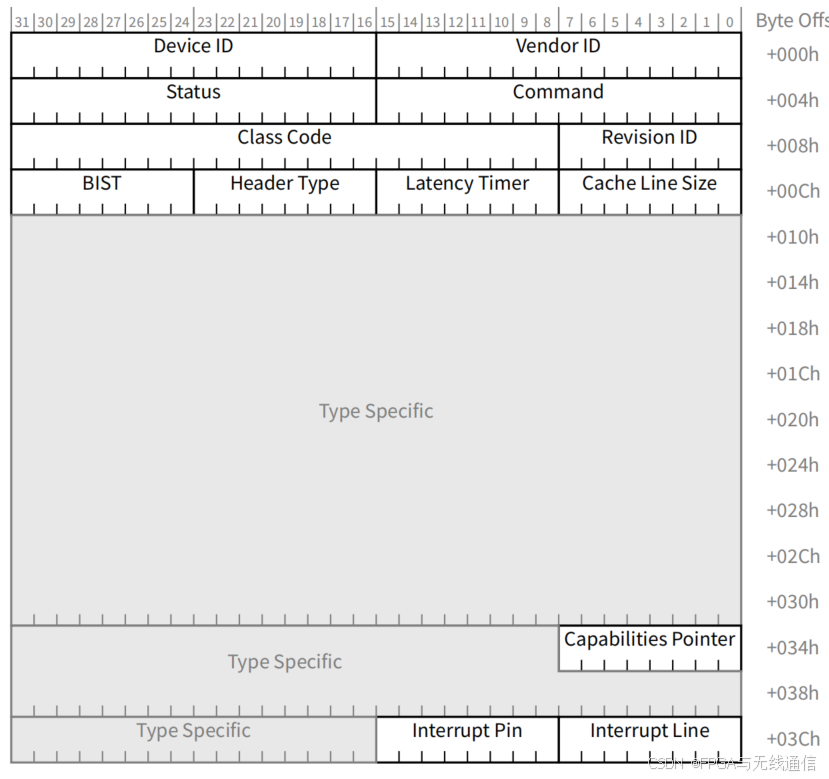

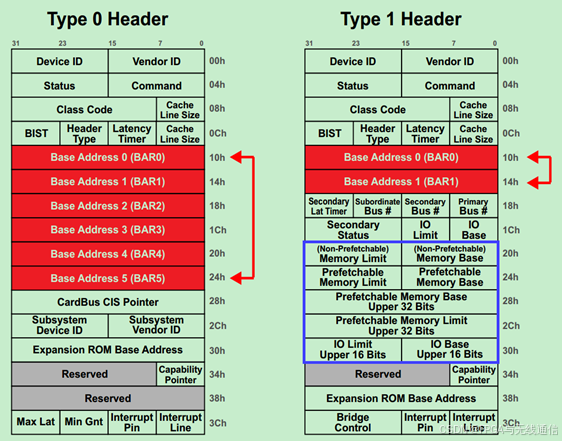

PCIE 64字节的配置头分为两种,Type0和Type1,Type0用于描述PCIE Endpoint,Type1用于描述PCIE Bridge或者Switch。

Type1/Type0 PCIE头部分空间配置相同,如下图所示,灰色部分为不同处,白色部分为相同处。

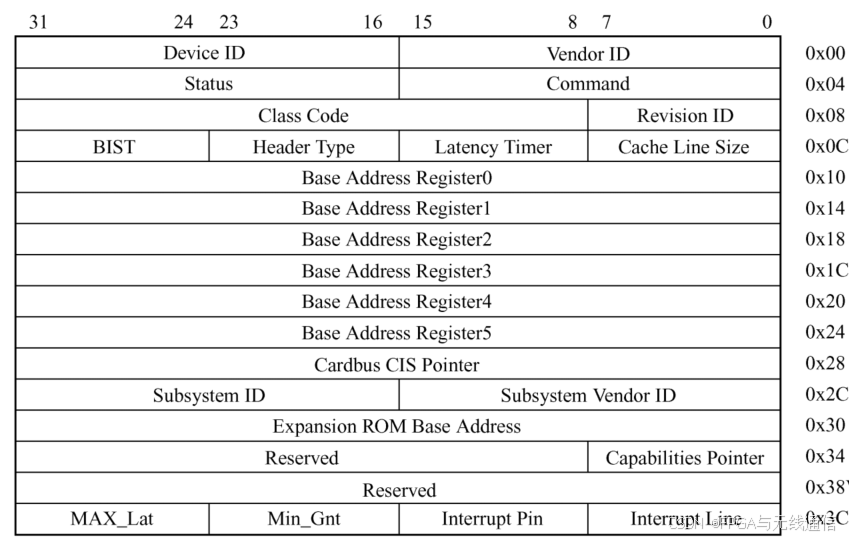

PCIE Type0配置头如下图所示:

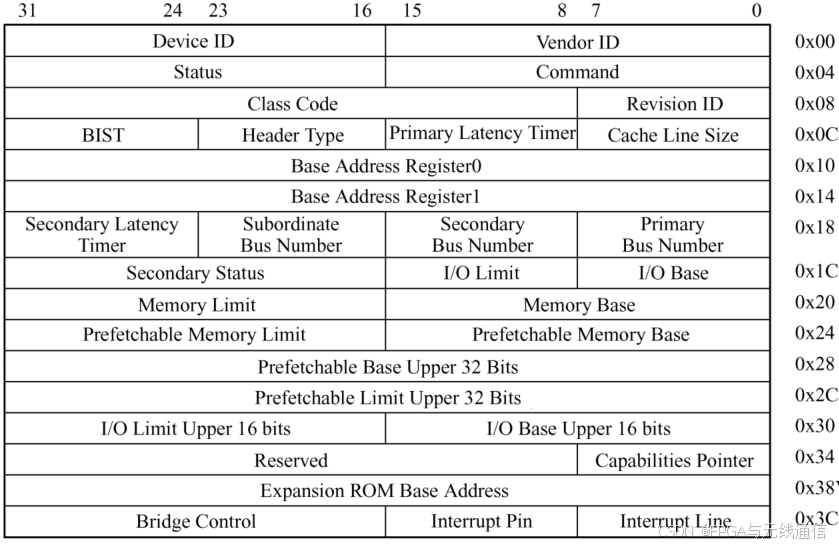

PCIE Type1配置头如下图所示:

Type0/1相同配置寄存器说明:

(1) Device ID 和 Vendor ID 寄存器

这两个寄存器的值由 PCISIG 分配, 只读。 其中 Vendor ID 代表 PCI 设备的生产厂商, 而Device ID 代表这个厂商所生产的具体设备。

(2) Revision ID 和 Class Code 寄存器

这两个寄存器只读。 其中 Revision ID 寄存器记载 PCI 设备的版本号。 该寄存器可以被认为是 Device ID 寄存器的扩展。

而 Class Code 寄存器记载 PCI 设备的分类, 该寄存器由三个字段组成, 分别是 Base Class Code、 Sub Class Code 和 Interface。 其中Base Class Code 将 PCI 设备分类为显卡、 网卡、PCI 桥等设备; Sub Class Code 对这些设备进一步细分; 而 Interface 定义编程接口。 ClassCode 寄存器可供系统软件识别当前 PCI 设备的分类。

除此之外硬件逻辑设计也需要使用该寄存器识别不同的设备。 当 Base Class Code 寄存器为 0x06, Sub Class Code 寄存器为 0x04 时, 如果 Interface 寄存器为 0x00, 表示当前 PCI 设备为一个标准的 PCI 桥; 如果 Interface 寄存器为0x01, 表示当前 PCI 设备为一个使用 “负向译码” 的 PCI 桥。

硬件逻辑需要根据这些寄存器判断当前 PCI 桥的使用方式, 许多 PCI 桥既可以支持 “正向” 译码, 也可以支持 “负向” 译码, 系统软件必须合理设置 Class Code 寄存器。

(3) Header Type 寄存器

该寄存器只读, 由 8 位组成。

● 第 7 位为 1 表示当前 PCI 设备是多功能设备, 为 0 表示为单功能设备。

● 第 6 ~ 0 位表示当前配置空间的类型, 为 0 表示该设备使用 PCI Agent 设备的配置空间, 普通 PCI 设备都使用这种配置头; 为 1 表示使用 PCI 桥的配置空间, PCI 桥使用这种配置头; 为 2 表示使用 Cardbus 桥片的配置空间, Card Bus 桥片使用这种配置头。

(4) Cache Line Size 寄存器

该寄存器记录 HOST 处理器使用的 Cache 行长度。 在 PCI 总线中和 Cache 相关的总线事务, 如存储器写并无效和 Cache 多行读等总线事务需要使用这个寄存器。 值得注意的是, 该寄存器由系统软件设置, 但是在 PCI 设备的运行过程中, 只有其硬件逻辑才会使用该寄存

器, 比如 PCI 设备的硬件逻辑需要得知处理器系统 Cache 行的大小, 才能进行存储器写并无效总线事务, 单行读和多行读总线事务。如果 PCI 设备不支持与 Cache 相关的总线事务, 系统软件可以不设置该寄存器, 此时该寄存器为初始值 0x00。 对于 PCIe 设备, 该寄存器的值无意义, 因为 PCIe 设备在进行数据传送时, 在其报文中含有一次数据传送的大小, PCIe 总线控制器可以使用这个 “大小” , 判断

数据区域与 Cache 行的对应关系。

(7) Capabilities Pointer 寄存器

在 PCI 设备中, 该寄存器是可选的, 但是在 PCI⁃X 和 PCIe 设备中必须支持这个寄存器,Capabilities Pointer 寄存器存放 Capabilities 寄器组的基地址, PCI 设备使用 Capabilities 寄存器组存放一些与 PCI 设备相关的扩展配置信息。 该组寄存器的详细说明见第 4. 3 节。

(8) Interrupt Line 寄存器

这个寄存器是系统软件对 PCI 设备进行配置时写入的, 该寄存器记录当前 PCI 设备使用的中断向量号, 设备驱动程序可以通过这个寄存器, 判断当前 PCI 设备使用处理器系统中的哪个中断向量号, 并将驱动程序的中断服务例程注册到操作系统中。

Type0其他配置寄存器说明:

(1) Base Address Register 0 ~ 5 寄存器

该组寄存器简称为 BAR 寄存器, BAR 寄存器保存 PCI 设备使用的地址空间的基地址,该基地址保存的是该设备在 PCI 总线域中的地址。 其中每一个设备最多可以有 6 个基址空间, 但多数设备不会使用这么多组地址空间。具体参照第三章。

(2) Subsystem ID 和 Subsystem Vendor ID 寄存器

这两个寄存器和 Device ID 及 Vendor ID 类似, 也是记录 PCI 设备的生产厂商和设备名称。 但是这两个寄存器和 Device ID 及 Vendor ID 寄存器略有不同。 下面以一个实例说明Subsystem ID 和 Subsystem Vendor ID 的用途。Xilinx 公司在 FGPA 中集成了一个 PCIe 总线接的 IP 核, 即 LogiCORE。 用户可以使用LogiCORE 设计各种各样基于 PCIe 总线的设备, 但是这些设备的 Device ID 都是 0x10EE, 而

Vendor ID 为 0x0007。因此仅使用 Device ID 和 Vendor ID 寄存器无法区分这些设备。 此时必须使用 SubsystemID 和 Subsystem Vendor ID。 如果 Intel 也使用 LogiCORE 设计一款网卡适配器, 那么这个基于LogiCORE 的网卡适配器的 Subsystem Vendor ID 寄存器0x8086, 而 Subsystem ID 寄存器将是 0x10xx。

(3) Expansion ROM base address 寄存器

有些 PCI 设备在处理器还没有运行操作系统之前, 就需要完成基本的初始化设置, 比如显卡、 键盘和硬盘等设备。 为了实现这个 “预先行” 功能, PCI 设备需要提供一段 ROM程序, 而处理器在初始化过程中将运行这段 ROM 程序, 初始化这些 PCI 设备。 Expansion ROM base address 记载这段 ROM 程序的基地址。

Type1其他配置寄存器说明:

(1) Subordinate Bus Number、 Secondary Bus Number 和 Primary Bus Number 寄存器PCI 桥可以管理其下的 PCI 总线子树。 其中 Subordinate Bus Number 寄存器存放当前 PCI子树中, 编号最大的 PCI 总线号。 而 Secondary Bus Number 寄存器存放当前 PCI 桥 SecondaryBus 使用的总线号, 这个 PCI 总线号也是该 PCI 桥管理的 PCI 子树中编号最小的 PCI 总线号。因此一个 PCI 桥能够管理的 PCI 总线号在 Secondary Bus Number ~ Subordinate Bus Number 之间。 这两个寄存器的值由系统软件遍历 PCI 总线树时设置。Primary Bus Number 寄存器存放该 PCI 桥上游的 PCI 总线号, 该寄存器可读写。 Primary Bus Number、 Subordinate Bus Number 和 Secondary Bus Number 寄存器在初始化时必须为 0,系统软件将根据这几个寄存器是否为 0, 判断 PCI 桥是否被配置过。

(2) Secondary Status 寄存器

该寄存器的含义与 PCI Agent 配置空间的 Status 寄存器的含义相近, PCI 桥的 Secondary Status 寄存器记录 Secondary Bus 的状态, 而不是 PCI 桥作为 PCI 设备时使用的状态。 在 PCI 桥配置空间中还存在一个 Status 寄存器, 该寄存器保存 PCI 桥作为 PCI 设备时的状态。

(3) Secondary Latency Timer 寄存器

该寄存器的含义与 PCI Agent 配置空间的 Latency Timer 寄存器的含义相近, PCI 桥的Secondary Latency Timer 寄存器管理 Secondary Bus 的超时机制, 即 PCI 桥发向下游的总线事务; 在 PCI 桥配置空间中还存在一个 Latency Timer 寄存器, 该寄存器管理 PCI 桥发向上游的总线事务。

(4) I / O Limit 和 I / O Base 寄存器

在 PCI 桥管理的 PCI 子树中包含许多 PCI 设备, 而这些 PCI 设备可能会使用 I / O 地址空间。 PCI 桥使用这两个寄存器, 存放 PCI 子树中所有设备使用的 I / O 地址空间集合的基地址和大小。

(5) Memory Limit 和 Memory Base 寄存器

在 PCI 桥管理的 PCI 子树中有许多 PCI 设备, 这些 PCI 设备可能会使用存储器地址空间。 这两个寄存器存放所有这些 PCI 设备使用的存储器地址空间集合的基地址和大小, PCI桥规定这个空间的大小至少为 1MB。

(6) Prefetchable Memory Limit 和 Prefetchable Memory Base 寄存器

在 PCI 桥管理的 PCI 子树中有许多 PCI 设备, 如果这些 PCI 设备支持预读, 则需要从PCI 桥的可预读空间中获取地址空间。 PCI 桥的这两个寄存器存放这些 PCI 设备使用的可预取存储器空间的基地址和大小。如果 PCI 桥不支持预读, 则其下支持预读的 PCI 设备需要从 Memory Base 寄存器为基地址的存储器空间中获取地址空间。 如果 PCI 桥支持预读, 其下的 PCI 设备需要根据情况, 决定使用可预读空间还是不可预读空间。 PCI 总线建议 PCI 设备支持预读, 但是支持预读的

PCI 设备并不多见。

(7) I / O Base Upper 16 Bits and I / O Limit Upper 16 寄存器

如果 PCI 桥仅支持 16 位的 I / O 端口, 这组寄存器只读, 且其值为 0。 如果 PCI 桥支持32 位 I / O 端口, 这组寄存器可以提供 I / O 端口的高 16 位地址。

(8) Bridge Control Register

该寄存器用来管理 PCI 桥的 Secondary Bus, 其主要位的描述如下。

● Secondary Bus Reset 位, 第 6 位, 可读写。 当该位为 1 时, 将使用下游总线提供的RST#信号复位与 PCI 桥的下游总线连接的 PCI 设备。 通常情况下与 PCI 桥下游总线连接的 PCI 设备, 其复位信号需要与 PCI 桥提供的 RST#信号连接, 而不能与 HOST 主桥提供的RST#信号连接。

● Primary Discard Timer 位, 第 8 位, 可读写。 PCI 桥支持 Delayed 传送方式, 当 PCI 桥的 Primary 总线上的主设备使用 Delayed 方式进行数据传递时, PCI 桥使用 Retry 周期结束 Primary 总线的 Non⁃Posted 数据请求, 并将这个 Non⁃Posted 数据请求转换为 De⁃layed 数据请求, 之后主设备需要择时重试相同的 Non⁃Posted 数据请求。 当该位为 1时, 表示在 Primary Bus 上的主设备需要在 2-10个时钟周期之内重试这个数据请求, 为0 时, 表示主设备需要在 2-15个时钟周期之内重试这个数据请求, 否则 PCI 桥将丢弃Delayed 数据请求。

● Secondary Discard Timer 位, 第 9 位, 可读写。 当该位为 1 时, 表示在 Secondary Bus上的主设备需要在 2-10个时钟周期之内重试这个数据请求, 为 0 时, 表示主设备需要在 2-15个时钟周期之内重试这个数据请求, 如果主设备在规定的时间内没有进行重试时, PCI 桥将丢弃 Delayed 数据请求。

2.1、PCIE扩展配置空间

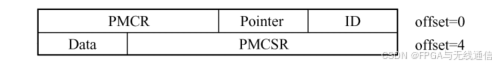

(1)Power Management Capability

PCIe 总线使用的软件电源管理机制与 PCI PM ( Power Management) 兼容。 而 PCI 总线的电源管理机制需要使用 Power Management Capability 结构, 该结构由一些和 PCI / PCI⁃X 和PCIe 总线的电源管理相关的寄存器组成, 包括 PMCR ( Power Management Capabilities Regis⁃ter) 和 PMCSR (Power Management Control and Status Register) , 其结构如下图 所示

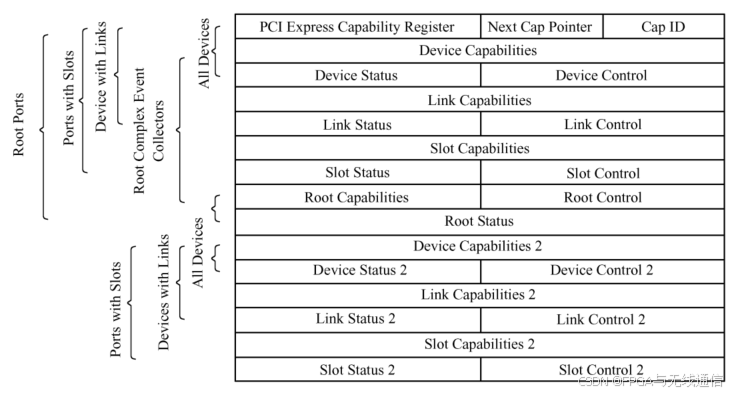

(2)PCI Express Capability

PCI Express Capability 结构存放一些和 PCIe 总线相关的信息, 包括 PCIe 链路和插槽的信息。 有些 PCIe 设备不一定实现了 PCI Express Capability 结构中的所有寄存器, 或者并没有提供这些配置寄存器供系统软件访问。PCI Express Capability 结构的部分寄存器及其相应字段与硬件的具体实现细节相关, 本节仅介绍其中一些系统软件程序员需要了解的字段。 在该结构中, Cap ID 字段为 PCI Ex⁃presss Capability 结构使用的 ID 号, 其值为 0x10。 而 Next Capability 字段存放下一个 Capabili⁃ty 寄存器的地址。 PCI Express Capability 结构由 PCI Express Capability、 Device Capability、Device Control、 Device Status、 Link Capabilities、 Link Status、 Link Control、 Slot Capabilities 和Slot Status 等一系列寄存器组成。 本节仅介绍该结构中常用的寄存器。 PCI Express Capability的组成结构如下图 所示。

(3)PCI Express Extended Capabilities

PCI Express Extended Capabilities 结构存放在 PCI 配置空间 0x100 之后的位置, 该结构是PCIe 设备独有的, PCI 设备并不支持该结构。 实际上绝大多数 PCIe 设备也并不支持该结构。在一个 PCIe 设备中可能含有多个 PCI Express Extended Capabilities 结构, 并形成一个单向链表, 其中第一个 Capability 结构的基地址为 0x100, 其结构如下所示。

在这个单向链表的尾部, 其 Next Capability Offset、 Capability ID 和 Capbility Version 字段的值都为 0。 如果在 PCIe 设备中不含有 PCI Express Extended Capabilities 结构, 则 0x100 指针所指向的结构, 其 Capability ID 字段为 0xFFFF, 而 Next Capability Offset 字段为 0x0。

3、PCIE BAR

如前面描述,PCIE配置空间中不同type下的BAR配置空间不同,Type0有6个可配置BAR空间,Type1有2个可配置BAR空间。

BAR空间实际就是PCIE设备和RC进行内存空间配置的交互寄存器,RC可以通过读写配置空间中BAR的位置获取PCIE设备地址空间的大小和个数,同时根据内存分配将PCIE设备映射到CPU的基地址配置到BAR空间中。

BAR可分为以下三类:

(1)32位内存空间:支持4GB以下地址范围

(3)64位内存空间:支持更大地址范围,需占用两个BAR寄存器(高位BAR与低位BAR联合使用)

(3)I/O空间:较少使用,仅支持32位地址

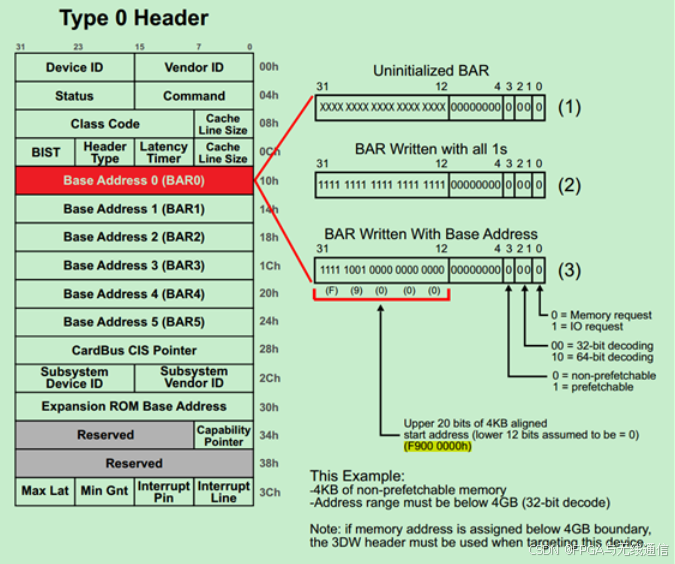

PCIE 32bit内存空间初始化流程:

(1)PCIE设备硬件初始化将未使用bar空间数据填0,如使用BAR空间为大小2^n,将BAR空间中n-1~4bit填0, 31 ~ n bit设置为高阻(RC可写),bit3 ~ 0填为0,表示 32bit内存空间,不预取。

(2)RC通过配置空间配置BAR地址值全为1;

(3)RC回读BAR空间的值,则可通过回读BAR空间的值中第一个不为1的bit确定BAR空间大小(如下图中确定空间为4K),同时可以通过bit3-0确定BAR空间类型

(4)CPU给PCIE 设备分配内存,并将映射到PCIE设备的内存地址基地址填写到31-n bit,后RC即可采用该基地址访问PCIE设备,PCIE设备收到TLP包中基地址与BAR空间地址匹配,则相应TLP包请求

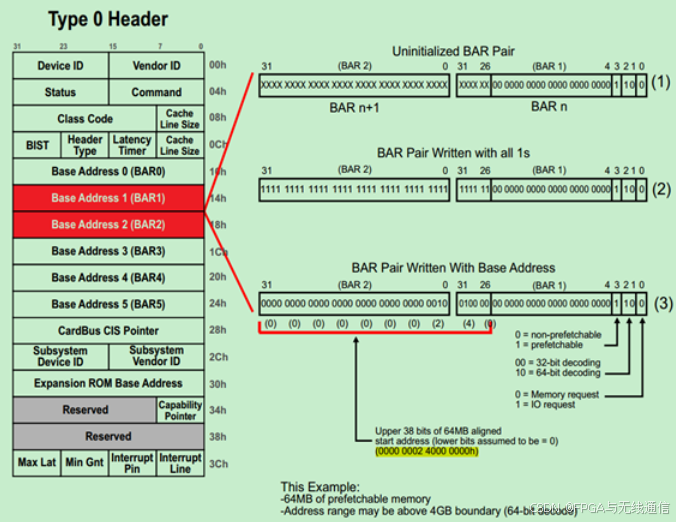

PCIE 64bit内存空间初始化流程:

PCIE 64bit内存空间初始化流程和PCIE 32bit内存空间初始化流程相似,但一个 64bit内存空间配置需要2个BAR空间,具体如下:

(1)PCIE设备硬件初始化将未使用bar空间数据填0,如使用BAR空间大小为2^n,将BAR空间中n-1~4bit填0, 31-n bit设置为高阻(RC可写),bit3-0填为0xC,表示 64bit内存空间,预取打开。下一个BAR 31-0 bit设置为高阻(RC可写,用于高32bit地址)

(2)RC通过配置空间配置BAR地址值全为1;

(3)RC回读BAR空间的值,则可通过回读BAR空间的值中第一个不为1的bit和通过bit3-0确定BAR空间类型从而确定BAR空间大小(如下图中确定空间为64MB)

(4)CPU给PCIE 设备分配内存,并将映射到PCIE设备的内存地址基地址填写到63-n bit(如下图高位存放于BAR2,低位存放于BAR1),后RC即可采用该基地址访问PCIE设备,PCIE设备收到TLP包中基地址与BAR空间地址匹配,则相应TLP包请求

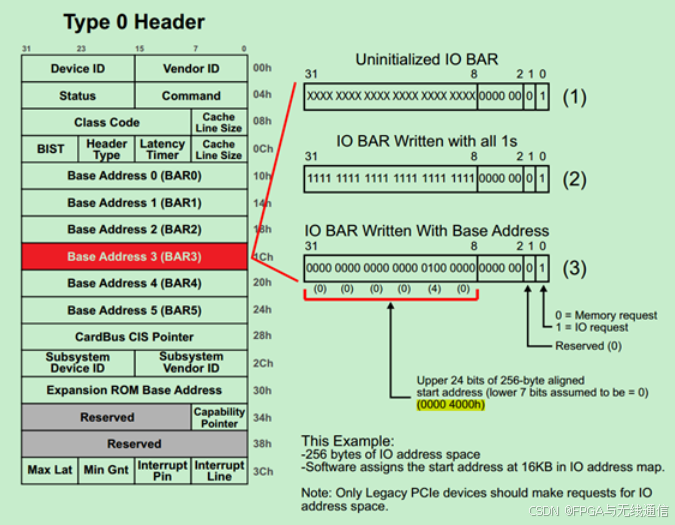

PCIE I/O空间空间初始化流程:

(1)PCIE设备硬件初始化将未使用bar空间数据填0,如使用BAR空间大小为2^n,将BAR空间中n-1~1bit填0, 31-n bit设置为高阻(RC可写),bit0填为0x1,表示IO内存空间

(2)RC通过配置空间配置BAR地址值全为1;

(3)RC回读BAR空间的值,则可通过回读BAR空间的值中第一个不为1的bit和通过bit1确定BAR空间类型从而确定BAR空间大小(如下图中确定空间为256)

(4)CPU给PCIE 设备分配内存,并将映射到PCIE设备的内存地址基地址填写到31-n bit,后RC即可采用该基地址访问PCIE设备,PCIE设备收到TLP包中基地址与BAR空间地址匹配,则相应TLP包请求。

490

490

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?