概念(sequential logic)

时序逻辑:任意时刻输出不仅与当前时刻的输入,而且还取决于电路原来的状态。

与组合逻辑不同,时序逻辑有时钟信号,复位信号

类型

①触发器

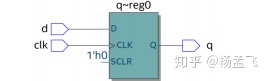

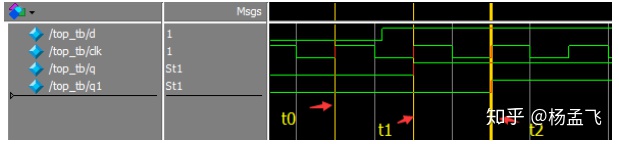

always @(posedge clk) begin // 通过时钟的上升沿进行赋值

q<=d;

end

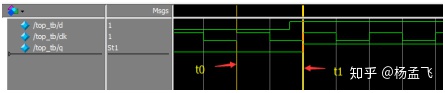

②两级触发器

always @(posedge clk) begin

q<=d;

end

always @(posedge clk)begin

q1<=q;

end

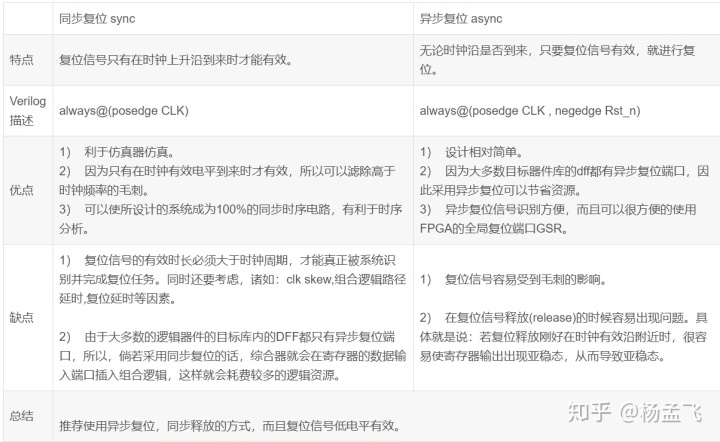

③带异步复位的D触发器 独立于时钟,异步复位信号有效,就会触发复位操作。 用于给信号复位,初始化

module test(d,q,clk,rst);

input d;

input clk;

input rst;

output reg q;

//时钟上升沿,复位下降沿为敏感列表,low active reset

always@(posedge clk or negedge rst)begin

if(rst==0)

q<=0;

else

q<=d;

end

endmodule

仿真代码

module vtf_test_tb();

reg d;

reg clk;

reg rst;

wire q;

initial begin

d=0;

clk=0;

forever begin

#({$random}%100) d=~d;

end

end

initial begin

rst=0;

#150

rst=1;

end

always #10 clk=~clk;

test t0(

.d(d),

.clk(clk),

.rst(rst),

.q(q)

);

endmodule

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?