一 、使用的工具:

vivado 2021.2及其配套的软件

二、使用到的ip

1、video in to axi4_stream ip

2、两个vdma IP

3、zynq ip

4、axi4_stream to video out ip

5、vtc ip

三、注意点

这里使用的ps测ddr。这里输入输出的是vesa标准的1080P视频内容.

这里的视频是4lane的,即一个时钟有4个像素。

转载:video进出VDMA+读写ddr验证_hhh_fpga的博客-CSDN博客

四、设计思想

五、BD设计

六、vitis代码中vdma的设计:因为此设计只需要编写vdma的代码就可以了。

Xil_Out32((VDMA_BASEADDR0 + 0x030), 0x03);//使能循环模式

Xil_Out32((VDMA_BASEADDR0 + 0x0AC), VIDEO_BASEADDR0);//帧存0地址

Xil_Out32((VDMA_BASEADDR0 + 0x0B0), VIDEO_BASEADDR1);//帧存1地址

Xil_Out32((VDMA_BASEADDR0 + 0x0B4), VIDEO_BASEADDR2);//帧存2地址

Xil_Out32((VDMA_BASEADDR0 + 0x0A8), (H_STRIDE*3)); //跨度设置(1920 * 3) bytes

Xil_Out32((VDMA_BASEADDR0 + 0x0A4), (H_ACTIVE*3)); //行宽设置(1920* 3) bytes

Xil_Out32((VDMA_BASEADDR0 + 0x0A0), V_ACTIVE); //行数设置(1080)

/*****************从 DDR 读数据设置**********************/

Xil_Out32((VDMA_BASEADDR1 + 0x000), 0x03); // enable circular mode

Xil_Out32((VDMA_BASEADDR1 + 0x05c), VIDEO_BASEADDR0); // start address

Xil_Out32((VDMA_BASEADDR1 + 0x060), VIDEO_BASEADDR1); // start address

Xil_Out32((VDMA_BASEADDR1 + 0x064), VIDEO_BASEADDR2); // start address

Xil_Out32((VDMA_BASEADDR1 + 0x058), (H_STRIDE*3)); // h offset (1920 * 3) bytes

Xil_Out32((VDMA_BASEADDR1 + 0x054), (H_ACTIVE*3)); // h size (1920 * 3) bytes

Xil_Out32((VDMA_BASEADDR1 + 0x050), V_ACTIVE); // v size (1080)

七、各ip的设置:

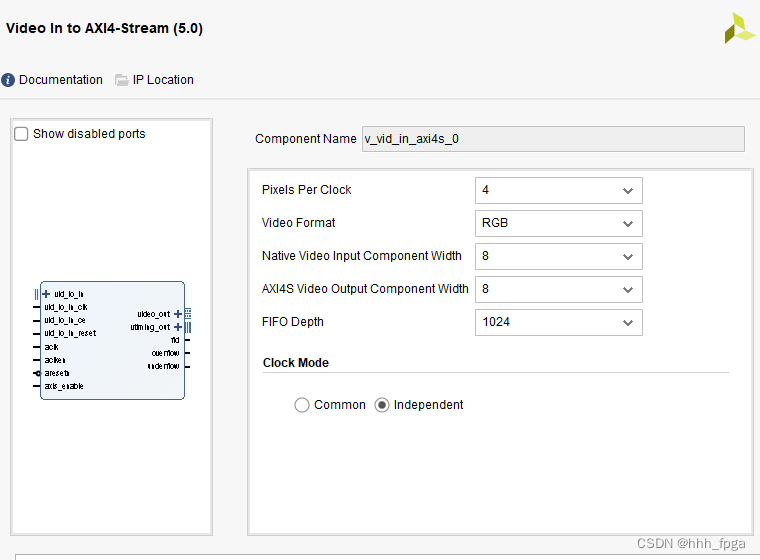

Video in to AXI4-stream:

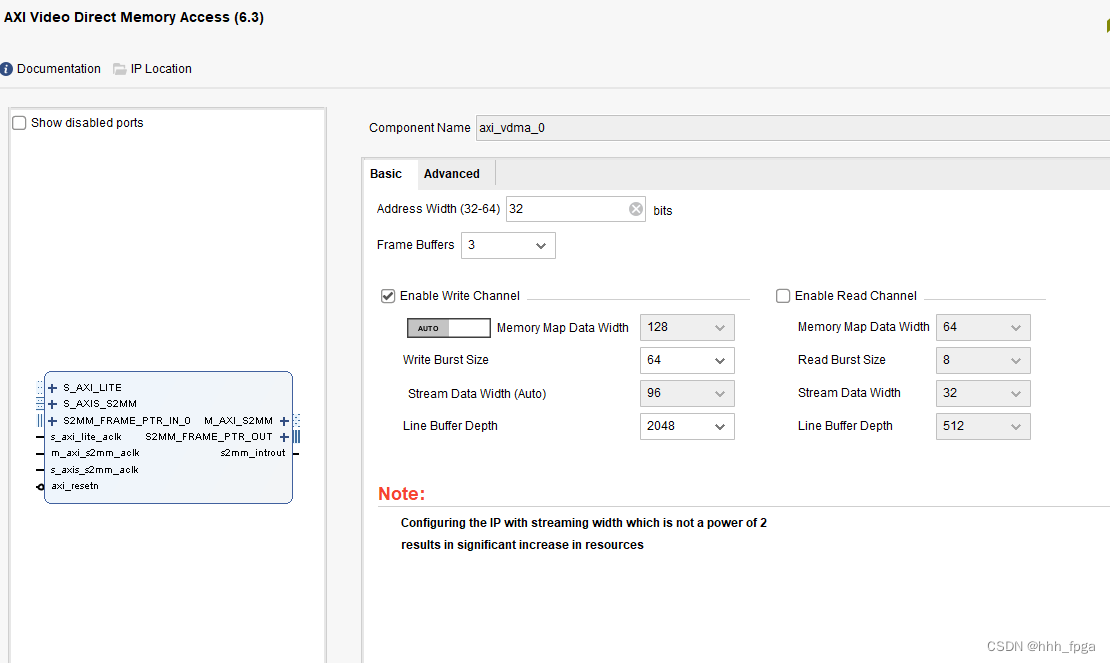

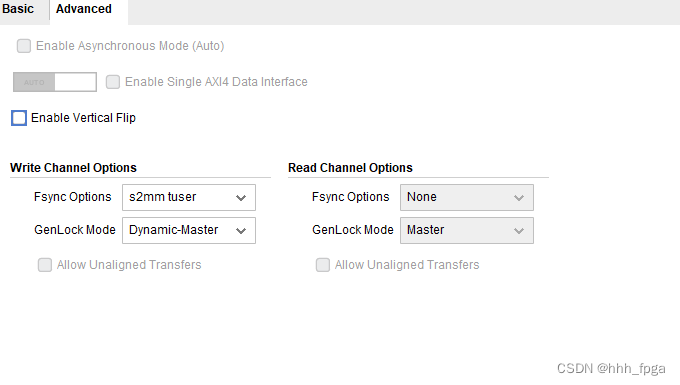

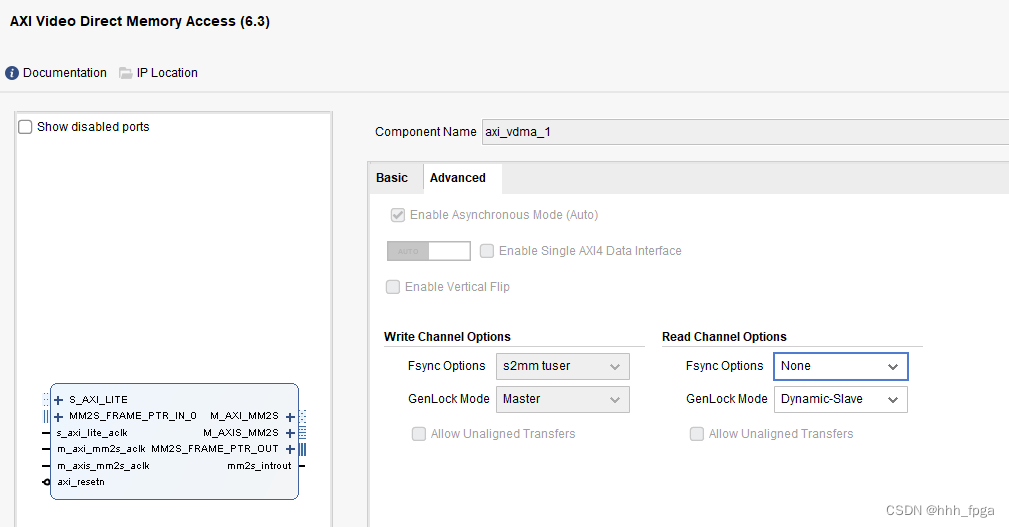

VDMA:写

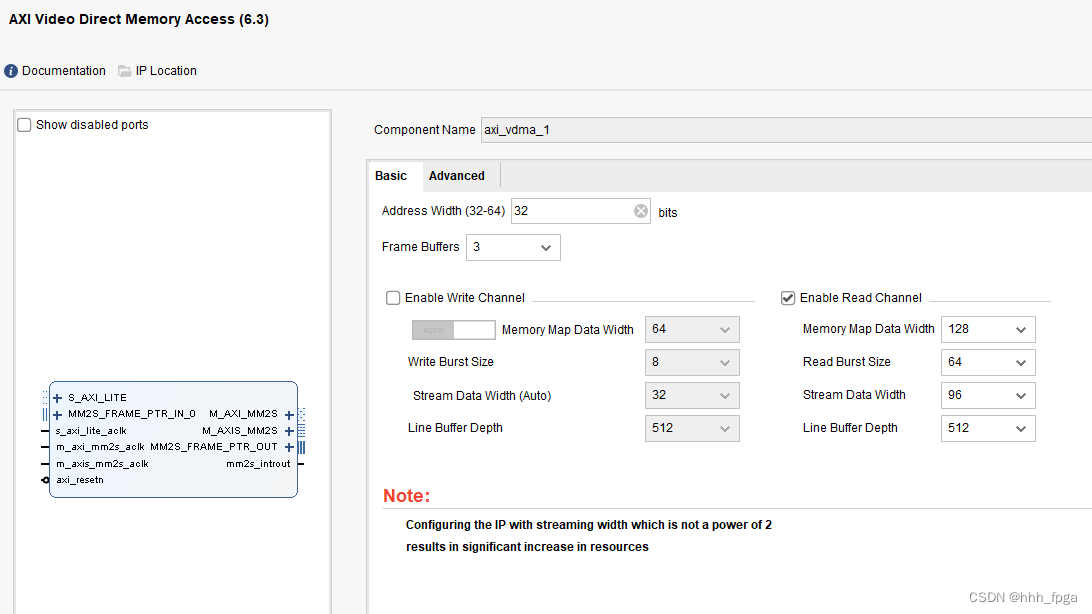

VDMA:读

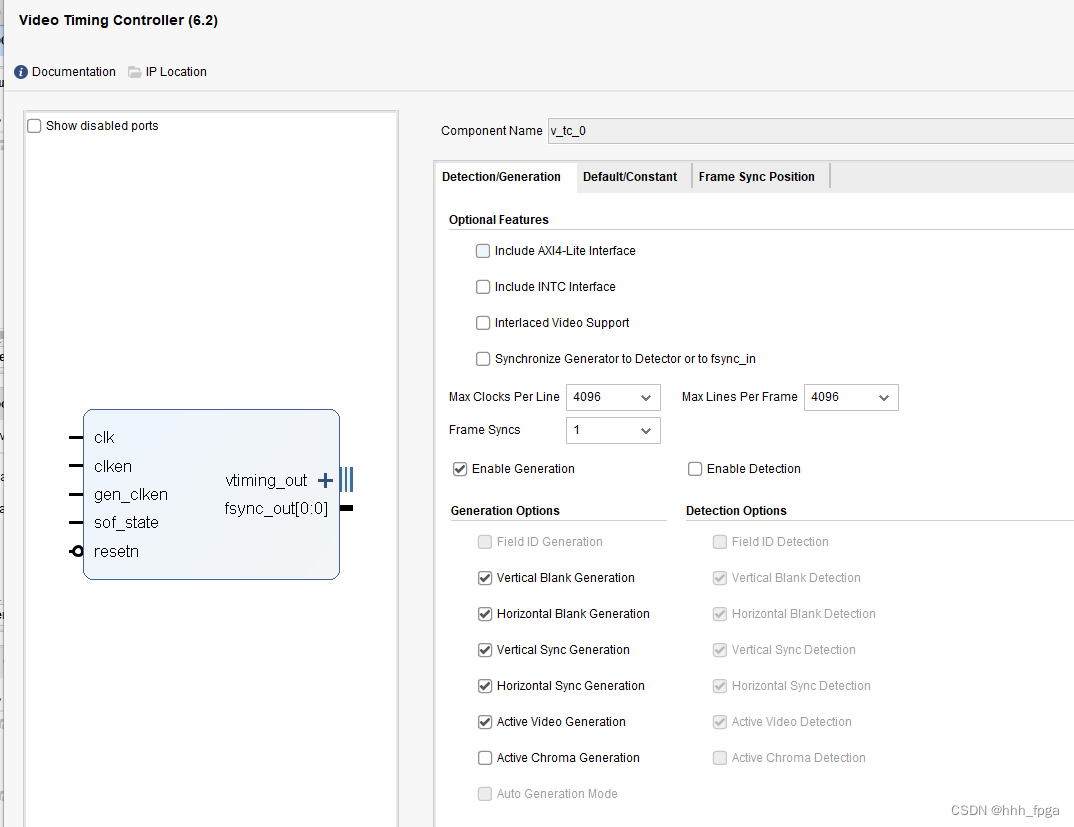

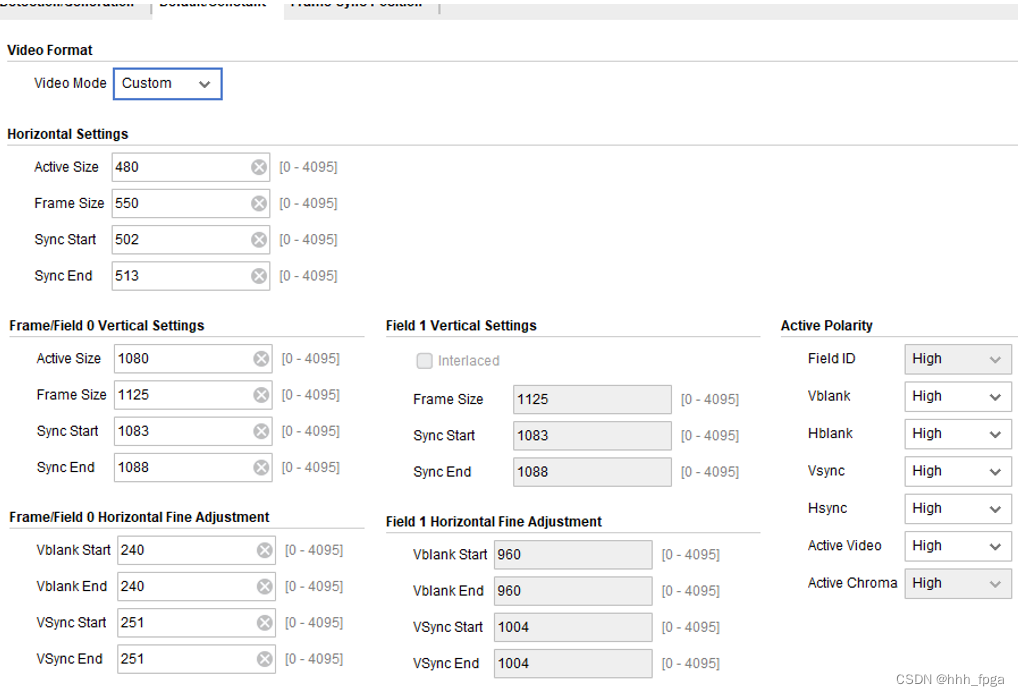

VTC:因为4lane

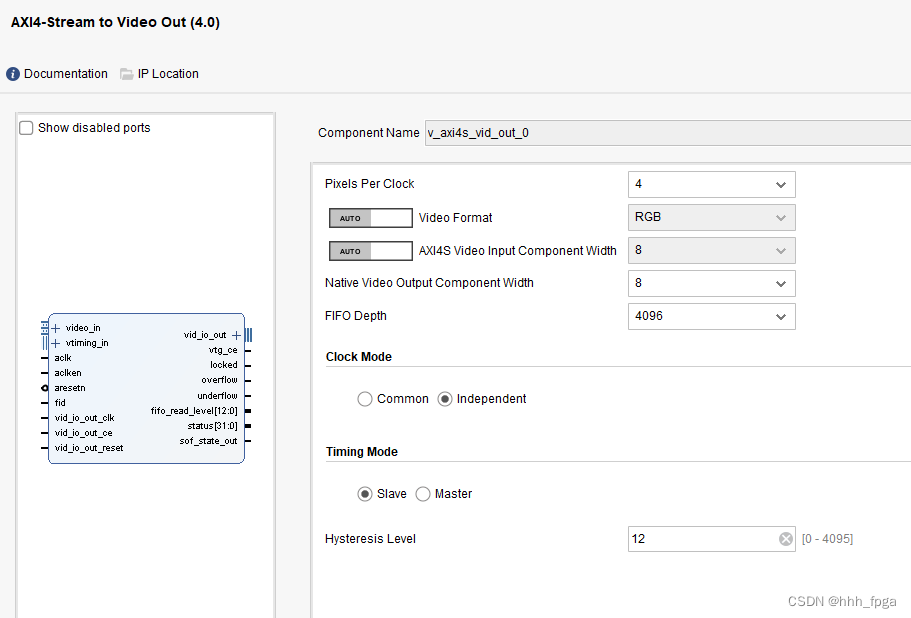

AXI4-Stream to Video Out:

八、ILA在线逻辑分析仪验证的信号:

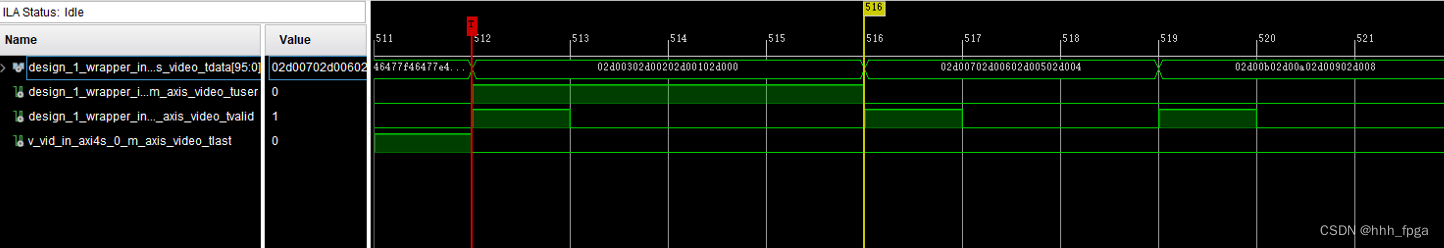

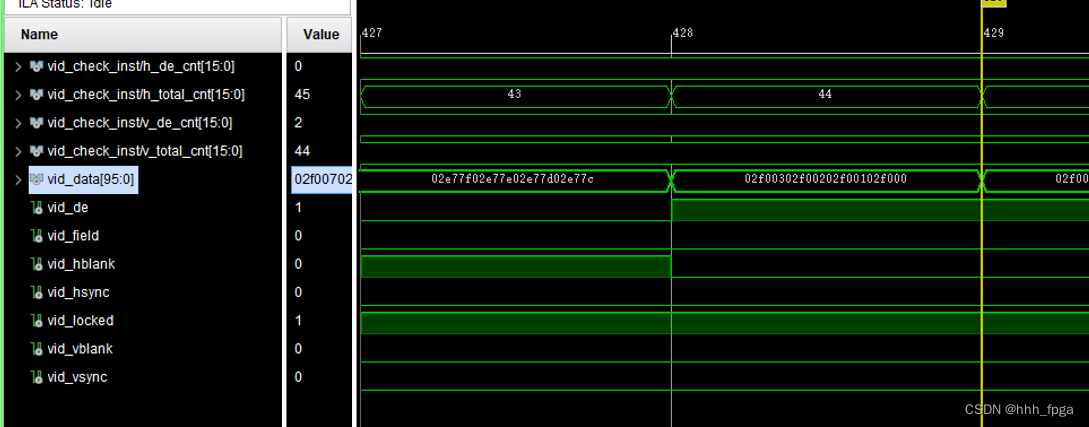

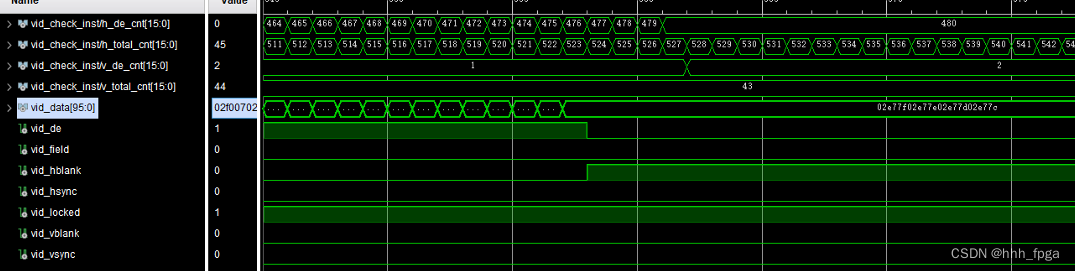

1、Video in to AXI4-stream输出的视频内容:

USER:每一帧的第一个像素:

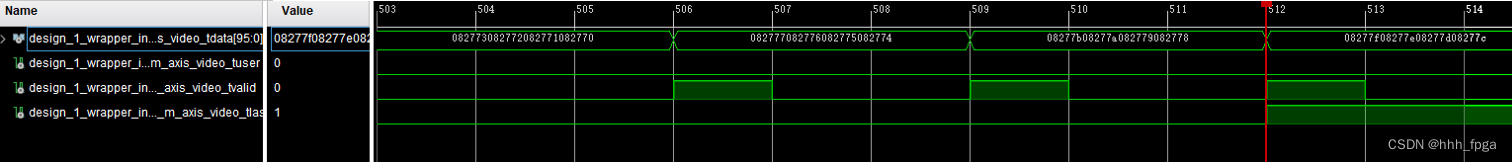

TLAST:每一行的最后一个像素:

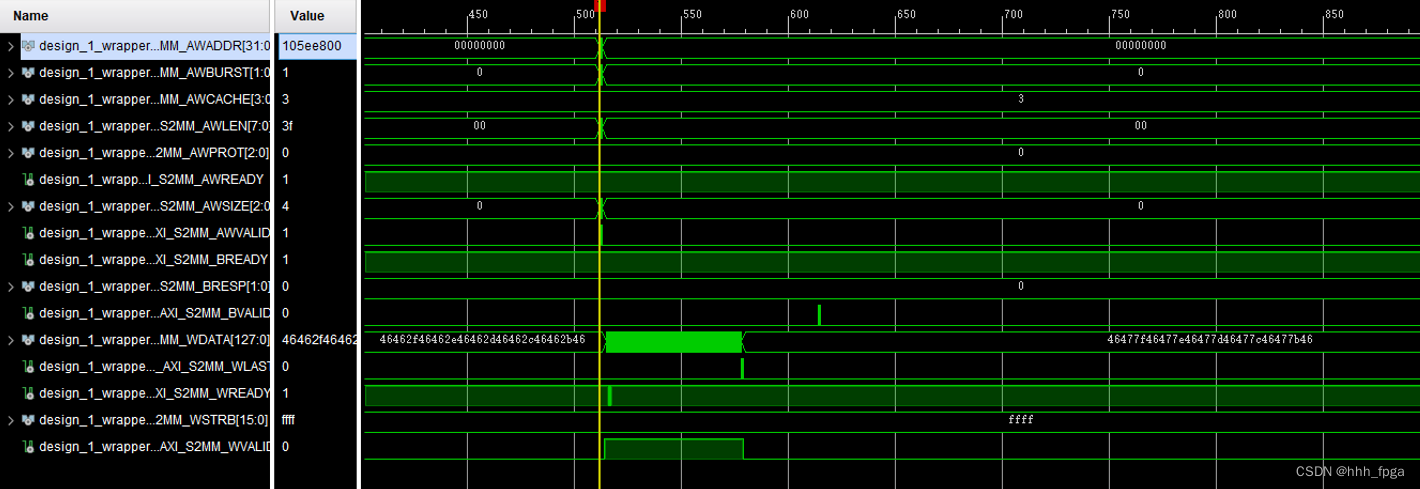

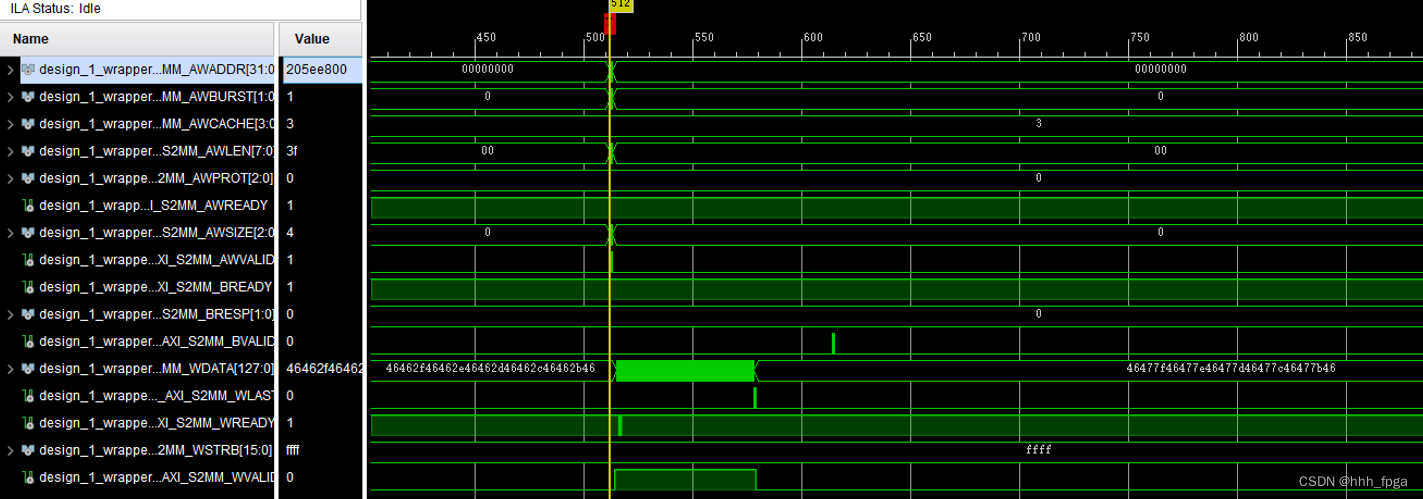

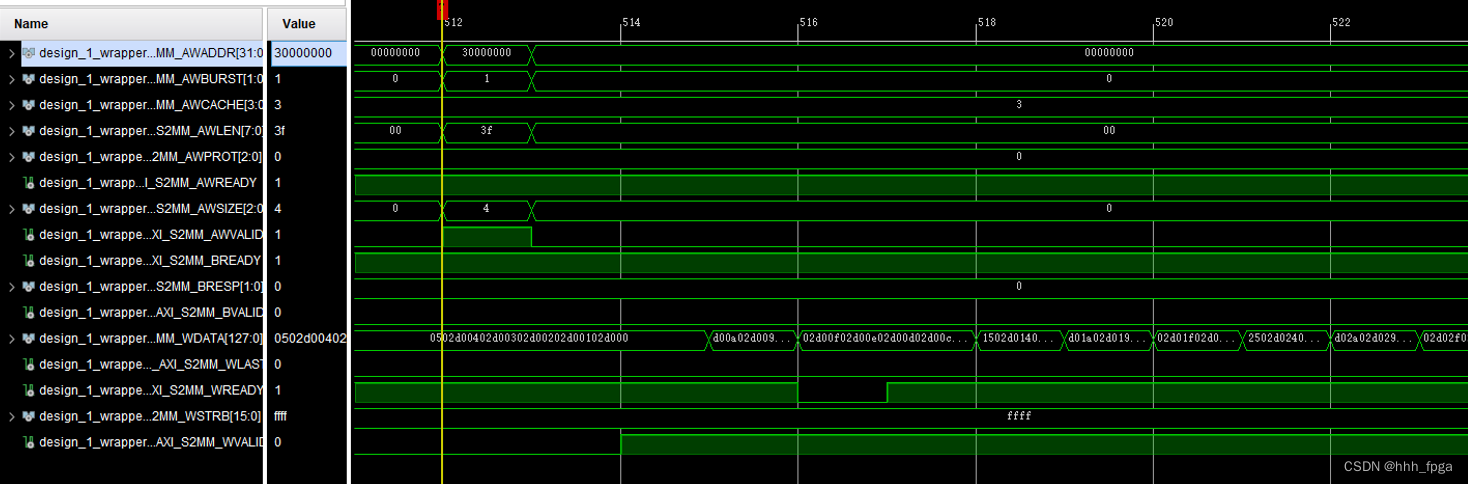

2、VDMA 写ddr: 8bit占用一个地址。

1920*1080*24bit的一帧占用地址是:1920*1080*24/8=6220800=0x5E_EC00

M_AXI_S2MM:写ddr接口:位宽从96-->128bit

第一帧的首地址:0x1000_0000

最后一个地址:0X105E_E800:

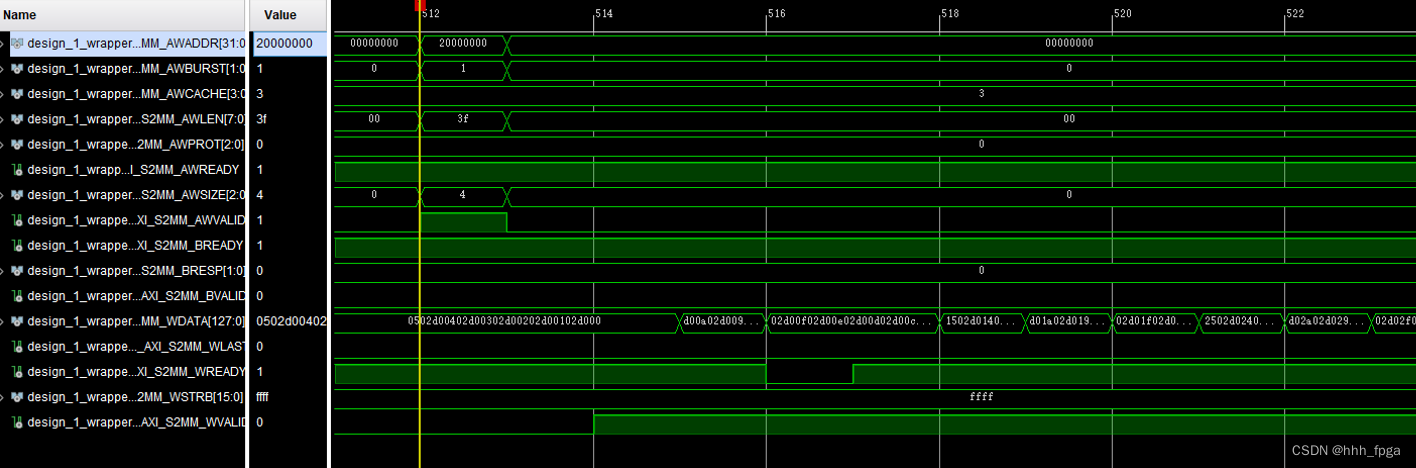

第二帧:

第二帧的首地址:0x2000_0000

最后一个地址:0X205E_E800:

第三帧:

第三帧的首地址:0x3000_0000

最后一个地址:0X305E_E800:

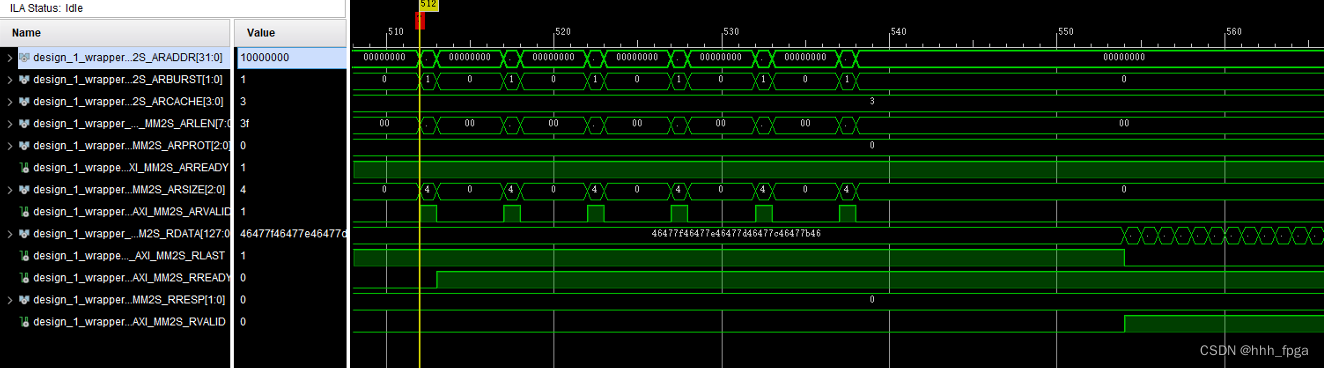

3、VDMA 读ddr

由于它是这种,把读地址用先缓存的方式,这不利于我们用逻辑分析仪捕捉正确地址的内容,所以这里直接捕捉VDMA与video out模块的视频时序

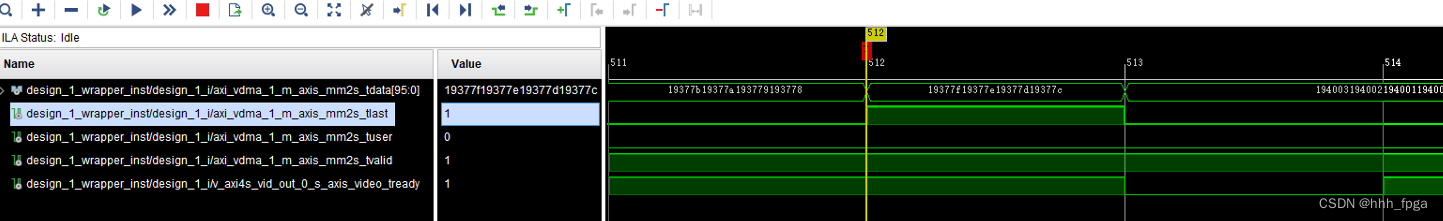

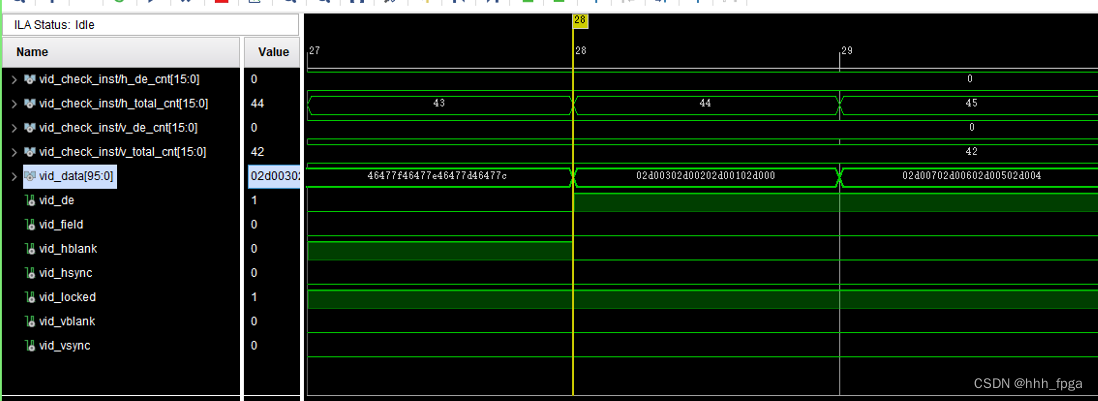

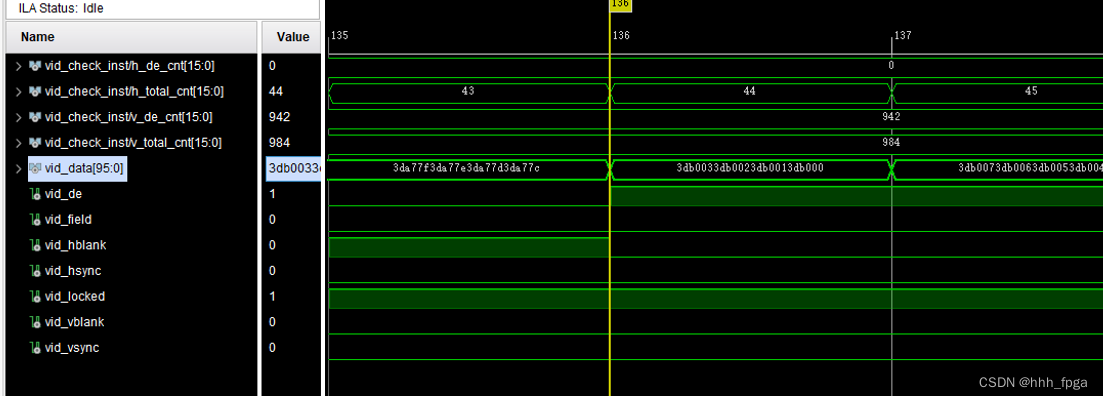

4、VDMA输出video stream

TUSER:每一帧的第一个像素:

TLAST:每一行的最后一个像素:

TLAST:每一行的最后一个像素:

5、AXI4-Stream to Video Out,输出的视频时序和内容:

时序和内容:

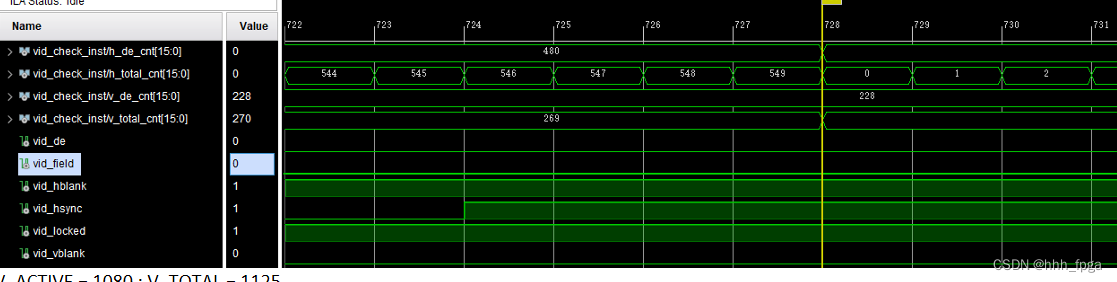

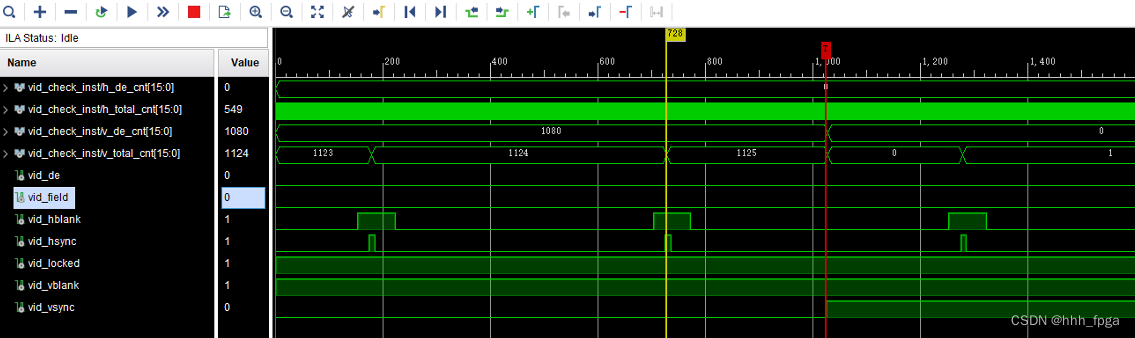

H_ACTIVE = 1920 /4=480; H_TOTAL = 2200/4=550

V_ACTIVE = 1080 ; V_TOTAL = 1125

第一帧的第一个像素:

每一行的第一个像素:

每一行的最后一个像素:

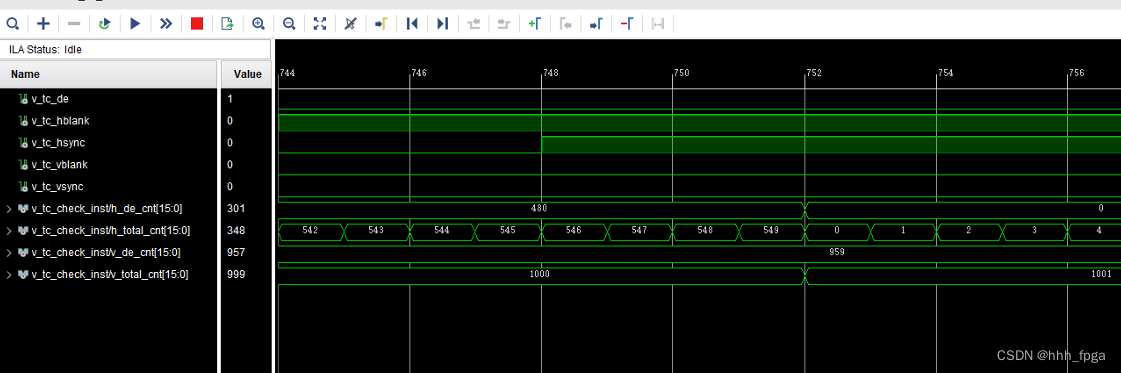

6、VTC:输出的时序验证:

H_ACTIVE = 1920 /4=480; H_TOTAL = 2200/4=550

V_ACTIVE = 1080 ; V_TOTAL = 1125

8730

8730

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?