数字后端自主命题题目大揭秘(附知识星球本周问答精选)

文章右侧广告为官方硬广告,与吾爱IC社区无关,用户勿点。点击进去后出现任何损失与社区无关。

这周是小编过年后的第一个工作周,今天又到周末了,小编公众号依然要更新一篇文章。目前暂定公众号每周一更,主要精力集中在运行知识星球和数字后端培训课程的定制编写。今天分享一道年前小编自己命题,发布在知识星球上的作业题目,这道题目考察的知识点覆盖整个数字后端 implementation。

-

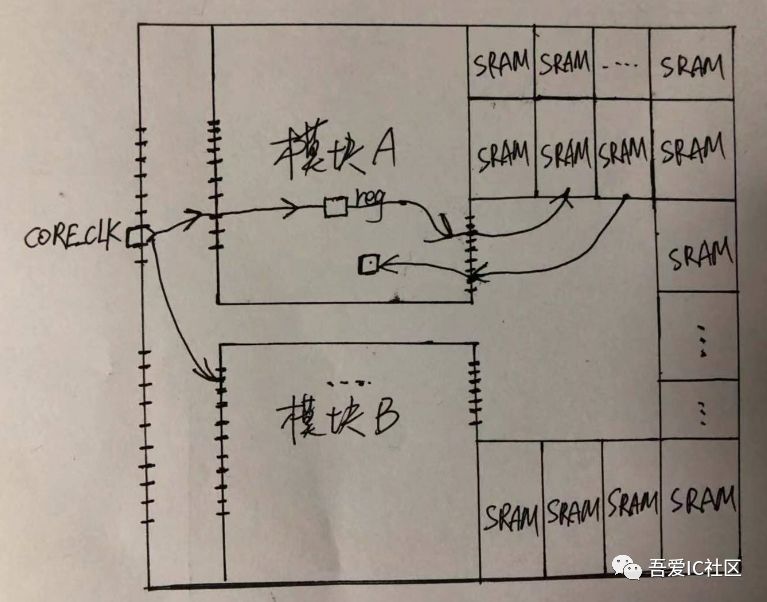

模块 A 和模块 B 为两个 power domain,其他区域为 TOP,TOP 为 Always ON;

-

CORE_CLK 下的 sink 分布在模块 A,模块 B,各个 SRAM 时钟端以及 TOP 区域,即模块 A,模块 B,TOP 彼此是同步的;

-

模块 A 中的 reg 到接口处的逻辑级数特别长,约 26 级左右,即 reg 的 output 到模块 A 的输出端 port 的 delay 比较大,约为 1.6ns;

-

SRAM 数量较多,每个 memory pin 的数量比较多,约 500 个;

以上为已知条件,请大家思考如下几个问题。这道题的知识点可以涉及数字后端 PR 全过程,欢迎大家积极参与讨论。这道题如果你能够轻松解答,年薪 50 万以上不是问题。

1. 该设计是否存在不合理性?

2. 为何模块 A 和模块 B 要做 power domain?

3. 模块 A 和模块 B 输出端是否需要加 isolation cell? 如果需要加 isolation cell,有何优缺点?PR 过程需要如何处理?

4. 如果 Isolation cell 的 input 不小心被插入 buffer 甚至 inverter pair,而且不允许重新跑 flow,应该如何高效解决?

5. 对于 hierarchy 方式实现的 design,如何优化接口处的 timing?

6. 时钟树 clock tree synthesis 应该要如何做?时钟树结构是否合理?

7. 如果 place 和 cto 后的 timing 一致性比较好,route 后 timing 变差 200ps,如何分析解决问题?

8. 该设计的 timing 瓶颈会在哪里?在 PR 实现时有何难点?

星球成员回答精选:

张馨然:能力有限,回答就当个笑话看了 _

1.A B 模块 channal 的处理;sram 要看是否有复用,来决定是否 pin 对 pin 放,还有尽量挨着 core,好 routing,也要看数据流什么关系进行摆放。

点评: A 和 B 模块之间的 channel 确实需要留好,大了则浪费面积,小了则可能有绕线问题,时钟质量可能也不理想。

2. 如果 A B 与 top 不同 voltage,或者有 shut down 需要做 power domain。

点评: 之所以做 power domain,主要是考虑产品应用方面的需求,比如超低功耗需求的产品。如果不做 power domain 的话,A 和 B 模块是一直处于 ON 的状态。

3. 假设 top 1.5v、A 1.2v with shut down 、B 1.8 v alway on。 (1)A B 模块都需要加 iso cell,A 模块需要带 level shift 功能的 isn cell (2)A 模块中 LSISO 放在 top 区域,只需要一套电源即可,否则放在 A 中需要 second pg。B 模块放在 B top 均可,都为 alway on,但是不同电压要用不同 cell。 (3) 无论放在模块还是 top 中,都要 dont touch。

点评: 假设条件与题设不符,已经条件模块 B 是一个 Power domain。A 模块和 B 模块的输出端都需要加 isolation cell,且 isolation cell 需要放置在 AON 的 domain,即 TOP 区域。加 Isolation cell 后会增加一级的 cell delay,会使得模块 A 和 TOP 之间的 timing 更紧。在数字后端实现时,需要选用合适驱动大小的 isolation cell,并将 isolation cell 的 input 端设置 dont_touch。

4. 打断 iso cell,直接和 output 直接,在连接 buf。

点评: 思路是对的,但是如果仅仅是改变连接关系,可能此时 Isolation cell 的位置距模块 A/B 的输出端较远,可能存在 max transition 的问题。因此,还需要将 isolation cell 的位置和 buffer 的位置互换下。如果插入的是 inverter pair,处理起来要稍微复杂点。相应的处理脚本已经发布在星球上。

5. 我现在的 flow 为 top down 的,有前端单独给我 partation 的 sdc,我的做法一般是加严端口,为 top 服务。

点评:子模块接口处加紧 io 的约束,但是需要掌握好度的问题。

6. 针对这个不好分析。

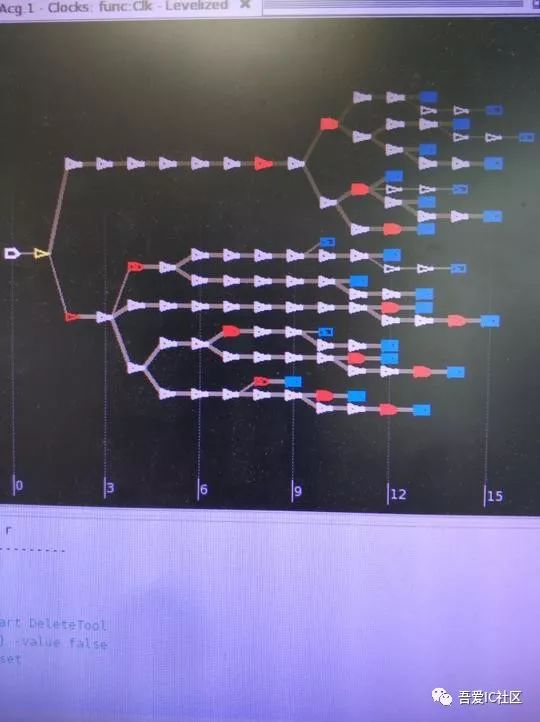

点评: 时钟 CORE_CLK 太早分叉(模块 A 和 TOP),common path 太短,CRPR 补偿不尽人意,严重影响整个 design 的 timing(特别是当 clock tree latency 比较长的时候)。因此,需要对时钟进行 ECO,并添加 clock guide buffer 来人为将 common path 做长。

7.route 后变差的话,route 主要是有真实 data 的 net,可以用高金属层;也进行了 fix hold 动作,可能修过头了;或者 useful skew 前面用得过很了,修 hold 过头了。

点评: 要找 route 后 timing 变差的原因,首先需要知道 cto 和 route 之间的区别,不外乎就是 route 后有真实的绕线了,不再是根据 global route 来估算 RC。既然有实际绕线了,就还可能存在绕线线之间的串扰 crosstalk。除了这些实质性的问题外,就是两个阶段的 timing correlation 问题,比如 timing derating,clock uncertainty,rc scale fator 等设置问题。

第八问留给各位思考。

青玄:我现在初学 PR,但是在星大社区仔细看过第四个问题的解决办法,对 isolation 的输入和 buffer 输出端断开连接到 buffer 输入 eco,不知道我的回答对不对

Andy 回复吾爱 IC:5. 对于 hierarchy 设计是否应该用 ilm model 呢? 模块实现时,端口时序修不干净,该如何解决?

点评: 用 ILM 和 ETM model 都可以。模块实现时能做的就是将接口相关 path 上的 data path 优化到极致,对应 top 的 path 也需要优化。如果这样做之后仍然搞不定,那就需要改设计或者做 pipeline。

星球本周问答精选

以下几个问答挑选自小编知识星球上星友提问,分享给各位。限于篇幅,小编的回答和点评,请移步知识星球查看。

1. 匿名用户 提问:版主 FE 用 tweaker 修完 timing 后,BE ecoRoute 之后 clock 会被变成 routed 和 detour 的,ecoRoute 之前 clock 是 fix 的,有什么原因会导致呢?

2. 我爱 ic 提问:亲,logically_exclusive 和 physically_exclusive 有什么区别?目前只知道 exclusive pin 指只在当前 skew group 做 balance,其他 group 里包含这些 pin 也不作 balabce。

3. 匿名用户 提问: 大佬您好,关于 cts 这一块,面试官会感兴趣哪些方面?

其实这个问题看公众号和星球上的问题足以应对资深工程师的面试。

4. 匿名用户 提问:星住,请教一下我做 cts 的时候,根据 cell 分布大致平均分,预先插入了 2 层 driver,现在问题是单个 tree 的 latency 真的好差,被插入了好多的 inv,树真的好长,请问一般情况怎么做短 latency 呢?用大 buffer?控制 tree 的级数?好的绕线层?都已经尝试了!!并且设了 latency,并没有什么用!请星主指导一下

•

5. 匿名用户 提问:群主,为什么加 decap,ir 会变好啊?

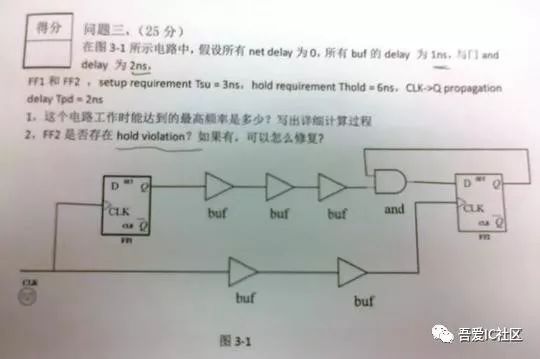

6. 小娟姐姐提问:请问针对该题以下解答是否正确 1、最高工作频率计算 TCLK >= [Tlaunch + Tck2q + Tdp] – Tcapture + Tsetup TCLK >= [0+2+5]– 2 +3 = 8 ns 最高频率为 125MHz 2、FF2 hold slack [Tlaunch + Tck2q + Tdp] - [Tcapture + Thold] =[0+2+5]–[2+6]\= -1 存在 hold 违例. 修复方法: 删除>=1 个 capture 路径 Buffer 或插入>=1 个 launch 路径 Buffer

•

7. 梦飞提问:星主,最近一直在看 cts 方面的资料,心中还是有比较多疑惑,想请您百忙中抽出时间来解答一下,非常感谢!CTS 中的一般约束 max clock transition,max clock fanout,max capacitance,uncertainty,skew 及 latency 应该怎么设?主要是参考哪些信息来设置?

8. 匿名用户 提问:请问动态 IR-drop 分析中有 10% 的压降。虽然是符合规定,但有一点搞不清楚,例如在 timing signoff 中逻辑库中描述的电压是 ss 为 0.81v,tt 为 0.9v,ff 下为 0.99v,按照这些电压值来 signoff,是在哪里考虑到那 10% 的压降,或者说是如何保证出现 10% 压降后时序仍然是没问题的?谢谢

9.ICer 提问:星主你好,新年快乐。想请问你一个问题,我有个 block cell 数量才 40w, 利用率一直做不上去,即使不到 40% 的利用率也还是有几百条 short, 看 database 感觉是线太多了,绕的太密,但是不是知道从哪儿找到具体的数据来证实,ICC2 里面提供这样的命令吗,谢谢

10. 匿名用户 提问:小编,请教一下时钟树要怎么做怎么 balance skew?

**小编知识星球简介 **:

在这里,目前已经规划并正着手做的事情:

-

ICC/ICC2 lab 的编写

-

基于 ARM CPU 的后端实现流程

-

利用 ICC 中 CCD(Concurrent Clock Data)实现高性能模块的设计实现

-

基于 ARM 四核 CPU 数字后端 Hierarchical Flow 实现教程

-

时钟树结构分析

-

低功耗设计实现

-

定期将项目中碰到的问题以案例的形式做技术分享

在这里,各位可以就公众号推文的内容或者实际项目中遇到的难题提问,小编会在 24 小时内给予解答(也可以发表你对数字后端设计实现中某个知识点的看法,项目中遇到的难点,困惑或者职业发展规划等)。

反正它是一个缩减版的论坛,增强了大家的互动性。更为重要的是,微信有知识星球的小程序入口。星球二维码如下,可以扫描或者长按识别二维码进入。目前已经有113位星球成员,感谢这 113 位童鞋的支持!欢迎各位铁杆粉丝加入!终极目标是打造实现本知识星球全员年薪百万的宏伟目标。(星球的门票即将调整到 228 元 / 年,有需求的朋友趁早上车,**目前价格已经提高至 208 元 / 年,折算每天需要六毛钱 **)

点击下方 “阅读全文” 了解更多

1064

1064

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?