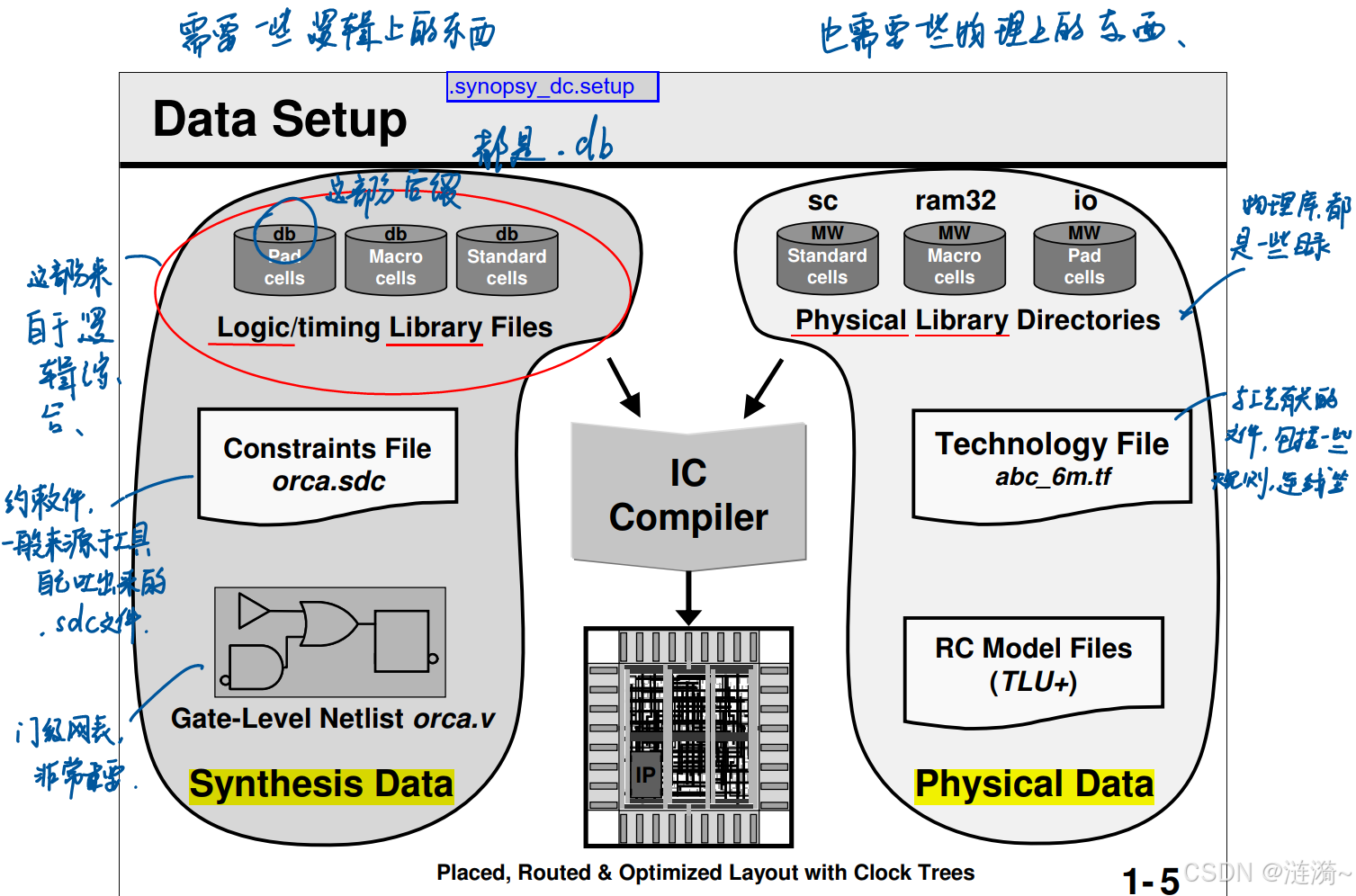

ICC做布局布线需要的数据资源分为非工艺库文件和工艺库文件,其中工艺库文件包括.v网表和.sdc约束文件,工艺库文件分为逻辑库和物理库:

一、工艺库文件

1、逻辑库——.db

.db

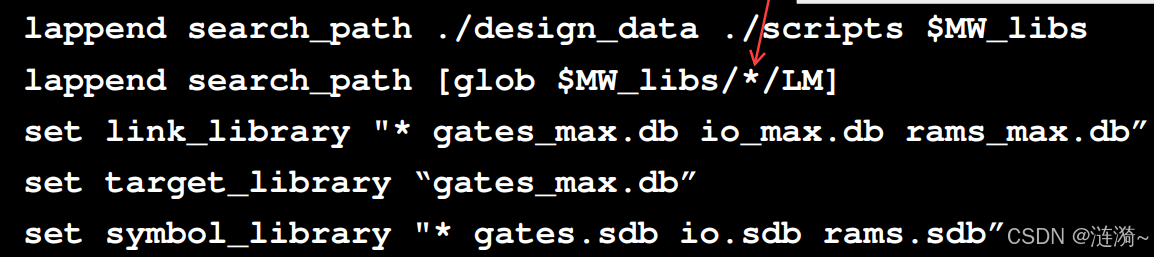

通常与DC使用相同的库文件,提供工艺库中标准单元、macros(IP,ROM,RAM)的时序和功能信息,定义驱动/负载的max fanout、max transition、max/min capacitance。在ICC中用target_library和link_library描述。必须指定逻辑库,用target_library,link_library、search_path三个变量来指定,其中search_path指向.db文件存在的路径,其余两个指向具体的.db文件。

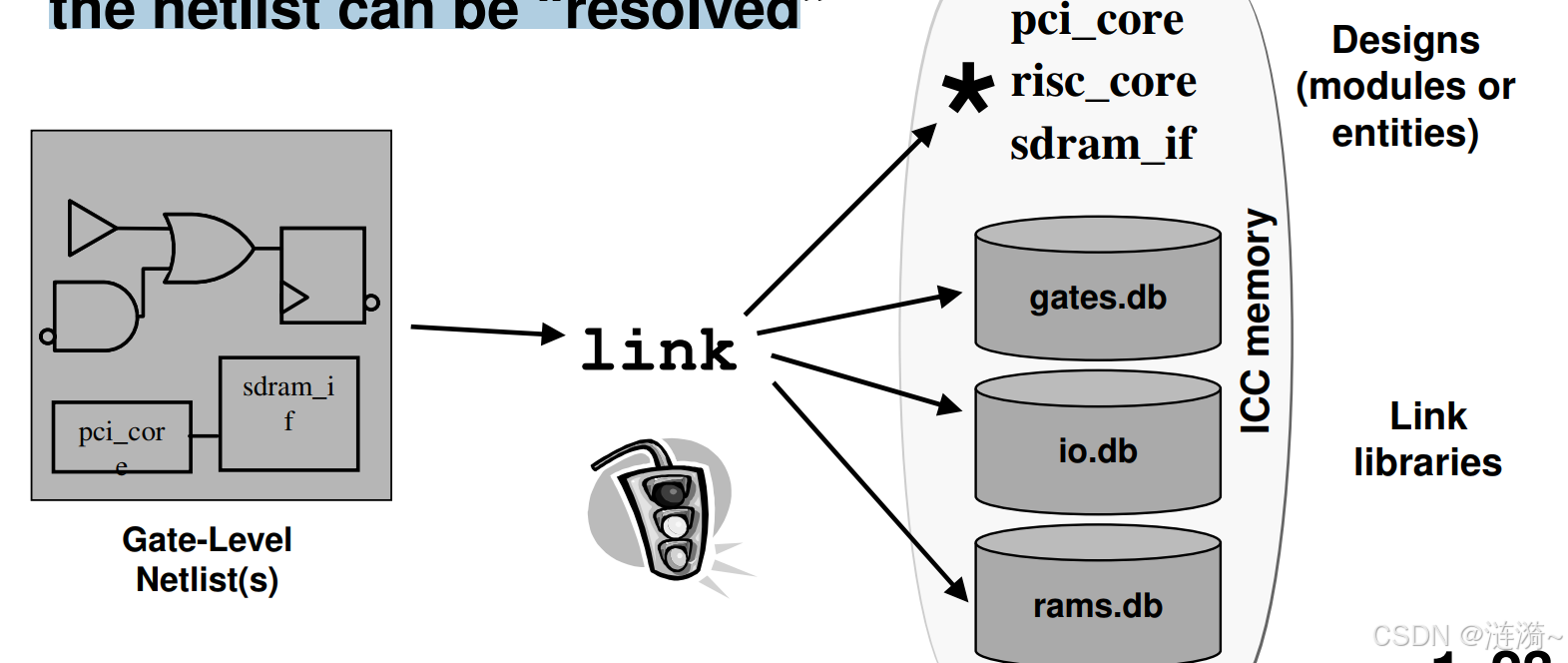

- link library是用来实例化网表中的元件,将逻辑库连接在一起,变量*代表ICC的内存,和read_verilog/ddc或import_designs一起读的任何设计都会被存储在icc内存中。如果所有instances都找到了,link命令会返回1,link成功,如果link存在找不到的instances,会出现警告信息。

- target library只列举有基本逻辑门(standard cells、IO pads、marcos)的单元库。

- search_path变量用来缩短文件举例,列出文件名ICC就在serach_path目录中找到文件,否则用户就要列举出具体的文件路径。

- symbol libraries在GUI界面看电路图时提供图形化按钮。

2、物理库——.mw、.tf、TLU

Milkway:

记录工艺和标准单元、macro、pad cell物理相关信息,以及这些单元在布局时需要的最小间隔和对绕线的需求等。

.tf:

工艺文件,提供了technology-specific信息以及tile的宽高,例如:每层金属的名称、物理和电学特性。另外,ICC要求TF必须包含Design Rules:包括width,pitch,spacing等值的定义。

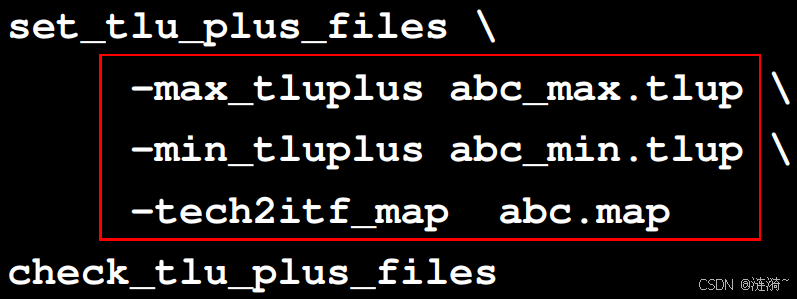

TLU+:

RC寄生模型文件,用于计算互连线RC,有多个corner的建模。由工艺厂商提供,但如果工艺厂商仅提供了itf文件,可以通过工具StarRC使用grdgenxo将itf文件转换成tluplus文件。指令如下:

unix% grdgenxo -itf2TLUPlus -i <ITF file> -o <TLU+ file>tf文件和itf文件(包含layout层数、通孔信息)之间用.map文件来对应。

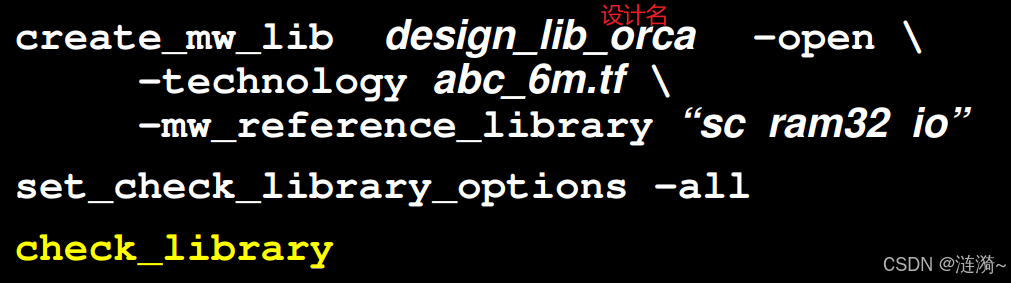

用命令create_mw_lib -mw_reference_library来指定。如果前面的search_path包含了tf文件和mw_reference_library所在的路径,则用以下方式指定有效,否则必须指出具体其具体路径。check_library可以找出逻辑库和物理中不一致的cells 和pins,物理库中缺失layout或者abstract view的cells,重复命名的cells。

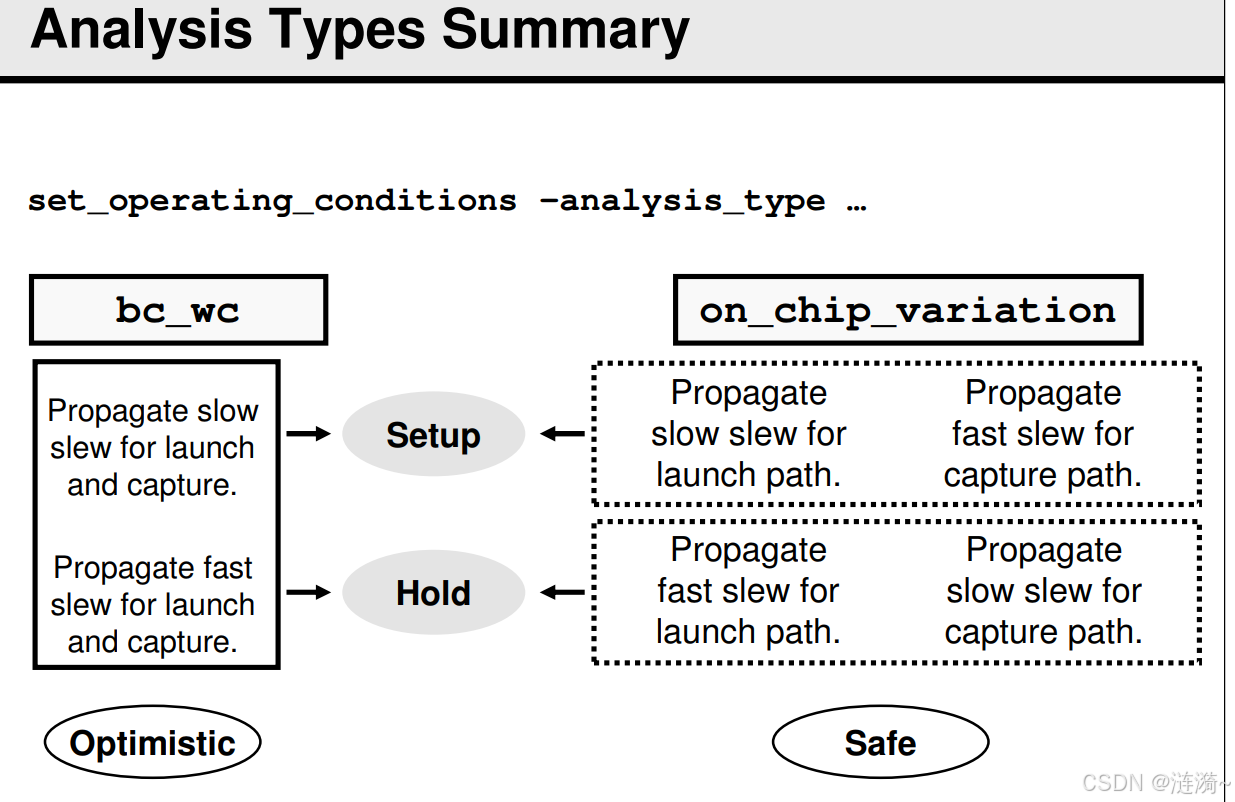

指定分析条件:set_operating_conditions

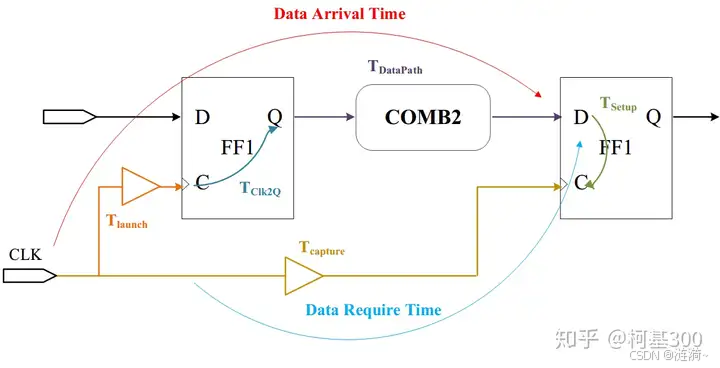

set_operating_conditions:指定工作条件(与corner相关),-analysis_type bc_wc | on_chip_variation,指定bc_wc和on_chip_variation选项中的一个,用于setup/hold 时序分析。

在bc_wc分析中:仅在max工作条件下,并检查setup时序;仅在min条件下检查hold时序。launch path和capture path工作在同一个工作条件下。

在on_chip_variation分析中,时序分析更加严格:检查setup时序时,launch path工作在max工作条件下,capture path工作在min工作条件下,检查hold时序时,launch path工作在min工作条件,capture path工作在max工作条件下。launch path和capture path工作在不同工作条件下。

具体指定方式如下:

set_operating_conditions -analysis_type bc_wc|on_chip_variation \

-min corner -min_library min_lib \

-max corner -max_library max_lib其中 corner由min_lib.lib文件中,default_operating_conditions指定,如下图: corner具体值则为ss_v4p5_125c

![]()

3、IP库——.sldb文件

synthetic_laibrary :DesignWare的可重用IP库,将运算符号转换成特定的库。

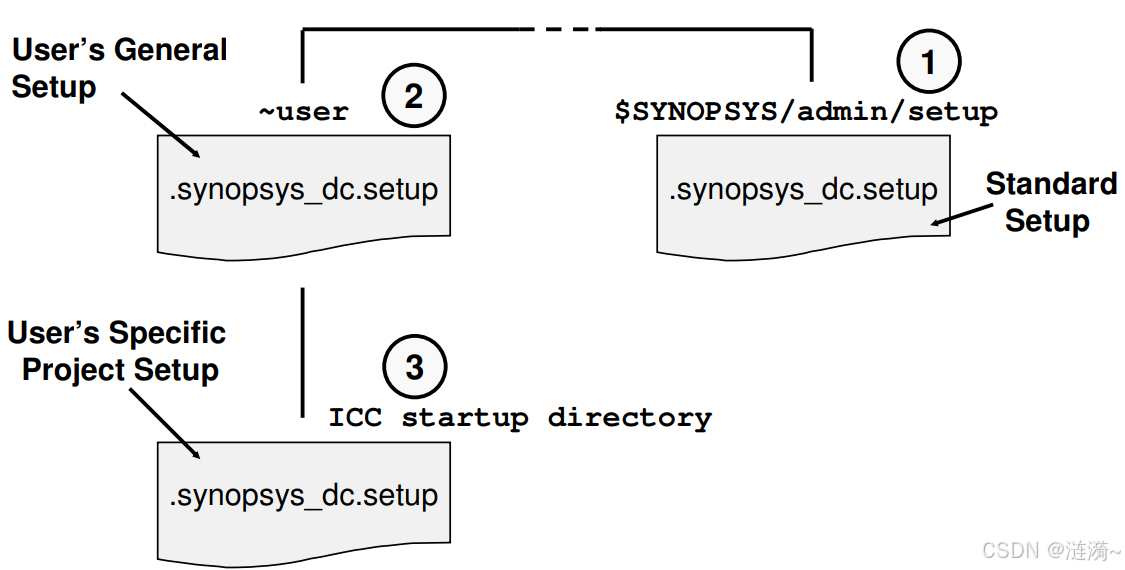

以上所有命令可在运行icc时一句一句输入,也可以防在.synopsys_dc.setup文件中,运行时工具自动初始化。该文件放在以下三个地方都可以初始化,启动时也按照以下顺序执行。

二、非工艺库文件

.sdc:由DC导出,可人工修改,以满足设计要求,可由命令read_sdc读入;

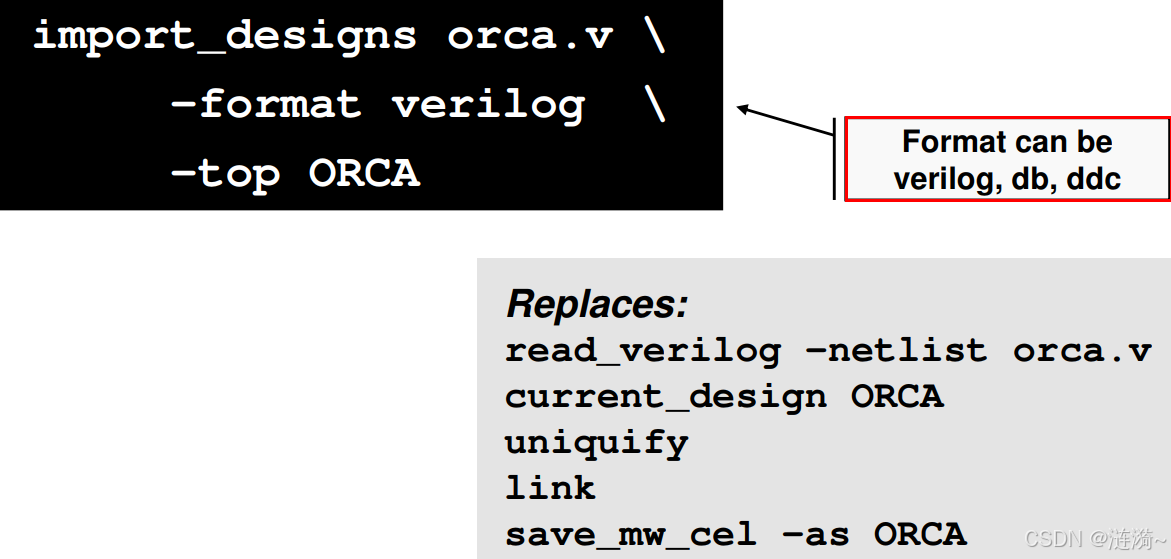

.v:由DC导出,由verilog等语言经过综合得到的门级网表。除了可以读入DC导出来的.v文件外,还可以读入.ddc文件,其不仅包含netlist、sdc,还包含了一些物理信息,placement blockage,-spg信息等,可由命令read_verilog或者import_design读入。读入网表之后就可以用list_libs命令来验证时候所有需要的logic lib都导入成功了。

总结:

ICC做PR时需要逻辑库和物理库,逻辑库为.db文件,物理库为.tf 和tlu文件。库的指定命令如下:其中逻辑库用search_path,target_library、link_library三个变量指定。物理由create_mw_lib指定。itf和tf文件之间通孔和层数的对应用.map文件来表示。

search_path:指定搜索路径,减少路径长度

target_library:与DC一致,使用link_library进行翻译,优化后映射到目标库中。

link_library:为网表中的每个子设计在ICC内存中找到相应的设计。

set_min_library:指定best_case用作保持时间分析,指定worst_case用作建立时间分析。

set_tlu_plus_files:指定tlu文件(与corner有关)

set_operating_conditions:指定工作条件(与corner相关)

creat_mw_lib:建立Milkway,指定tf和mw文件。

check_library:找出逻辑库和物理中不一致的cells 和pins,物理库中缺失layout或者abstract view的cells,重复命名的cells(该命令需要安装library compiler)。

check_tlu_plus_files:查看tlu文件是否存在且对其完整性进行检查。

list_lib:检查是否所有需要的库都load成功。

check_timing:检查约束的完整性,包括input output delay,no clock register。

report_timing_requirements:检查是否存在false path 、multicycle path,asychronous min or max delay 约束。

report_disable_timing: report disable path,由set_disable_timing或者工具自动根据加的。

report_case_analysis:report 恒为0或者1的ports pins。

lappend serach_path XXXpath

lappend search_path XXXpath

set_app_var target_library "XXX.db"

set_app_var link_library "* $target_library"

set_min_library $MAX_LIB.db -min_version XXX.db

set_tlu_plus_files -max_tluplus "XXX.tluplus" \

-min_tluplus "XXX.tluplus" \

-tech2itf_map "XXX.map"

set_operating_conditions -analysis_type bc_wc \

-min XXX -min_library XXX.db \

-max XXX -max_library XXX.db

create_mw_lib XXX -open \

-technology XXX.tf \

-mw_reference_library {XXX}

set_check_library_options -all

check_library

check_tlu_plus_files

read_verilog -top XXX -netlist XXX.v

read_sdc -version 2.0 XXX.sdc

list_libs

check_timing

report_timing_requirements

report_disable_timing

report_case_analysis参考:

2335

2335

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?