version2.0

一、VCS+dve:

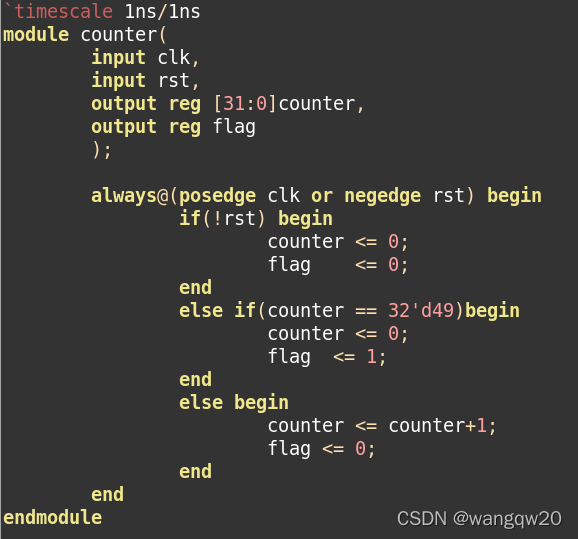

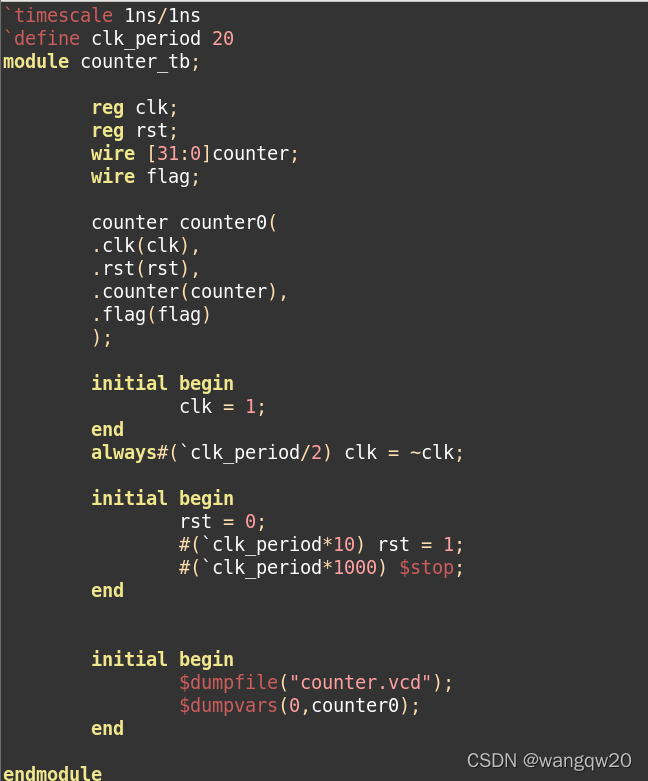

1. 编写.v文件。以计数器为例。

counter.v文件

counter_tb.v文件

2. 终端输入 vcs -full64 counter.v counter_tb.v -debug_all

-full64是64位linux操作系统,这里可以将vcs -full64写入环境变量中,用vcs代替。

-debug_all用于产生debug所需的文件。

1)debug: 只打开一点

2)debug_all:全部打开

3)debug_pp:保证打开开关最多的情况下,对性能影响最小的

3. 观察生成了一个simv可执行文件,运行./simv -gui 打开dve软件。

还有一些是附加命令,意义如下。

-l xxx.log 用于将编译产生的信息放在log文件中。

+v2k用于verilog兼容2001年之前的标准。

-f verilog.f 用于将.f中的verilog文件全部编译。

-R 编译后立即运行,即编译完成后立即执行 ./simv

-Mupdate 源文件有修改时,只重新编译有改动的.v文件,节约编译时间。</

本文介绍了如何使用VCS+dve+verdi进行FPGA开发的仿真流程,包括.v文件编写、编译命令、使用makefile简化操作、设置环境变量以及解决波形显示问题。通过VCS的debug选项、Verdi的交互文件生成,实现高效仿真和波形分析。

本文介绍了如何使用VCS+dve+verdi进行FPGA开发的仿真流程,包括.v文件编写、编译命令、使用makefile简化操作、设置环境变量以及解决波形显示问题。通过VCS的debug选项、Verdi的交互文件生成,实现高效仿真和波形分析。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?