目录

1、输入电容的位置。

2、电感的放置

3、FB脚该从哪里引。

案例1、下图为一个降压DCDC电路,图中红色的框是比较关键的地方,走线铺铜的时候要特别的注意,输入的电容要紧靠芯片的VIN和GND。

下面我们看一下这个PCB的布局,输入电容的位置距离芯片的VIN和GND很远,没有紧贴芯片。 我们重新调整输入电容的位置,可以出输出的纹波由大于100mV降到了小于10mV,开关节点上的上升沿的振荡也没有了,注意一下输入的电容排列,应该是电源进来先经过大电容再小电容。

我们重新调整输入电容的位置,可以出输出的纹波由大于100mV降到了小于10mV,开关节点上的上升沿的振荡也没有了,注意一下输入的电容排列,应该是电源进来先经过大电容再小电容。

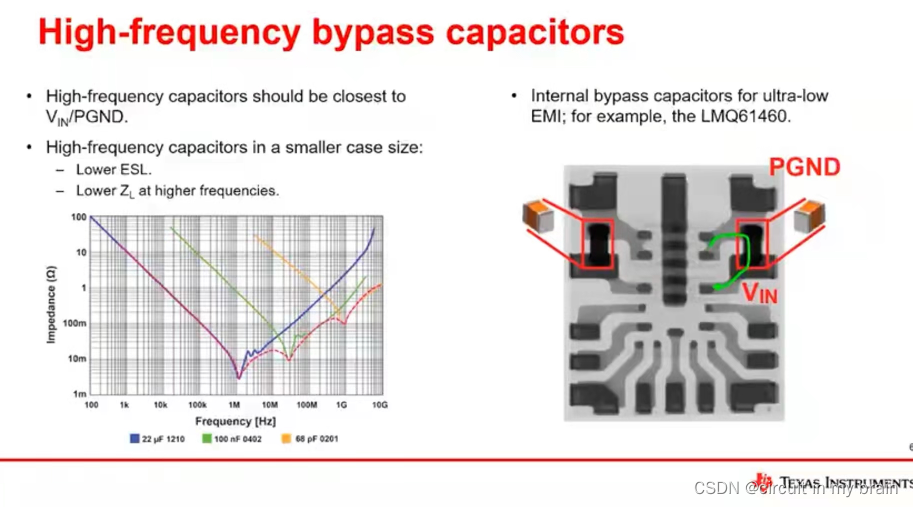

还有一般电源的输入电容都是大小尺寸搭配一起使用,这样做的原因是不同容值的电容的ESL的谐振点是不一样的,这样可以增加一些谐振点,在谐振点的阻抗还是比较小的。

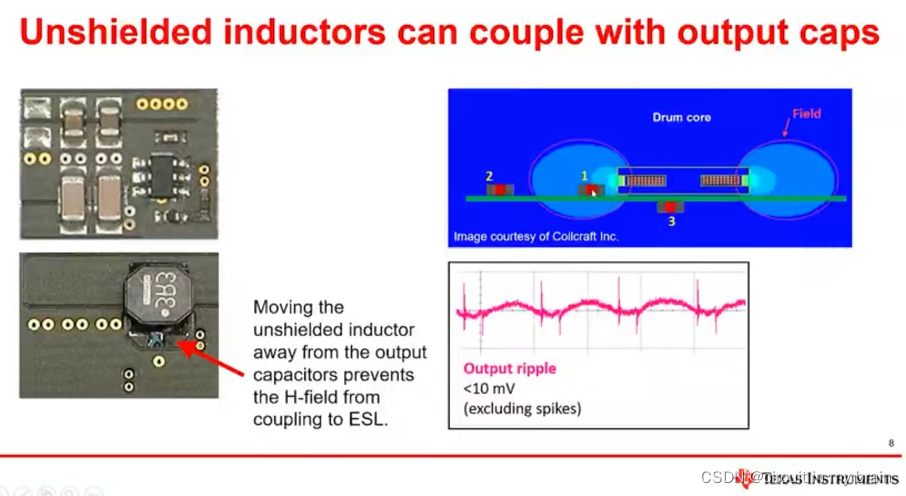

案例2、在下图的pcb布局中发现,功率电感的放置方向不一样会使输出纹波的相位发生改变,那电感的方向到底影响了什么,原因应该是电感中的磁场耦合到了输出电容的ESL上,使纹波发生了改变。

解决的办法就是把电感和输出电容的距离拉远,或者把电容放在另外一面。

下图为不同电感的辐射磁场强度,半屏蔽电感和不屏蔽电感的辐射强度是差不多的,全屏蔽电感效果比较好,电感下面连接地,有助于减小电感的辐射。由于电感的辐射我们输入电容的地千万不要经过电感的下面。

案例3、注意下图中的反馈电阻和电源芯片的位置,电阻分压到芯片的基准0.76v,然后这个弱的模拟信号(因为这个信号会进入误差放大器,误差放大的输入阻抗很高),在板子上面经过了很长的路径,这很长的路径上面就很容易耦合到一些噪声,尤其是还经过了辐射很强的电感下面。

改善的办法就是减小这个弱信号的长度,我们从下图中可以看出,这个电阻分压后的信号以非常短的路径给到电源芯片,从结果看纹波降了很多。

说到FB,下图中的问题我们也必须要注意,下图为一个输出0.85v,20A的DCDC,遇到的问题是负载调整率很差,图中红色的虚线为随着负载的变化输出电压的变化,可以看出在20A负载的时候输出电压已经降到了0.82v左右,降了30mV左右,那么是什么原因造成了这个问题?

在大电流的PCB布局时我们都要注意电流在铜皮上面的压降,我们选择电感后选择电压反馈点,就没有考虑铜皮上的压降,我们把电压检测点选在输出端子上面就好了。

7852

7852

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?