少数设计中会用到带有异步复位和异步置位的触发器,综合工具也能正确推断该器件类型,但是仿真行为和实际电路行为存在差异。

带有异步复位和异步置位的触发器的电路行为如下:

时钟上升沿,复位信号和置位信号两者中的任意一个的上升沿或者下降沿变化都可能引起触发器输出的改变。

带有异步复位和异步置位的触发器的verilog描述如下:

always @(posedge clk or negedge rst_n or negedge set_n)

if(!rst_n)

q <= 1'b0;

else if(!rst_n)

q <= 1'b1;

else

q <= d;

从语义上看仿真时,只有在时钟上升沿,复位信号下降沿或者置位信号下降沿触发器的输出才有可能发生改变。

综上来看,仿真和实际电路在复位信号和置位信号的上升沿处存在行为不一致的可能:

当复位信号和置位信号同时生效时,如果复位被解除,电路应该由复位状态进入置位状态。但是仿真上复位的接触不会触发输出值的更新,造成仿真歧义。

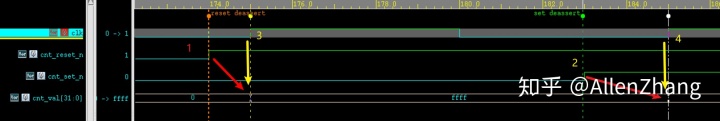

上图为一个带异步复位和异步置位的触发器的仿真波形:

初始时刻,触发器的复位和置位同时assert,触发器处于复位状态;

时刻1,触发器的复位deassert,触发器仍然处于复位状态,与实际电路行为不一致;

时刻2,触发器的置位deassert,触发器状态不改变,与实际电路行为一致;

所以,对于设计中包含带异步复位和异步置位的触发器,需要确认触发器复位和置位同时assert的场景下复位先于置位deassert时触发器的输出是否真的满足设计要求。

3981

3981

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?