FPGA保持时间检测机理及影响因素分析

本文分别将FPGA保持时间检测机理,以及影响因素分析总结如下。

一、时序引擎是如何进行保持时间检查的

第一步:确定保持时间要求

保持时间=保持时间的捕获沿-保持时间的发起沿。

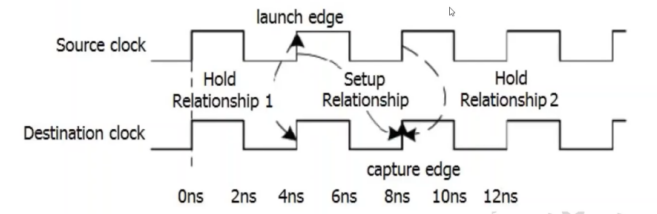

保持时间要求是以建立时间要求为基础的,保持时间要求有两种情况,如下图所示。

1、当前建立时间的发起沿产生的数据不能被当前建立时间的捕获沿的前一个有效沿捕获;

2、当前建立时间的发起沿的下一个有效沿产生的数据不能被当前建立时间的捕获沿捕获。

如何理解这两种情况要求,个人理解,就是采集旧数据时,不能被新数据刷新。

并且需要特别注意保持时间的发起沿和捕获沿是以建立时间触发沿情况为前提选择的。

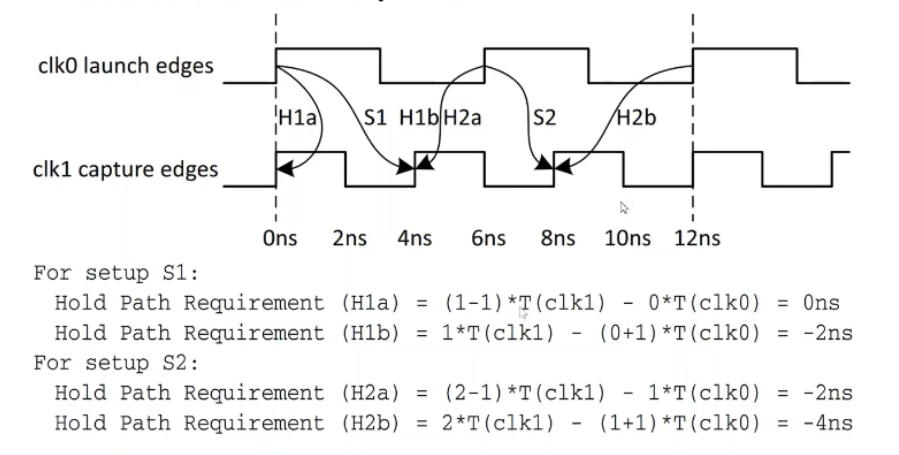

保持时间与建立时间类似,发起沿和捕获沿的确定可能有多种组合,时序引擎根据所有建立时间需求找到所有保持时间需求,并从保持时间需求(可正可负)中找到最大的保持时间需求。注意:保持时间需求值可正可负,而建立时间需求值必须为正。

如下图,建立时间沿的选择有两种可能,在每种建立时间沿的情况下,又有两种保持时间沿的情况,因此一共有4种情况。

例如在S1下有H1a和H1b两种情况,在S2情况下有H2a和H2b两种情况。

在这4种情况下,时序引擎计算并找到最大的保持时间,即H1a,该情况是最容易出现时序违例的,较大的时钟偏斜会导致捕获沿延时较大,相对来讲数据的保持时间就会更少。

第二步:计算数据的需求时间

数据需求时间=目的寄存器时钟捕获沿+目的寄存器时钟延迟+时钟不稳定度+寄存器固有延迟(Th)

注意:这里是旧数据需求时间。

第三步:计算数据的达到时间

数据达到时间=源寄存器时钟发送沿+源寄存器时钟延迟+数据路径延时

注意:这里是更新数据到达的时间。

第四步:计算保持时间的裕量(slack)

保持时间裕量=数据的到达时间-数据的需求时间。

注意:保持时间裕量的计算正好与建立时间裕量的计算公式相反。

实例分析

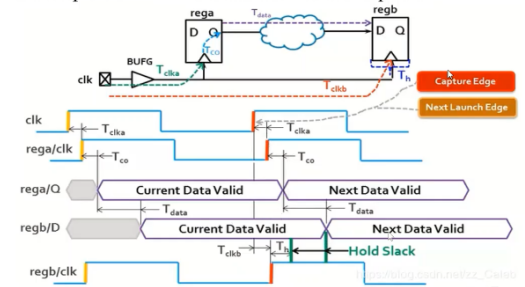

如下图:

数据到达时间(新数据)=发起沿+源寄存器时钟延迟(Tclka)+Tco+数据延迟(Tdata),其中数据延时(Tdata)=数据路径组合逻辑延时(Tlogic)+布线延时(Tnet)

数据需要时间=目的寄存器捕获沿+目的寄存器时钟延迟(Tclkb)+Th

保持时间裕量=数据到达时间-数据需求时间。

二、保持时间裕量影响因素分析

根据公式分析哪些因素会导致holdup slack为负。

holdup slack=(发起沿-捕获沿)+(源时钟寄存器时钟延迟-目的寄存器时钟延迟)+Tco+数据延时(Tlogic+Tnet)-Th

即:holdup slack=Tco+Tlogic+Tnet-Th-保持时间要求-时钟偏斜。

保持时间裕量为负的情况较少见,当建立时间裕量较大时,通常工具会自动插入延时来增加保持时间裕量。

根据上面公式分析,将保持时间裕量违规因素整理如下:

保持时间时序违规因素一

保持时间需求大于0,通常由时序引擎选择错误的捕获沿导致,需要手动更正。

保持时间时序违规因素二

时钟偏斜大于300ps,通常是由时钟路径上的组合逻辑延时导致。

保持时间时序违规因素三

Th过大,通常是由时序路径终点为Block导致。

本文详细解析了FPGA的保持时间检测机制,包括确定保持时间要求、计算数据需求时间、达到时间和保持时间裕量。保持时间裕量的正负受时钟偏斜、组合逻辑延迟等因素影响。当保持时间裕量为负时,可能导致时序违规,需关注捕获沿选择、时钟路径延迟等关键因素。

本文详细解析了FPGA的保持时间检测机制,包括确定保持时间要求、计算数据需求时间、达到时间和保持时间裕量。保持时间裕量的正负受时钟偏斜、组合逻辑延迟等因素影响。当保持时间裕量为负时,可能导致时序违规,需关注捕获沿选择、时钟路径延迟等关键因素。

1416

1416

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?