文章目录

前言

打卡学习第六天、第七天

今日天气:小雨

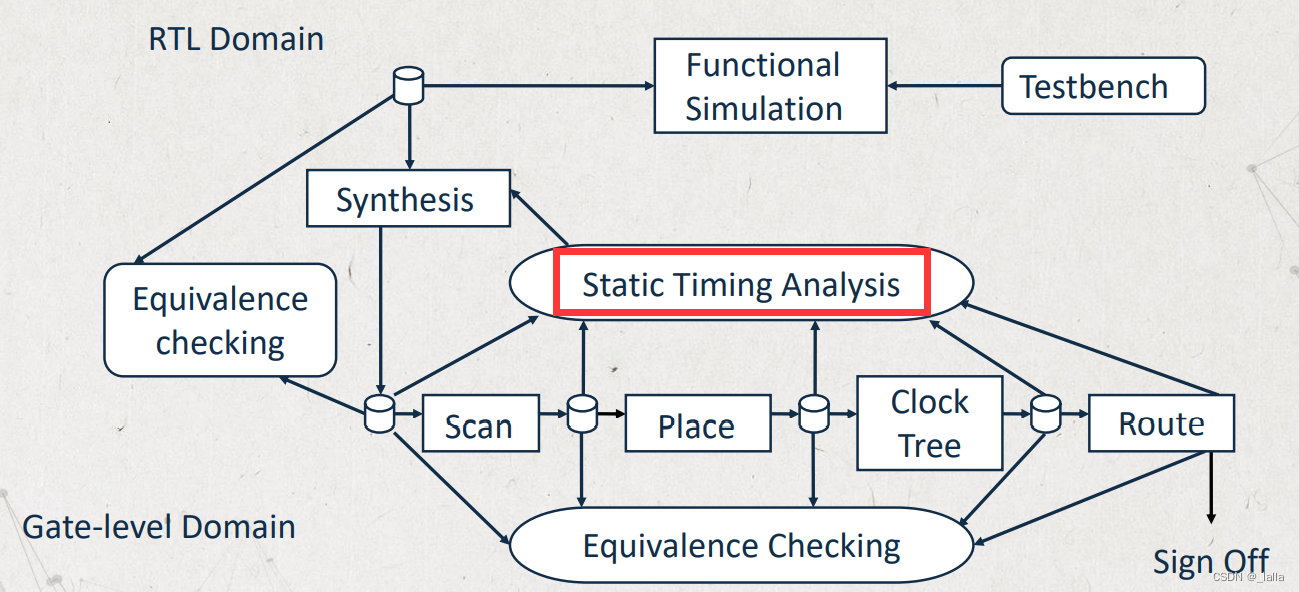

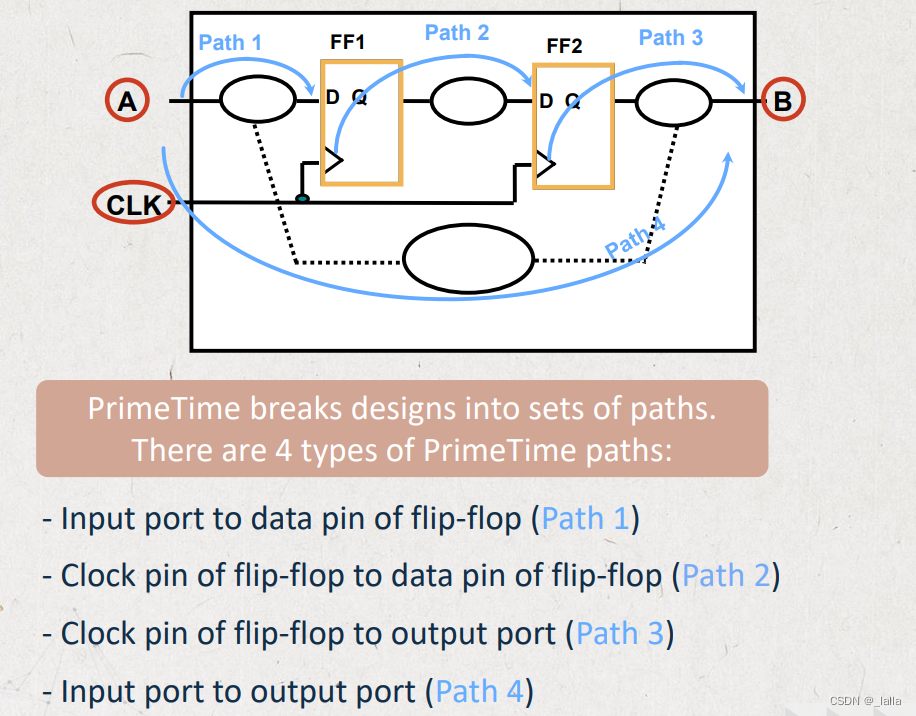

一、概述 Static Timing Analysis

工作:对电路时序进行检查,不是仿真,所以运行速度比RTL级更快,且对电路的逻辑功能不进行检查,因此不产生测试向量对电路的功能点进行验证

逻辑综合后面的每一个阶段都需要进行STA,以保证建立时间和保持时间是收敛的

同步电路才有静态时序分析,异步电路没有

动态仿真和STA是互补的关系,有些没有验证到的功能点,需要STA来保证触发器都能正确进行采样

假设动态仿真验证到了所有功能点,就不需要进行STA了(触发器都确保已经正常工作)

二、基本概念

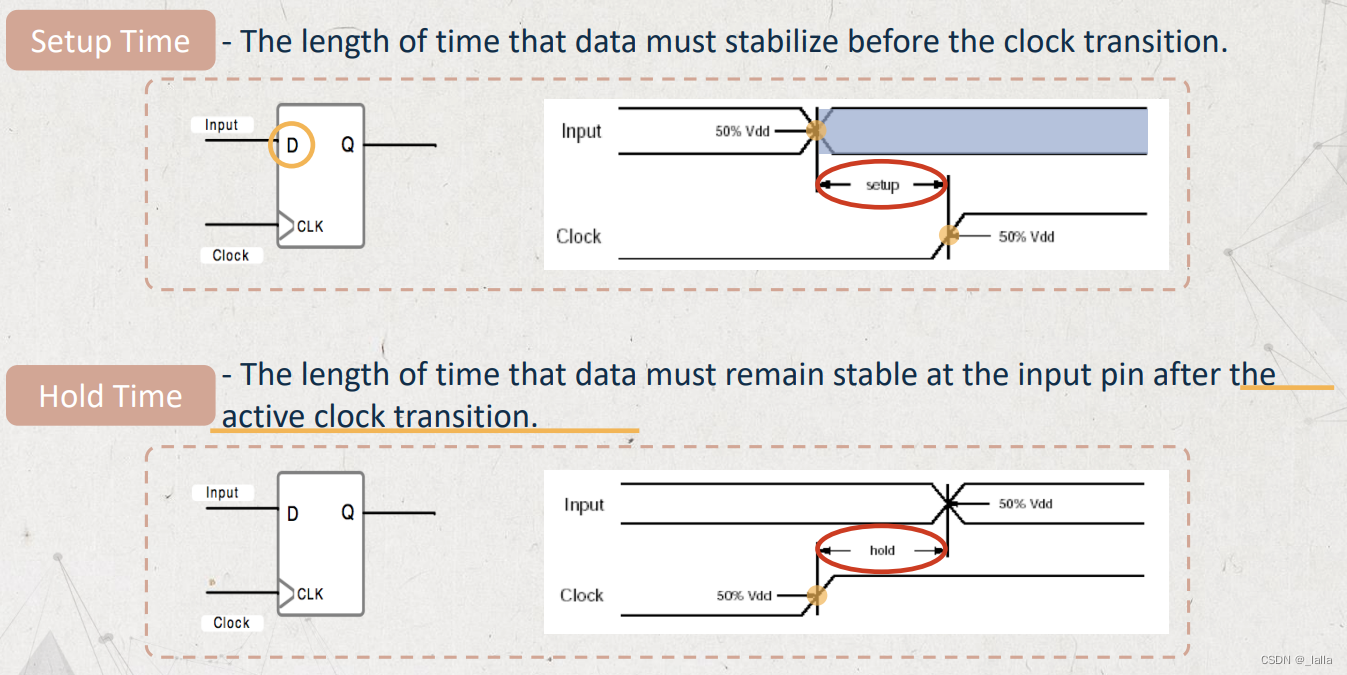

1、建立时间、保持时间

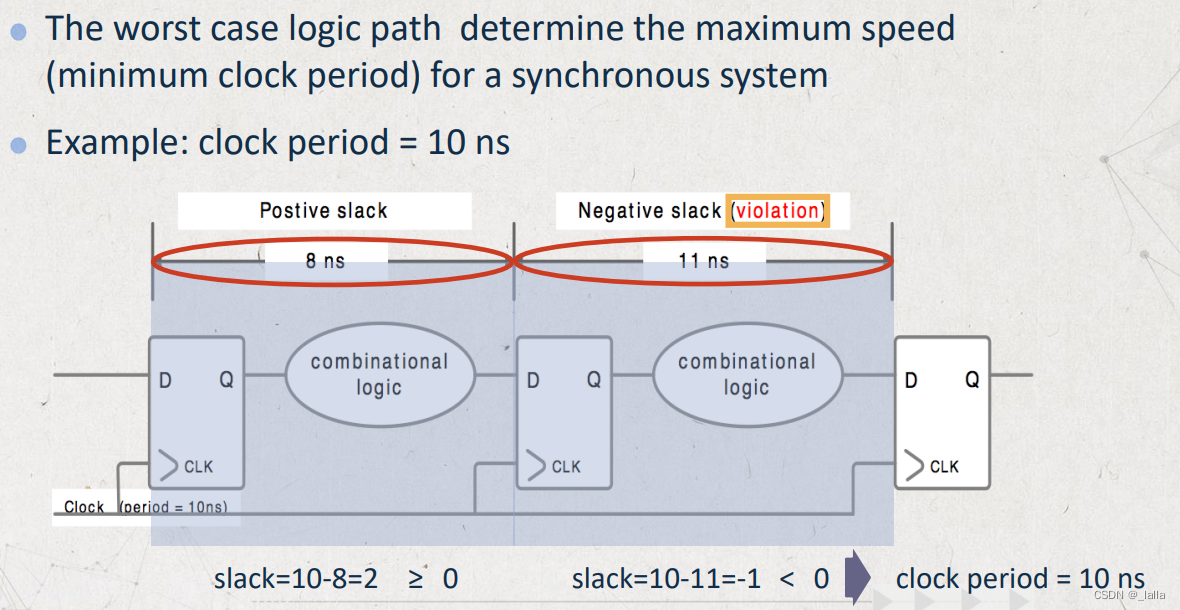

2、裕量Time Slack

裕量 = 数据实际到达的时间 - 建立时间 / 保持时间

裕量 > 0 :满足时序要求

裕量 < 0 :不满足,违例

(1)电路时钟/时钟频率/电路速度

单位时间内翻转次数,翻转次数越多,数据计算量越大。一般由最差的一条时序路径决定,裕量和clk是相关的

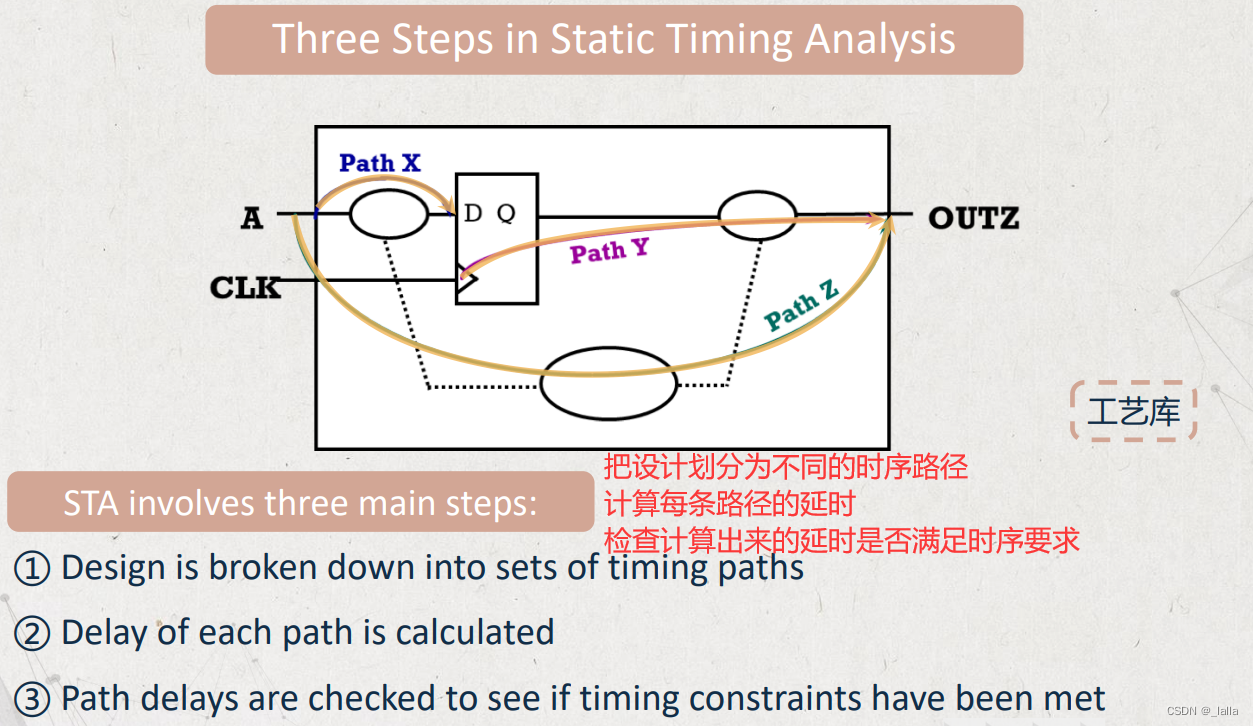

(2)STA步骤

逻辑综合阶段也有时序报告,和此处的静态时序分析有什么区别?

答:逻辑综合阶段是假设时钟是理想的没有延迟。STA在逻辑综合、布局布线、时钟树综合这些步骤都要做,越往后越准确,算出来的时钟网络延迟越接近实际结果。

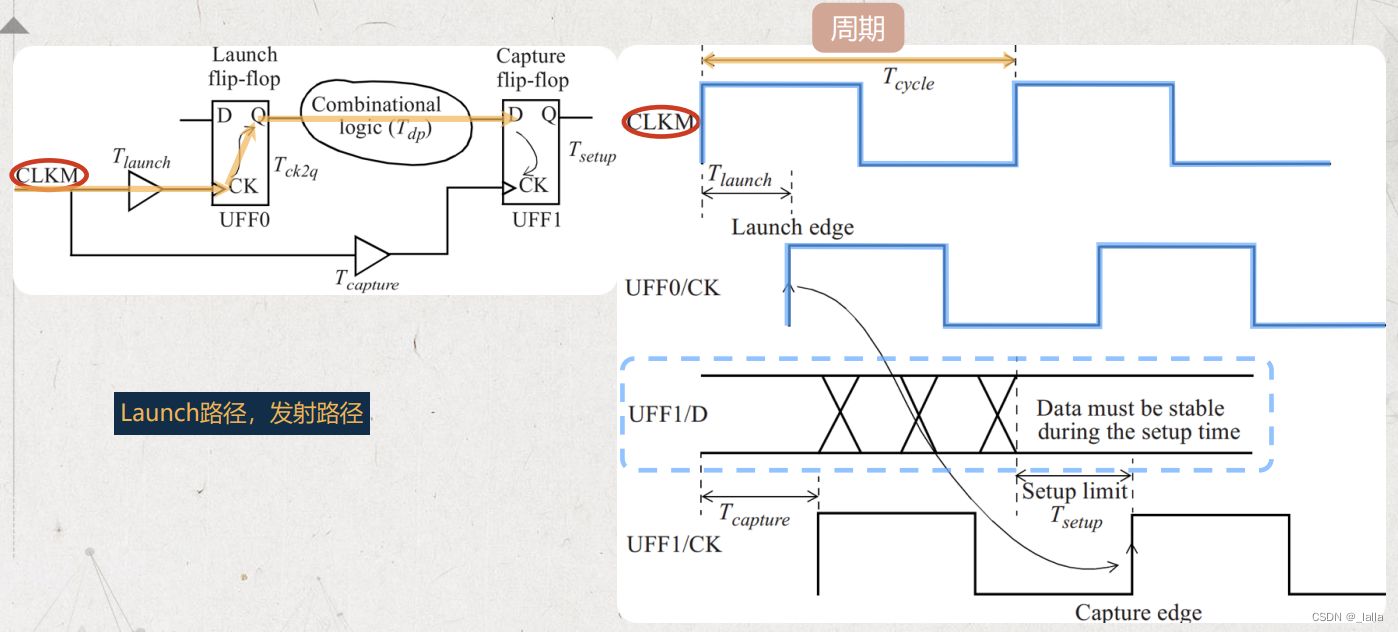

三、建立时间的检查

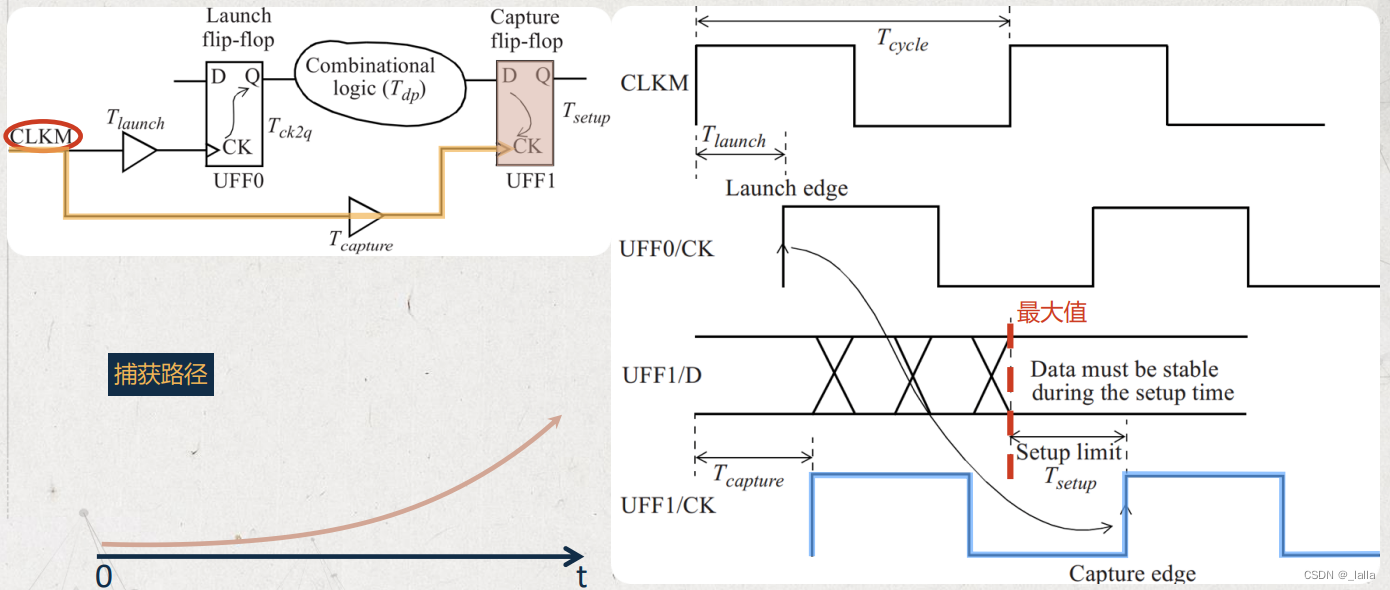

(1)发射路径、捕获路径

第一种路径是寄存器clk到寄存器D

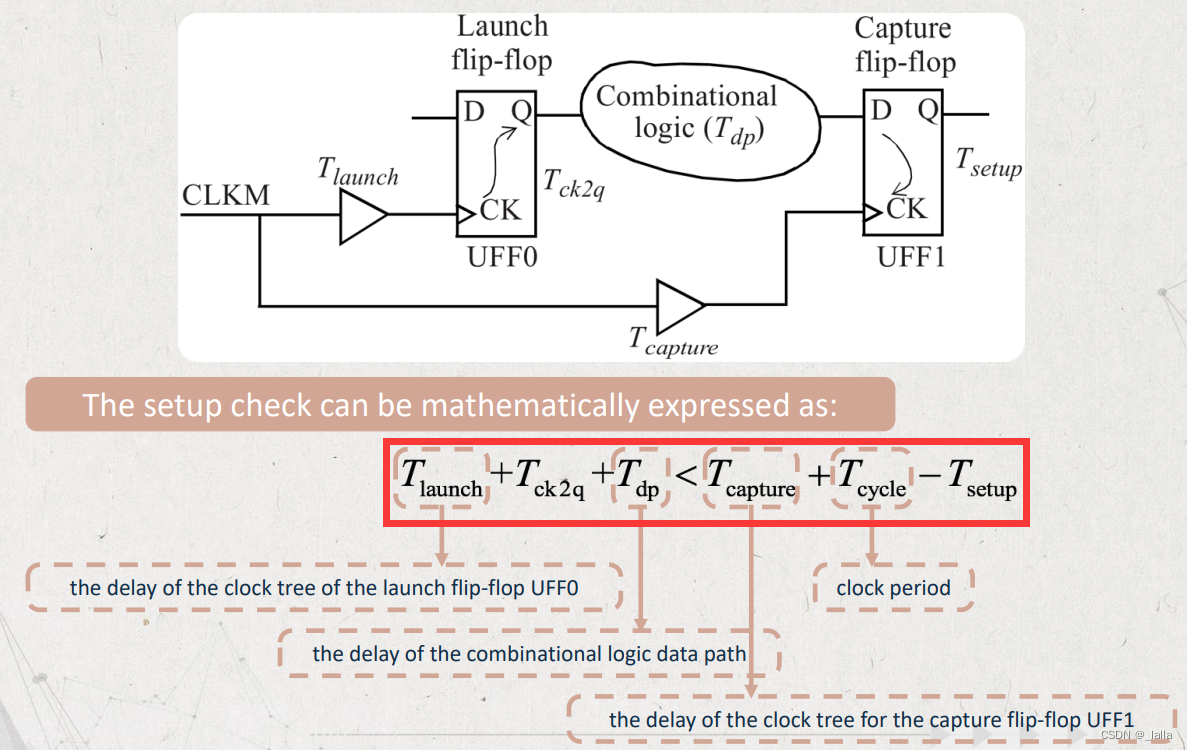

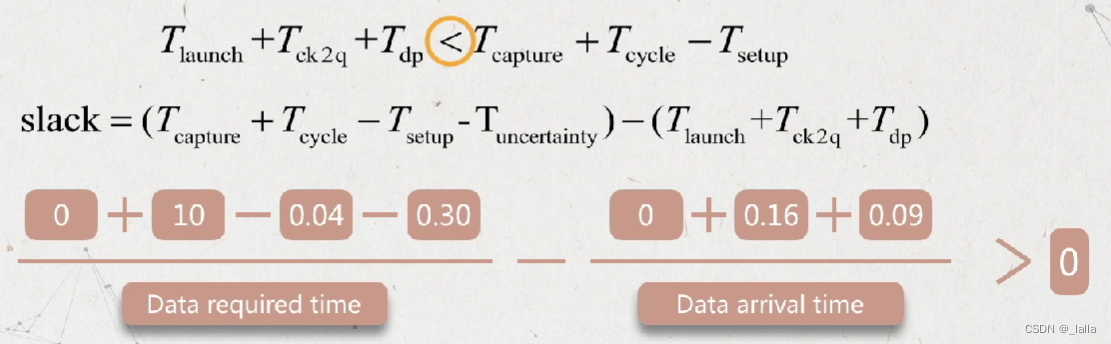

判断建立时间是否满足的公式(非常重要)

为什么要去最大值来进行判断?

答:时钟树的发射和捕获延迟时间是很小的,Tcq和Tsu是工艺库决定的,是固定值。要想下面等式成立,要取左边的最大值来进行判断

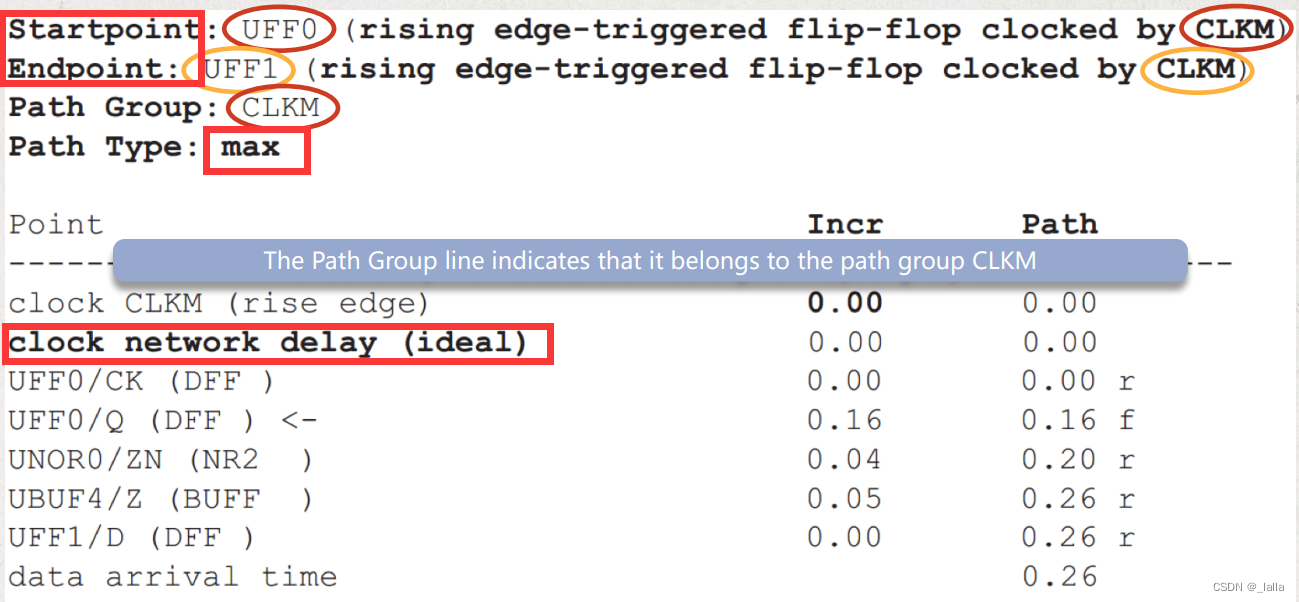

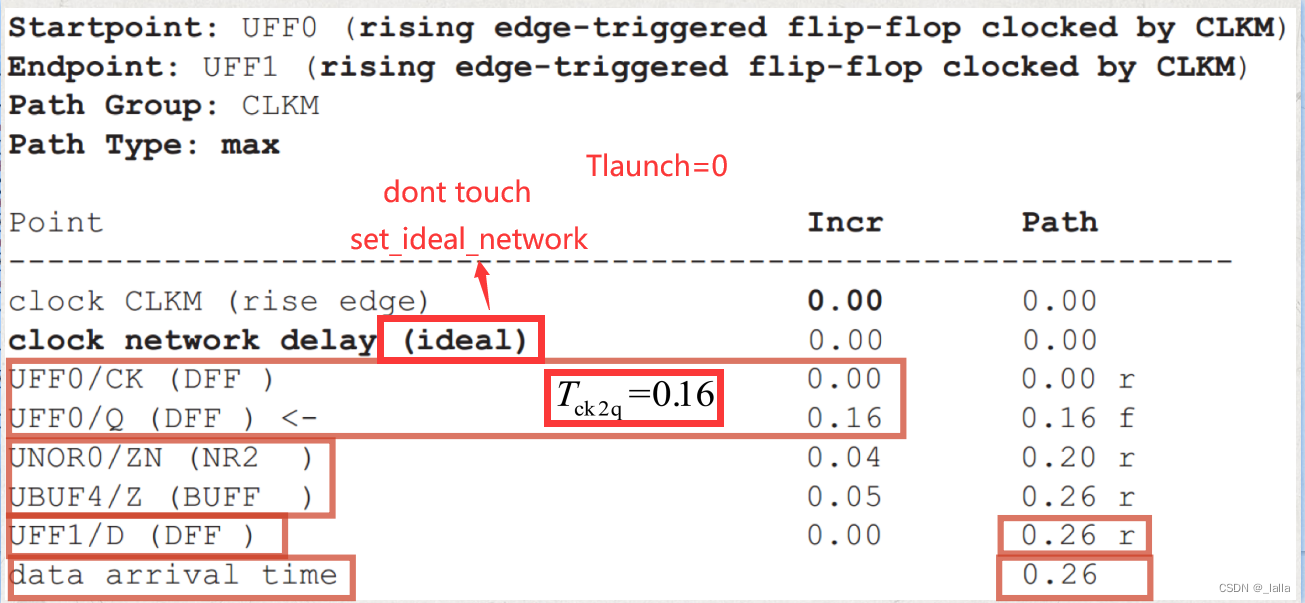

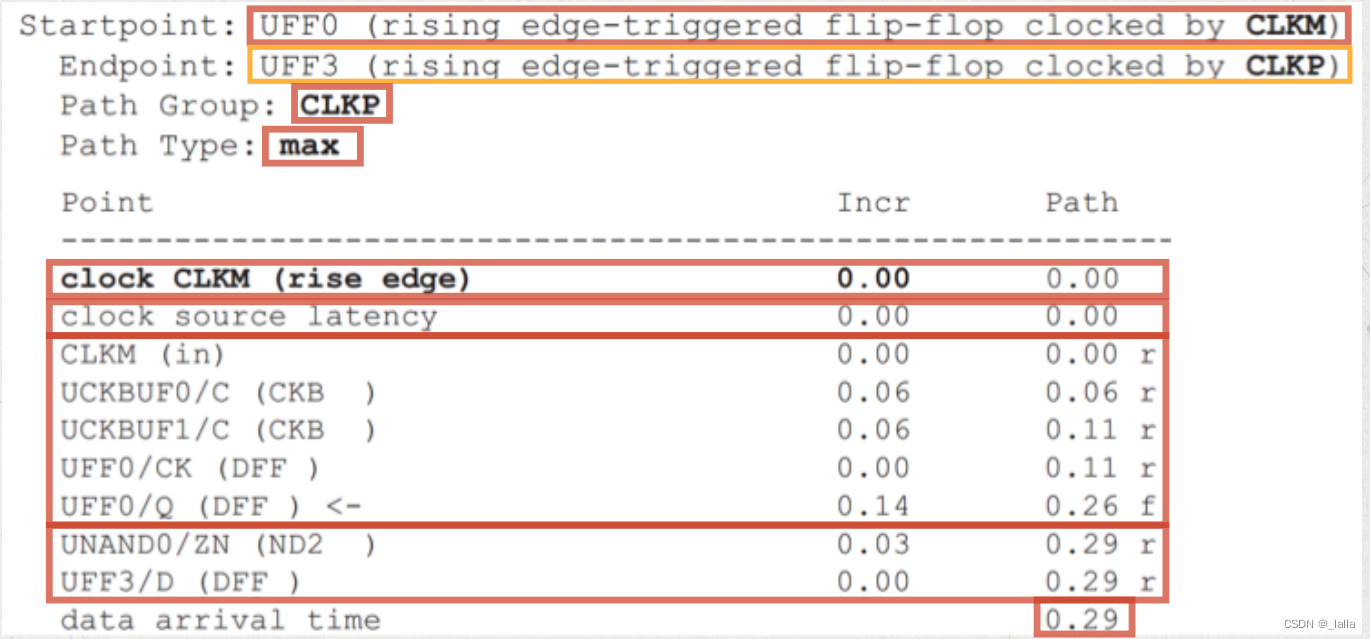

Path Group:由终点所处的时钟所决定,在这里是CLKM

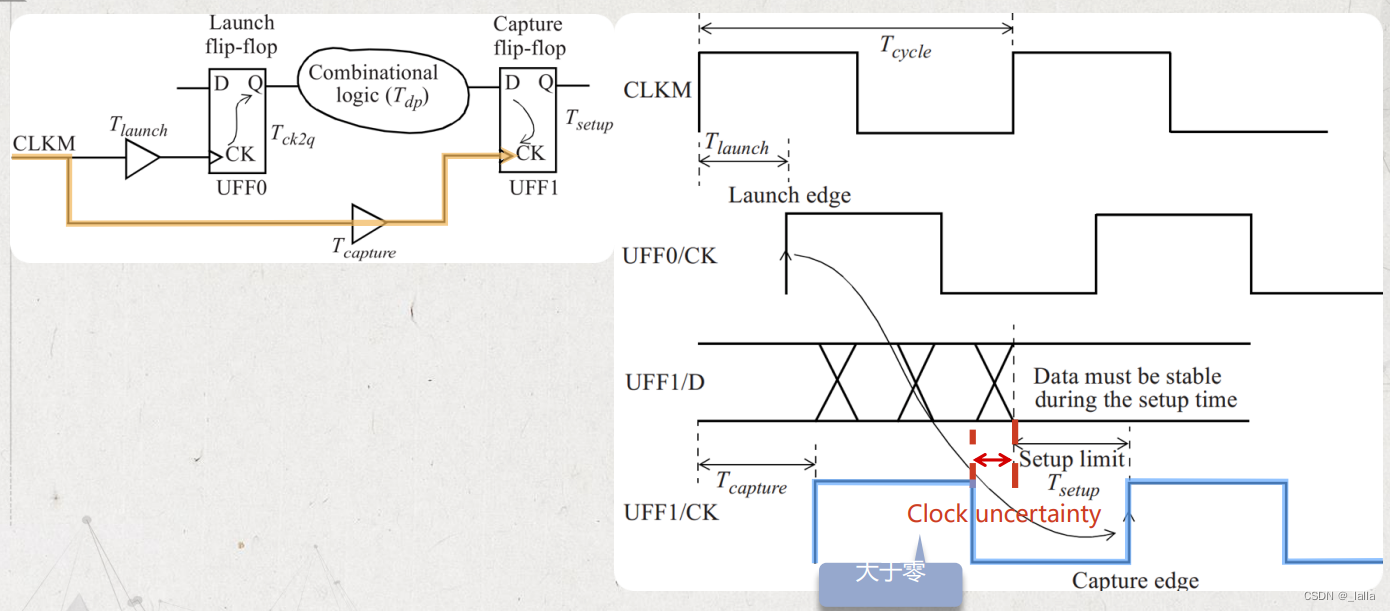

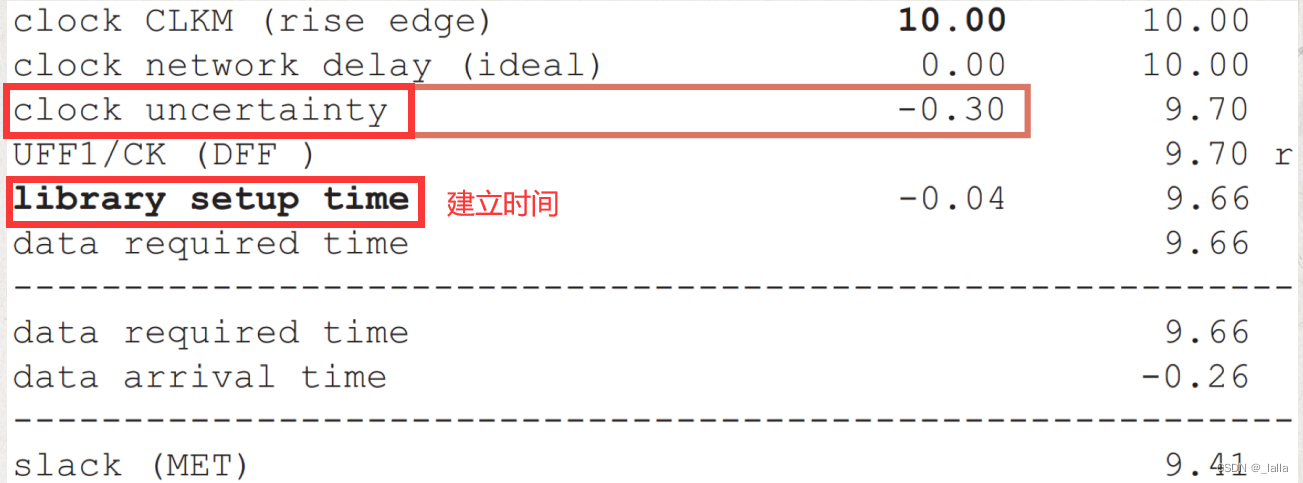

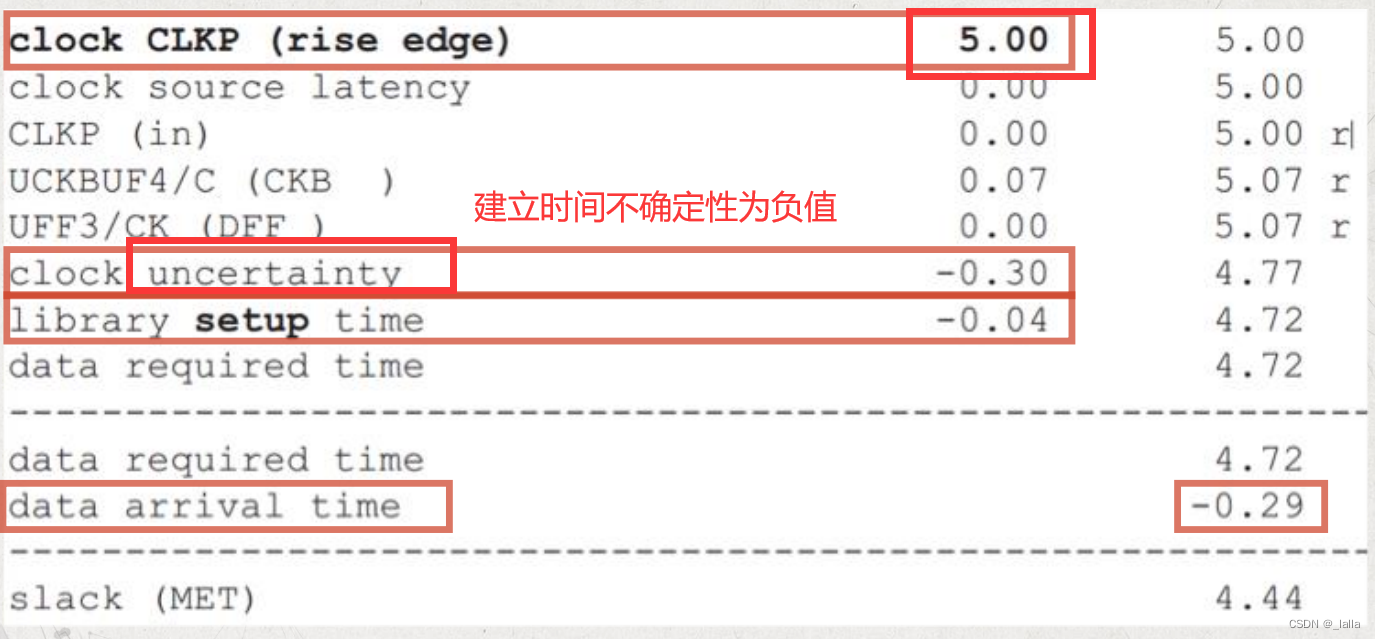

Clock Uncertainty:时钟不确定性,通常来说芯片在制造过程中存在很多的随机的偏差,如果我们此时在建立时间之前再将数据需要稳定的时间提前一些,以此来模拟芯片实际生成中的偏差。如果clock uncertainty 大于零,就会导致一个比较严谨的建立时间时序约束。如果在uncertainty 大于零的情况下,数据依然能够稳定到达,那也就是说这个设计比较安全。

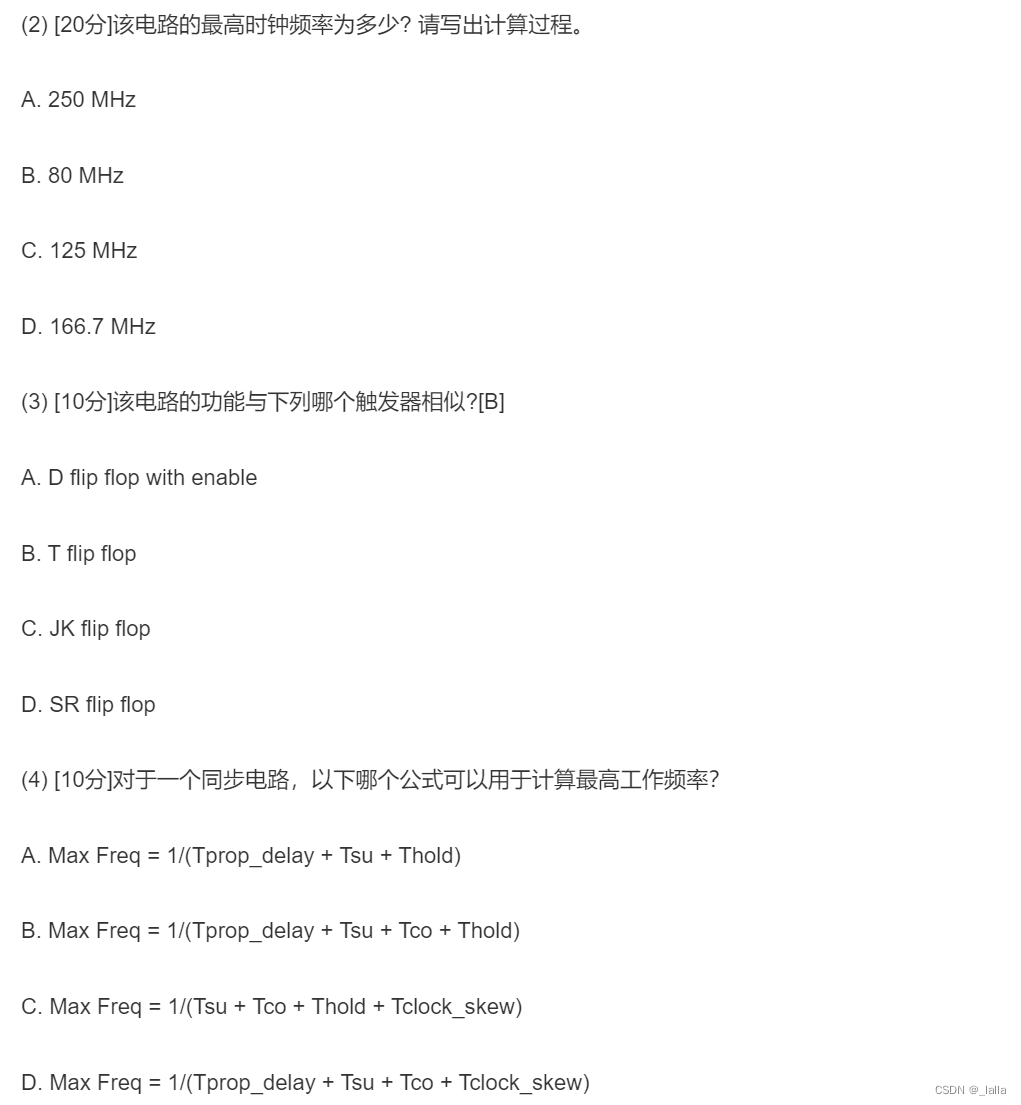

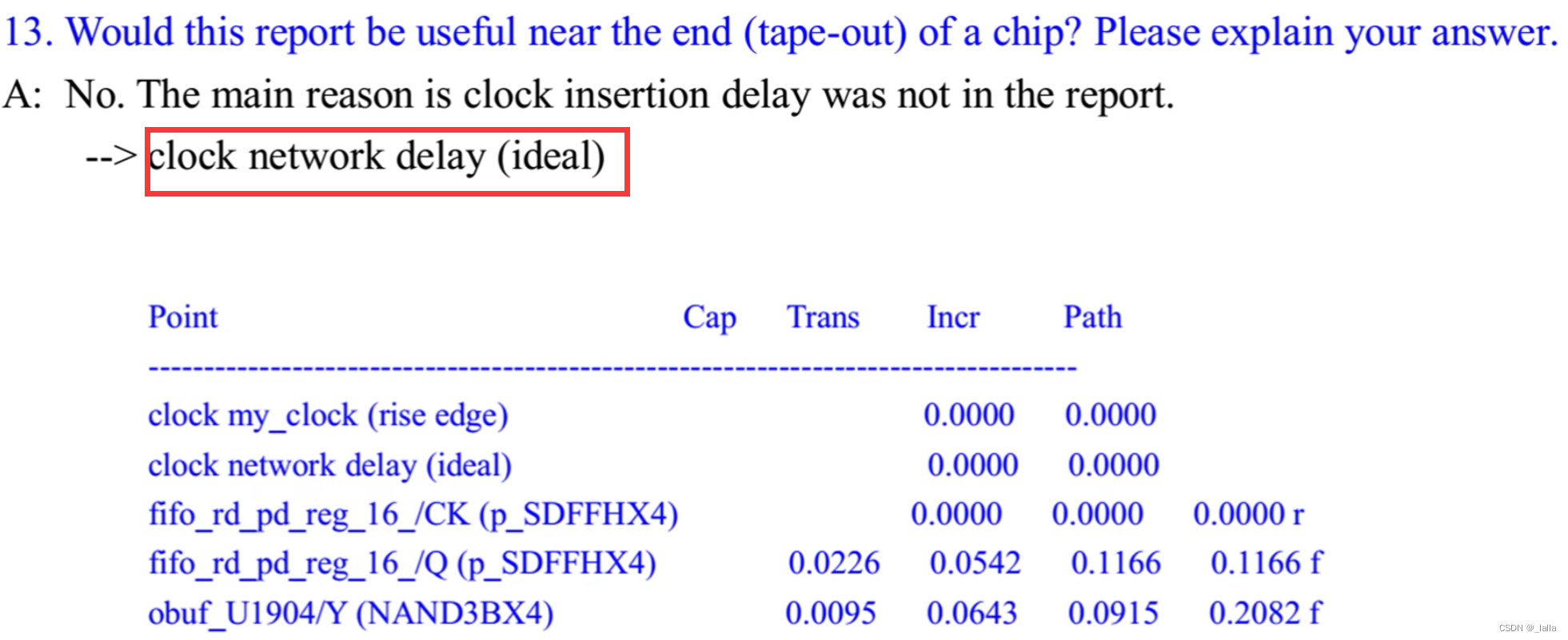

分析下面时序报告

(1)该报告可以看到时钟是理想的,所以可能是逻辑综合阶段的时序分析

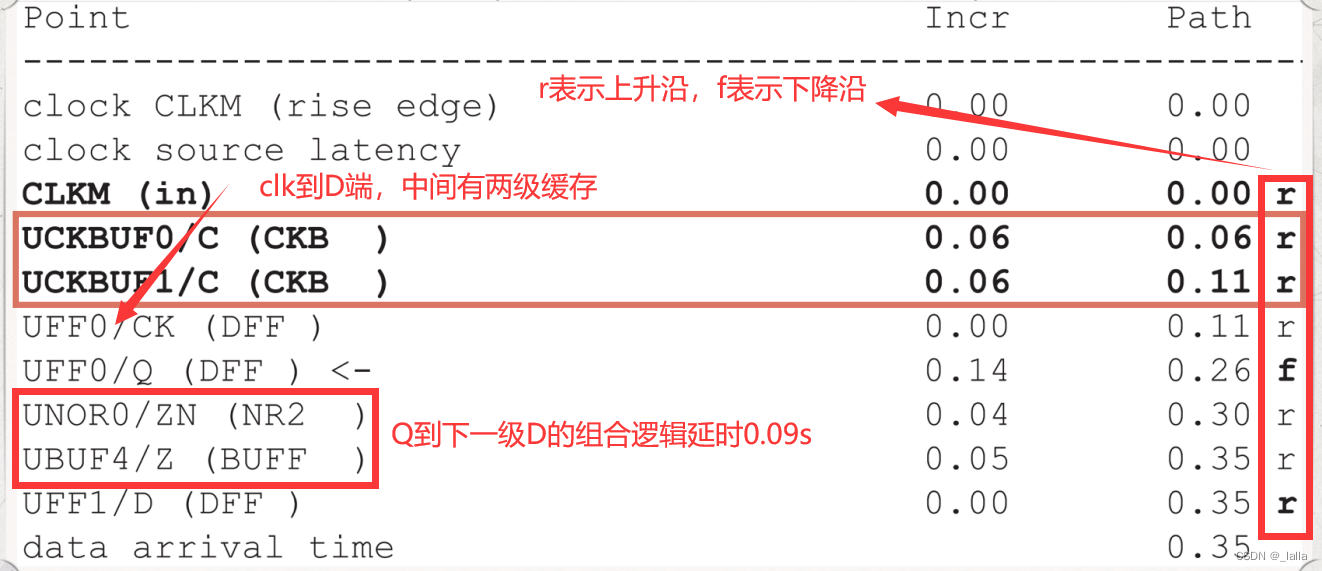

(2)非理想状态,存在时钟网络延时

时钟偏斜clock skew:数据发射路径和数据捕获路径的时钟延时之差

时钟网络的延迟:从内核端口到触发器的延迟

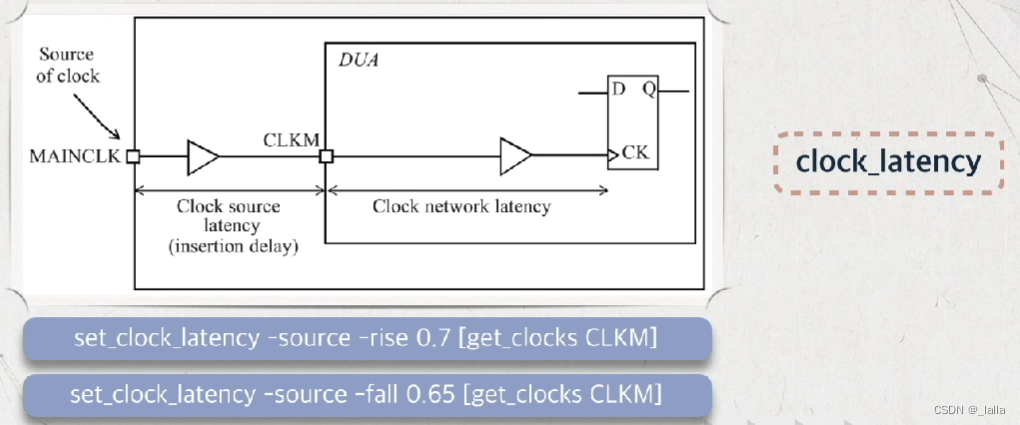

clock_latency:时钟从其源点传播到正在分析的设计的时钟定义点所需的时间,可以用 set_clock_latency 命令指定此延迟

(2)单周期建立时间的检查

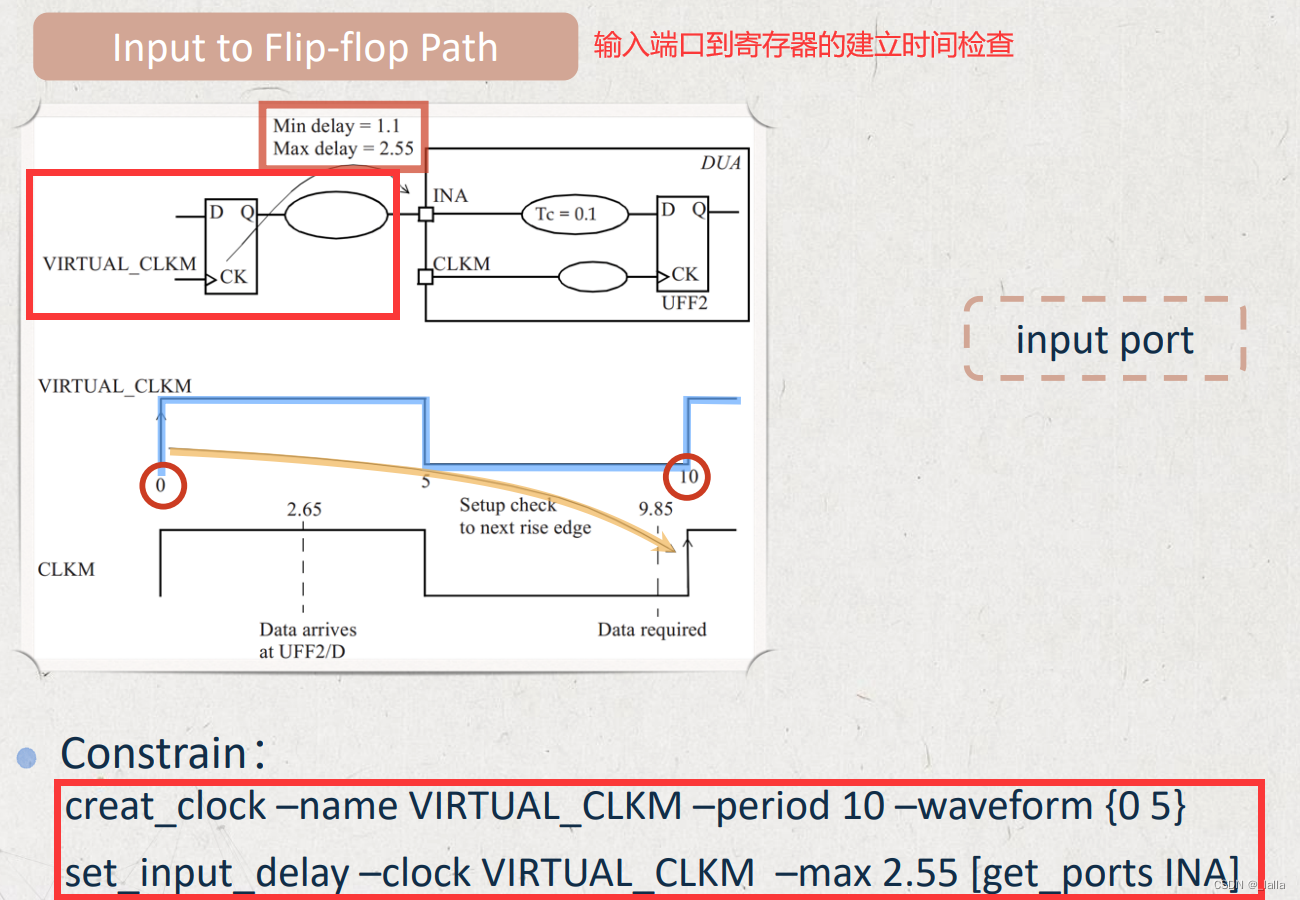

第二种:输入端到寄存器D端的建立时间

cell的延迟取决于input transition和output capacitance

第三种:寄存器clk端到输出端的建立时间

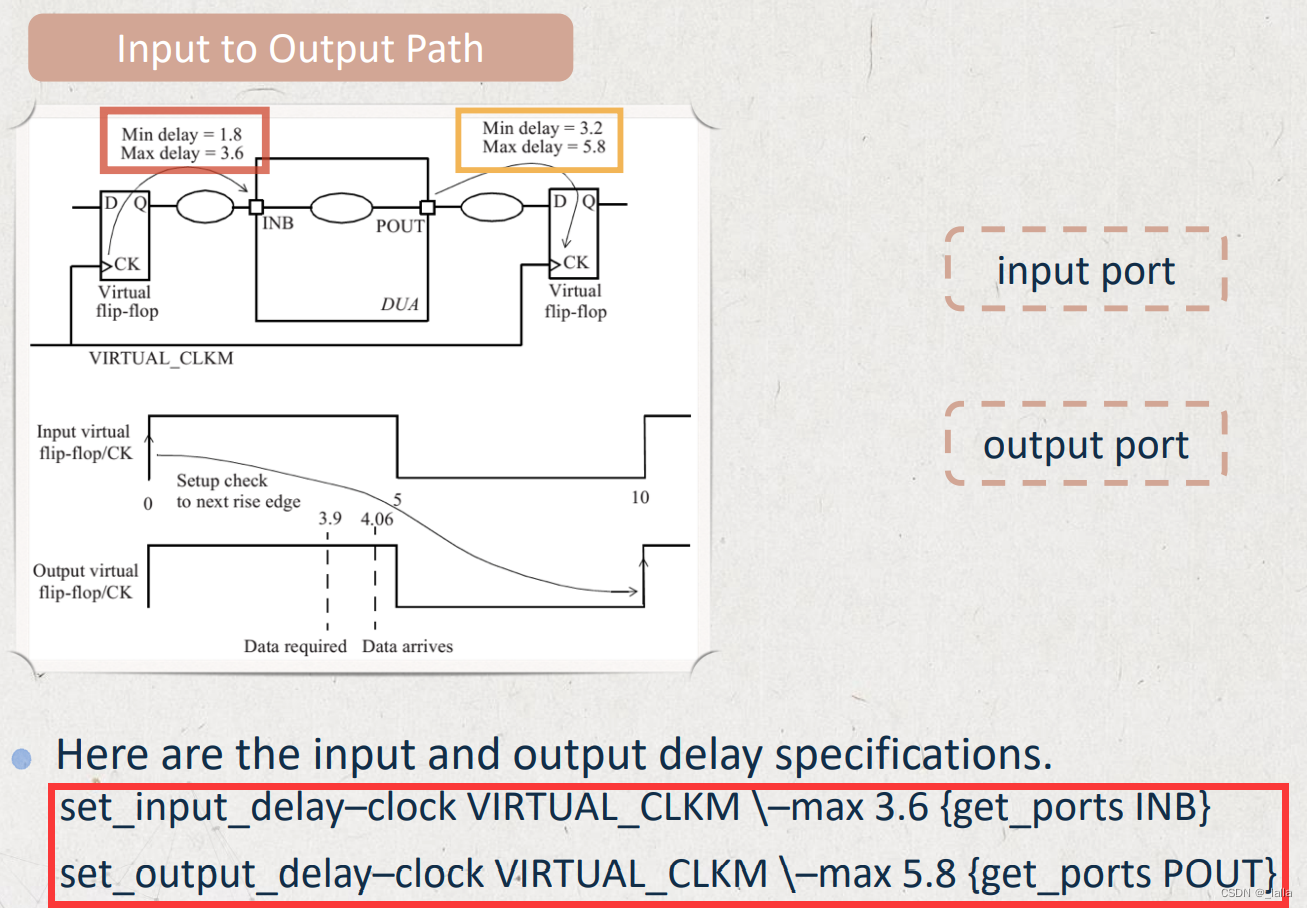

第四种:输入端到输出端的建立时间

优化方法:对组合逻辑电路进行优化

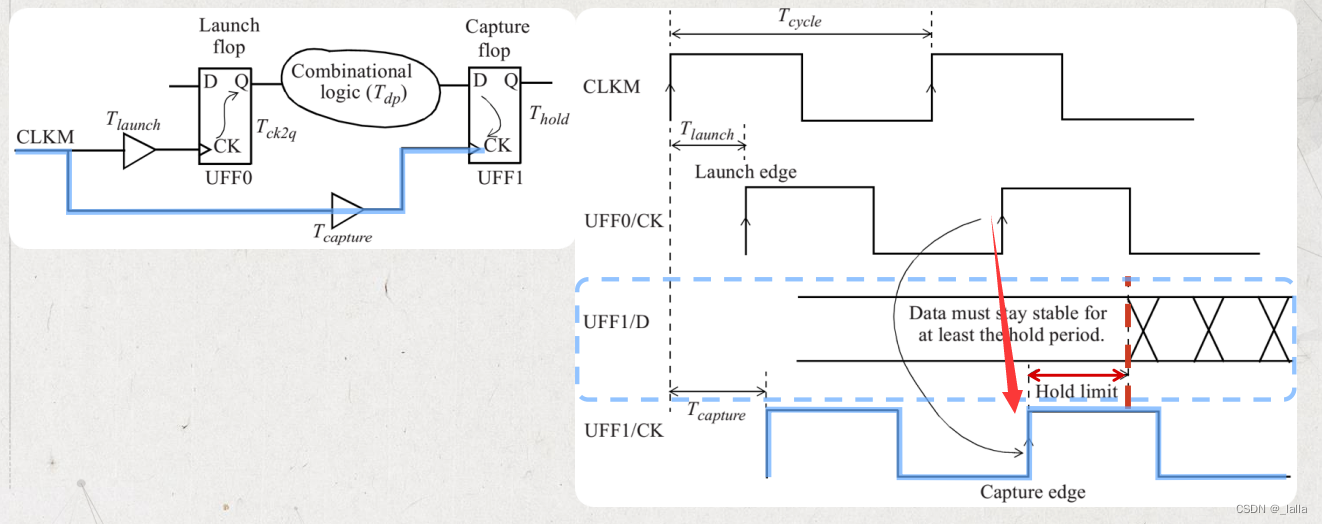

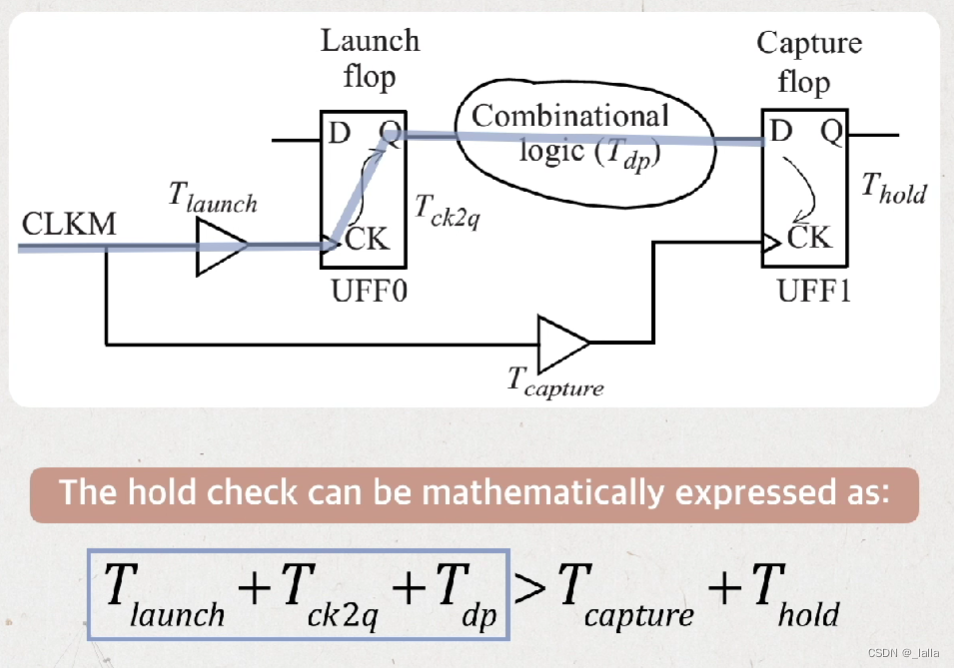

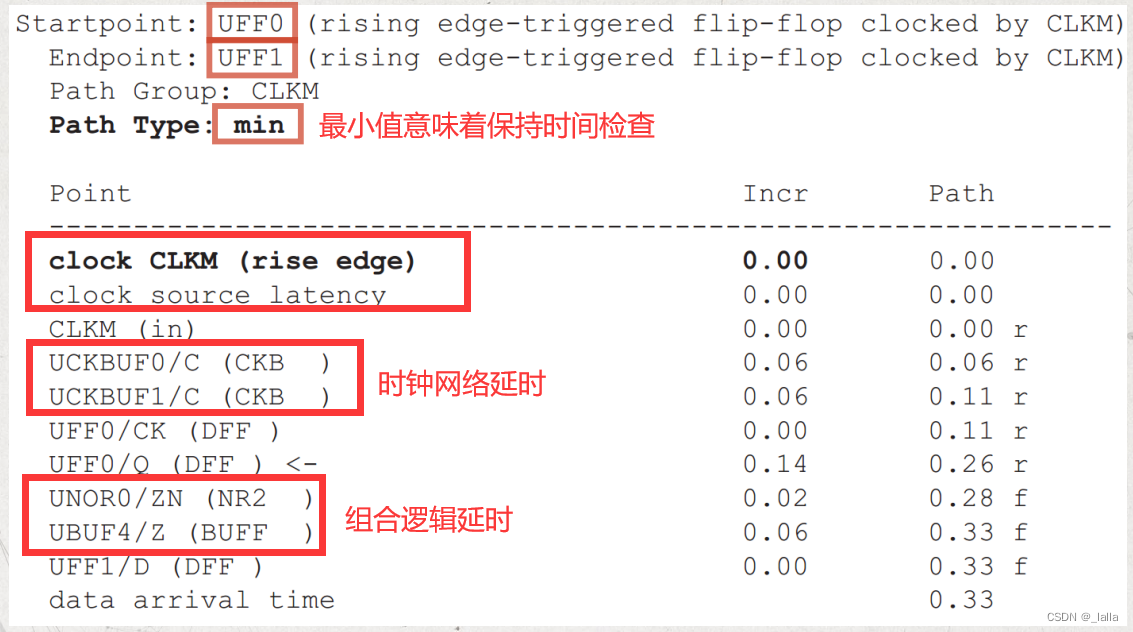

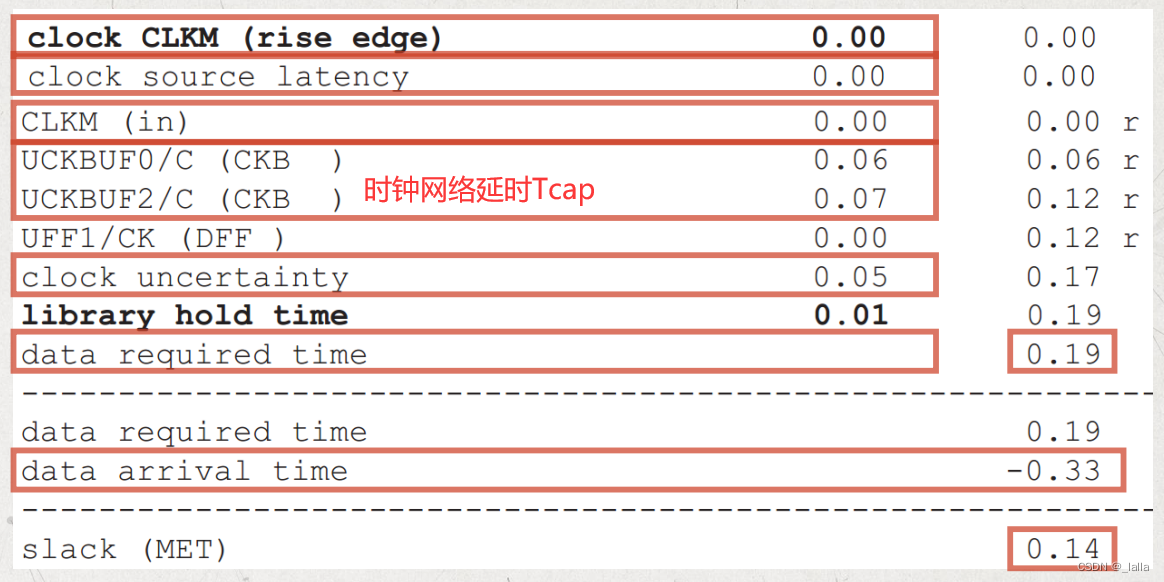

四、保持时间的检查

1、保持时间和建立时间检查区别

(1)保持时间是在同一时钟边沿进行检查,数据的发射路径和接收路径是同一时钟边沿。建立时间数据捕获路径要比发射路径晚一个时钟周期,不在同一时钟沿检查。

(2)保持时间检查与时钟周期无关。如果要计算一个电路的时钟周期,只能从建立时间去计算。

对于保持时间,上面的数据发射路径的时间要大于下面的捕获时间,数据要维持到捕获之后;而对于建立时间,则是上面发射路径时间要小于捕获路径时间,要求捕获之前数据已经达到了。

clock uncertainty:对于建立时间来说,这个值是负数;对于保持时间,这个值是正数。

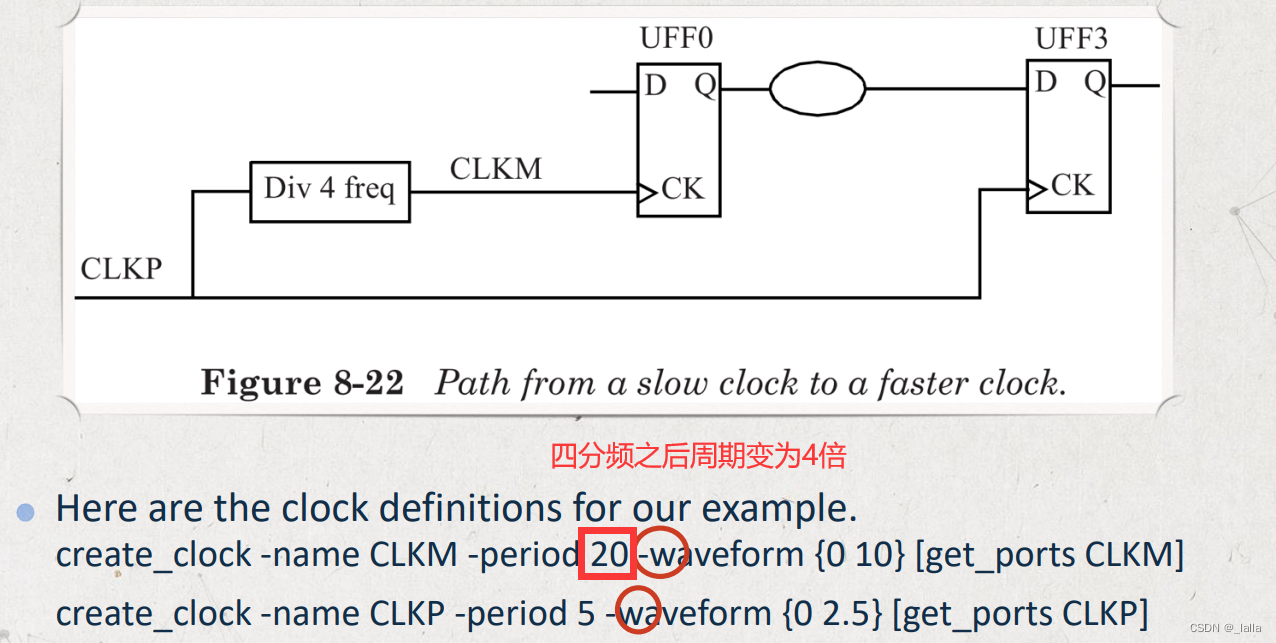

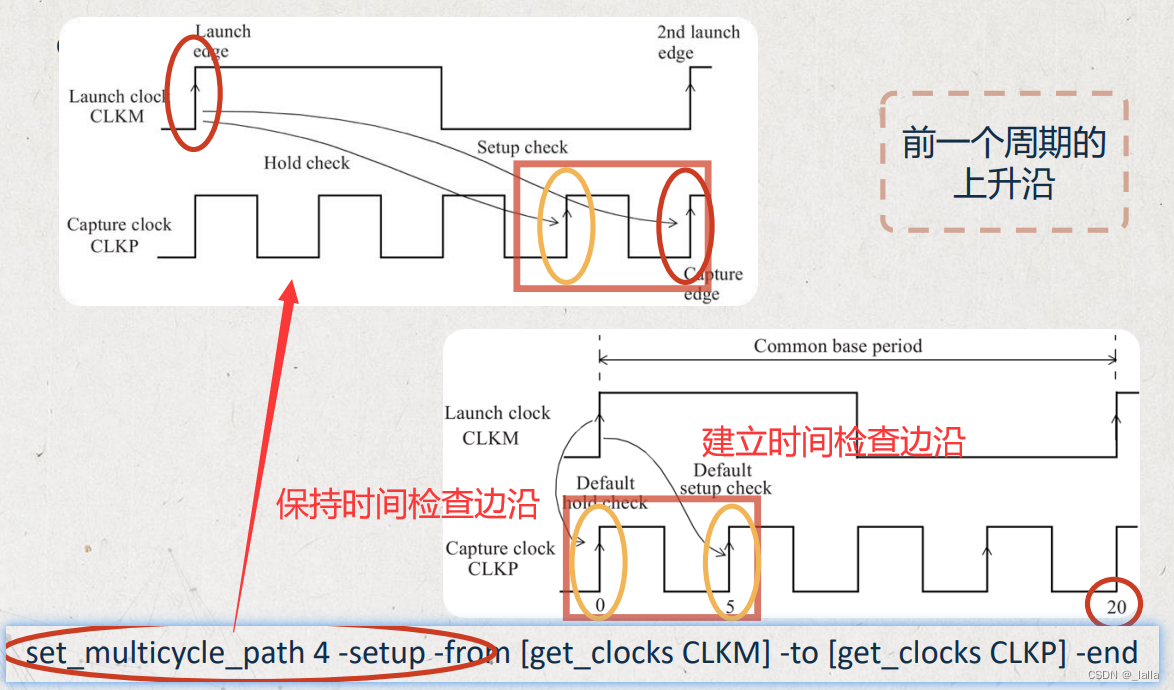

五、快慢时钟交互路径建立时间和保持时间检查

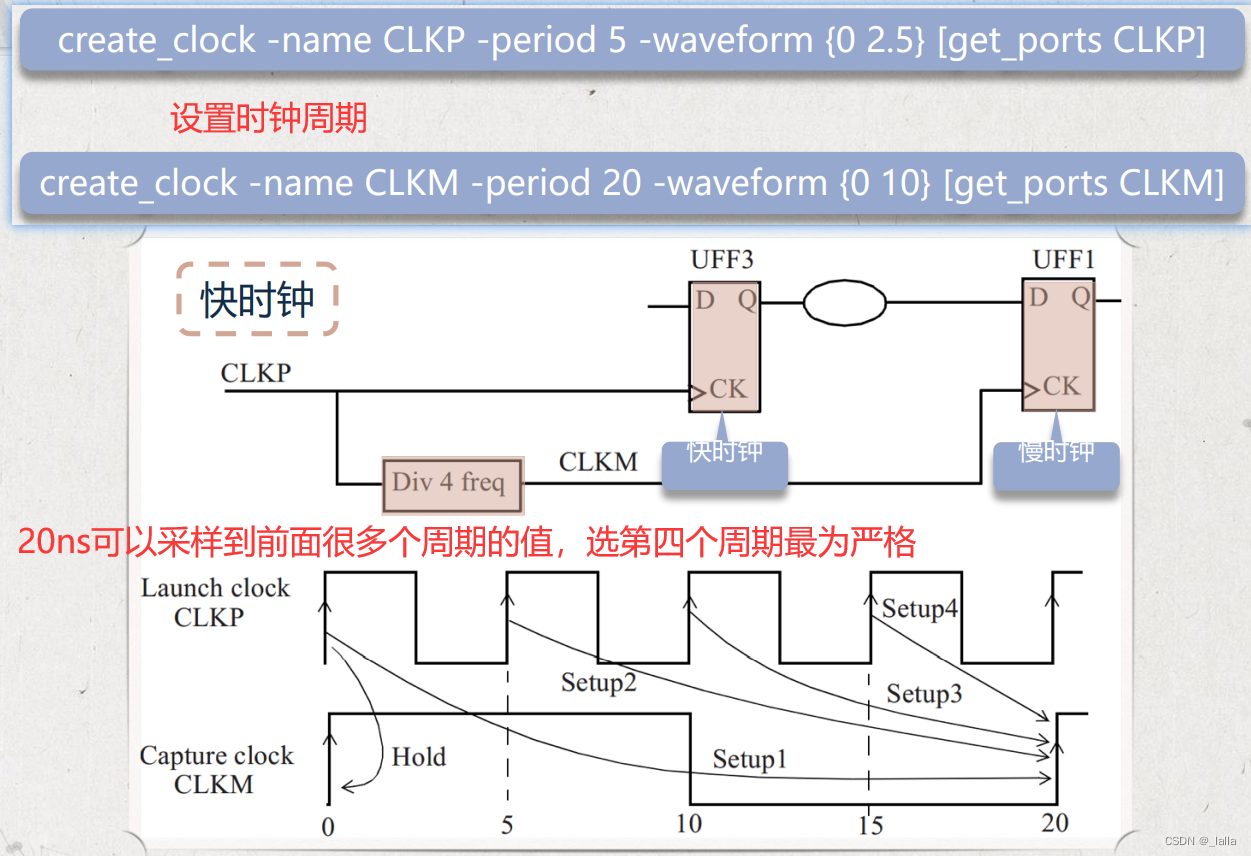

1、慢时钟到快时钟

快时钟和慢时钟起点是相同的,在第一个快时钟边沿采用是最为严格的,这样留给组合逻辑的时间是很少的。而在大多数情况下,组合逻辑的延时甚至比慢时钟的一个周期还要长,所以有时候也可以放宽要求,可以用指令设置在第四个周期检查。

(1)建立时间检查

数据发射路径

数据捕获路径:最后结果是正数,表面满足时序要求

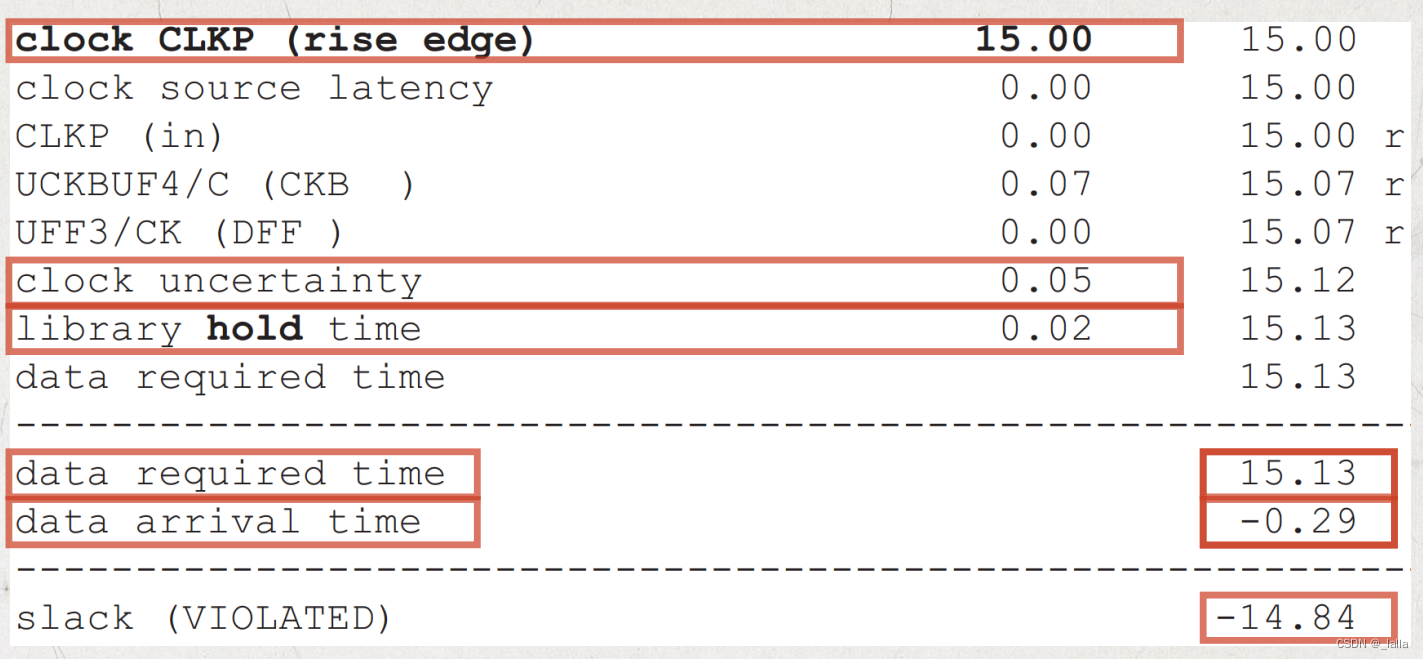

(2)保持时间检查

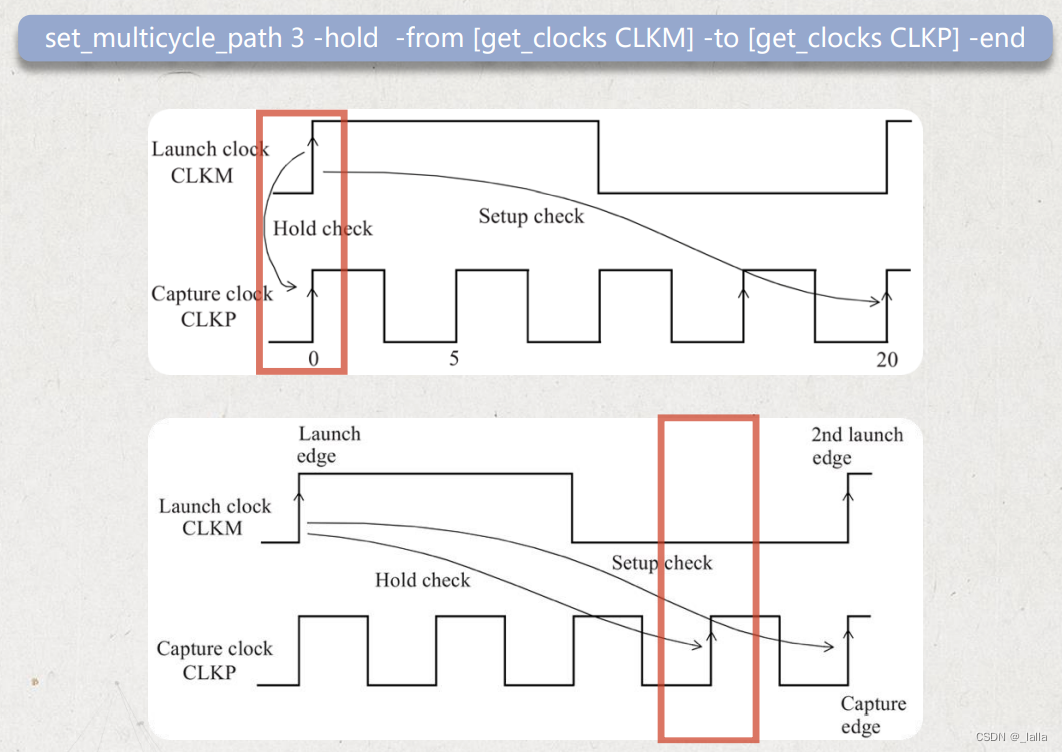

发现保持时间是违例的,所以需要将保持时间检查的边沿向前提前几个周期

设立为第四个时钟周期检查,所以是20 ns的时候

总结:慢时钟到快时钟,在第N个检查建立时间,提前N-1个周期检查保持时间

-end选项是对时序进行约束,修改多时钟周期的约束,调整建立时间和保持时间的检查时间点

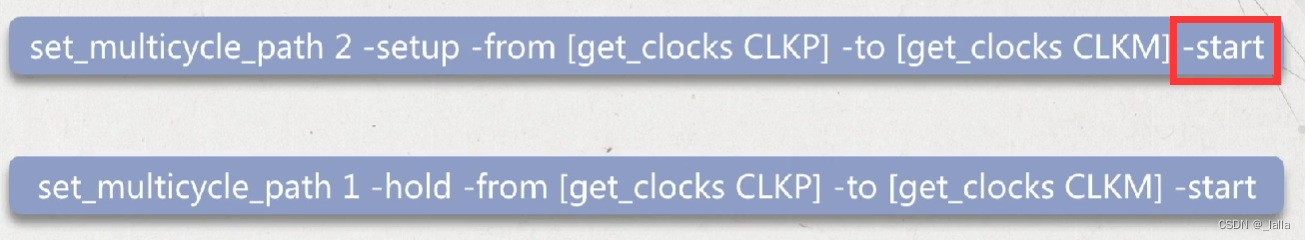

2、快时钟到慢时钟

此处使用的是start选项进行设置

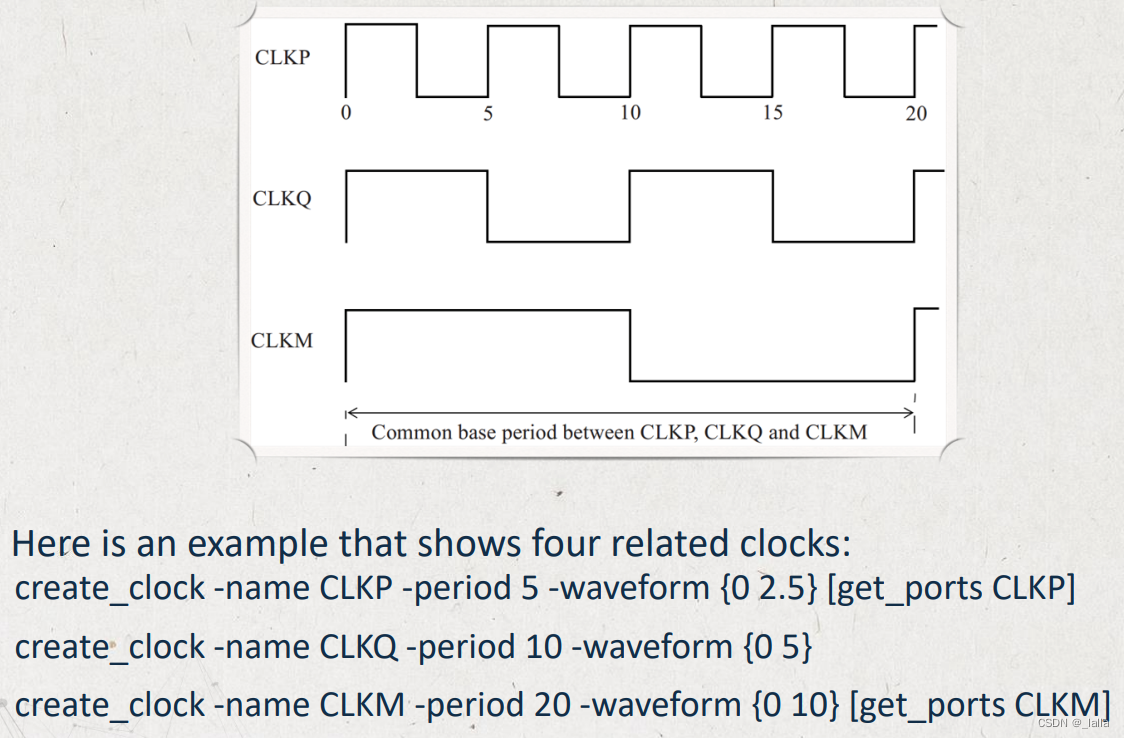

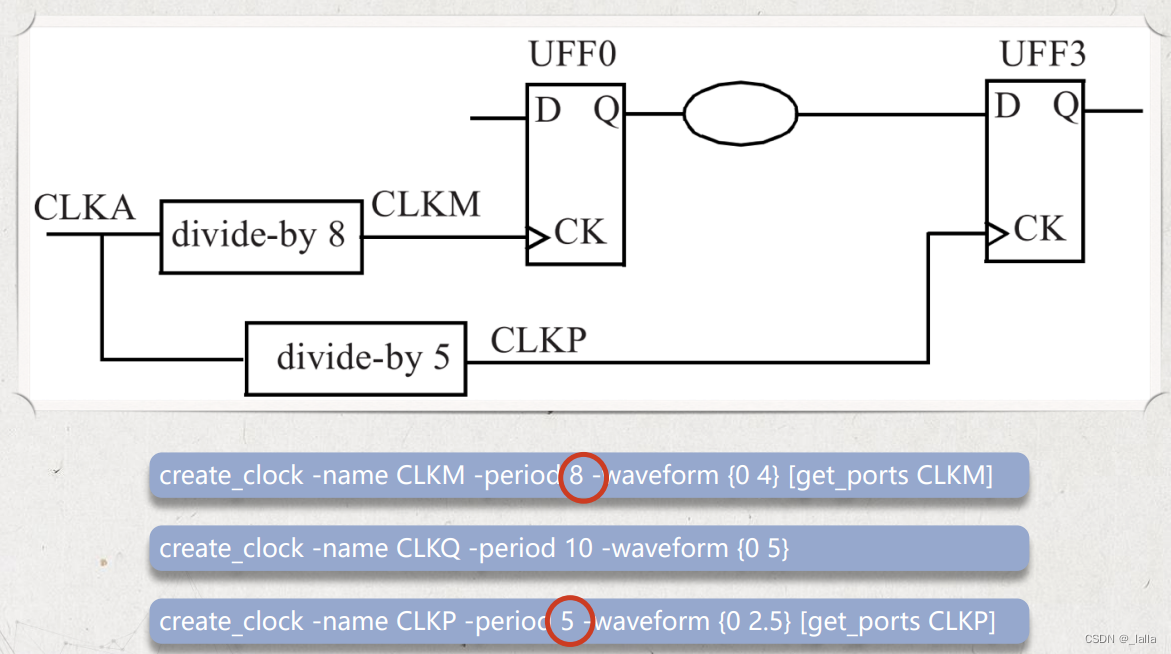

六、多时钟域的静态时序分析

1、时钟频率是整倍数关系

分析的方法和前面快慢时钟交互路径的检查是相同的。

首先,是找到各个时钟的公共周期然后进行分析。

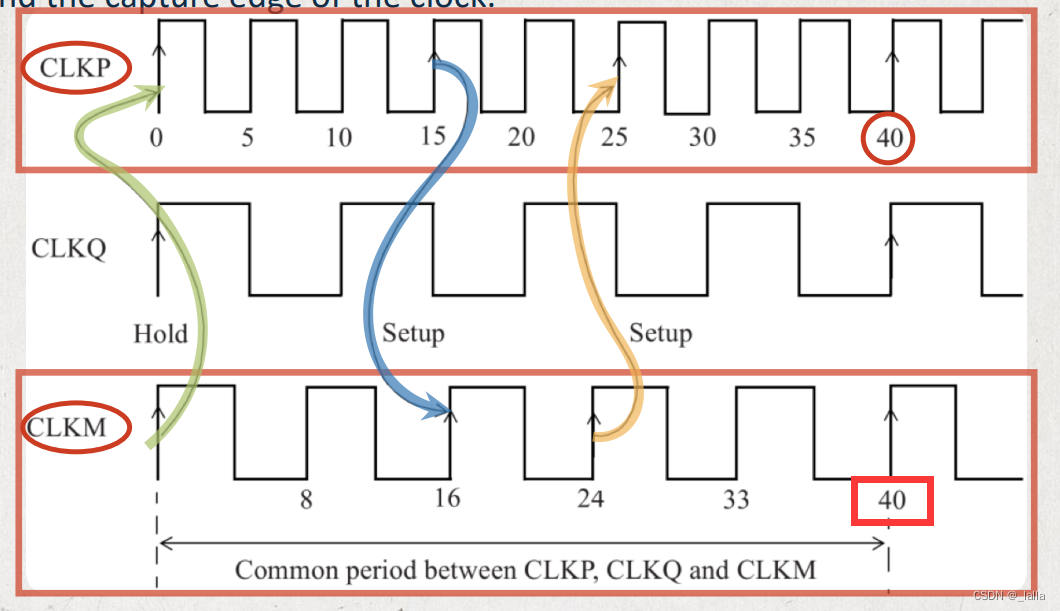

2、时钟频率是非整倍数关系

找到最小公倍数周期 40ns

建立时间:15ns发射数据,16ns捕获数据是最严格的

保持时间:24ns发射数据,25ns捕获数据是最严格的

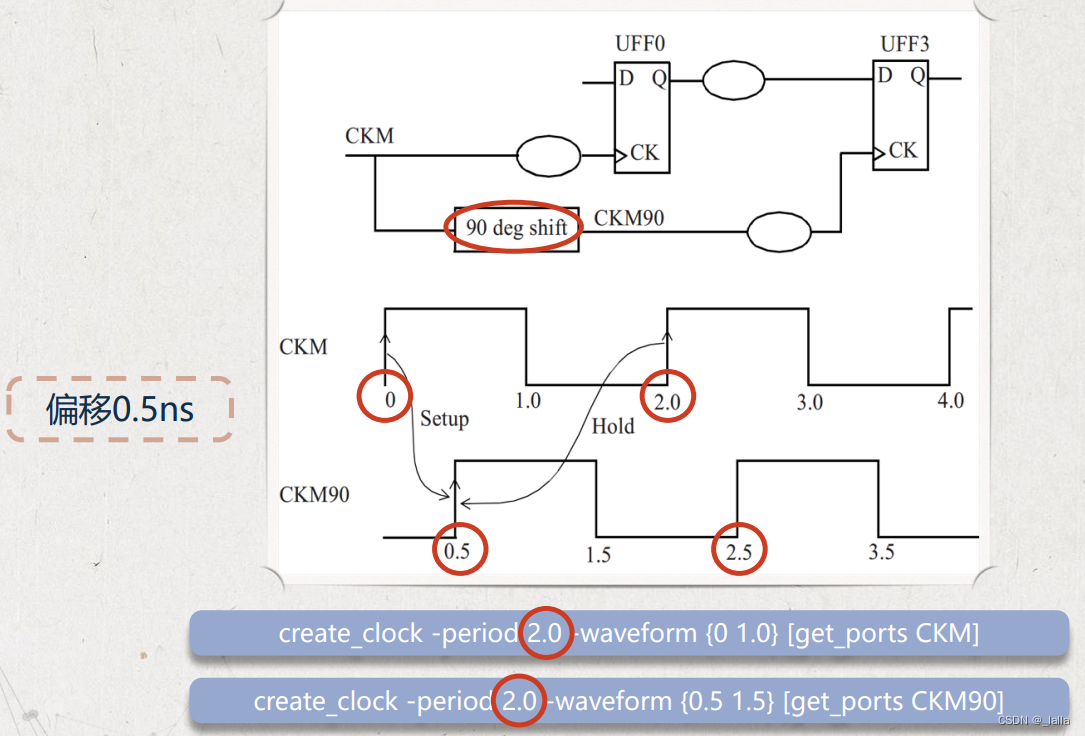

3、时钟相位不同

建立时间:0ns发射,0.5ns捕获是最严格的

保持时间:2ns发射,0.5ns捕获(发射的前一个周期捕获)

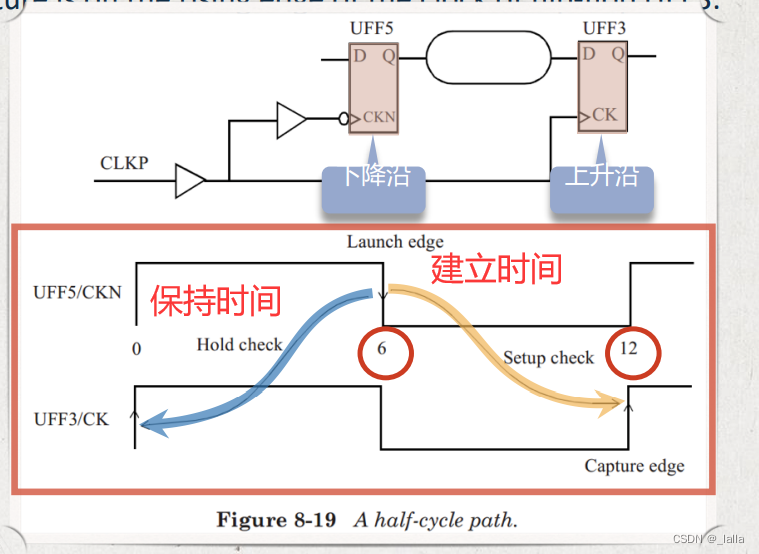

4、半周期时序路径

半周期:上升沿触发的触发器到下降沿触发的触发器

对于建立时间来说,只有半周期的时序,要求比较严格

对于保持时间来说,是比较友好的,采样数据时间早就到来,数据保持时间很容易满足要求

建立时间优化方法比较多,通常让保持时间更友好一点

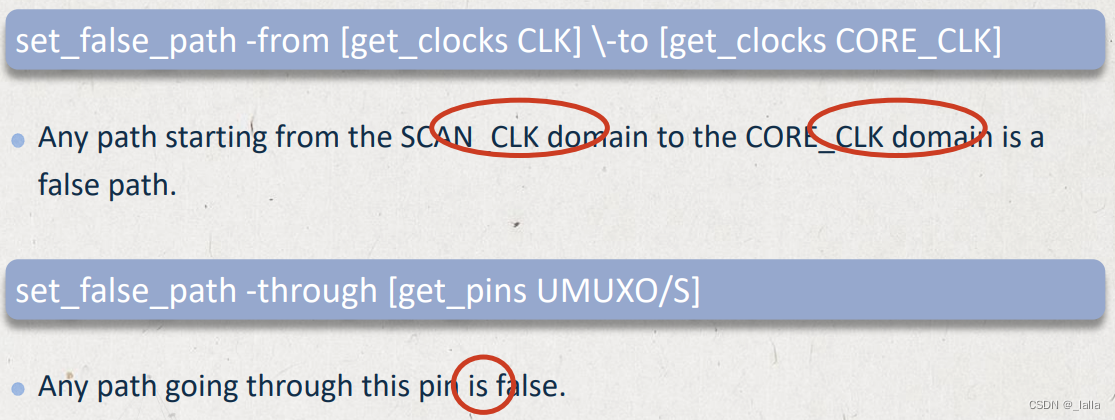

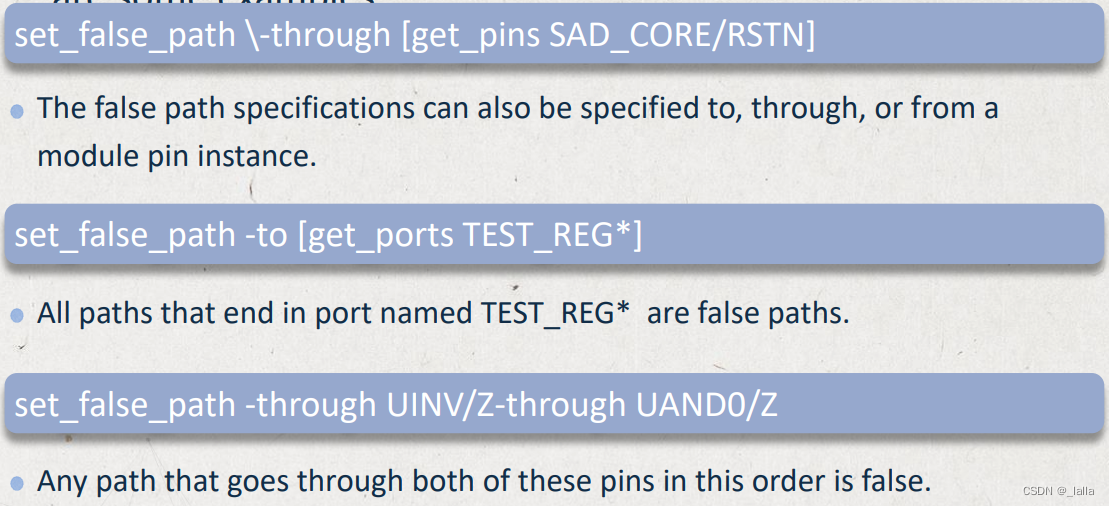

5、虚假路径

定义:某些不可能存在/不切实际的路径,减去它们可以减少时序分析的计算量

可以通过如下指令来进行设置

练习题

1、修setup time违例和hold time违例的常用方法都有哪些?

(1)修改时钟lunch和capture的值。比如要fix setup time违例,数据应该快速到达,launch时钟应快速到达,capture时钟应缓慢到达。要fix hold time违例,数据应该缓慢到达,launch时钟应缓慢到达,capture时钟应快速到达。

(2)修改组合逻辑的延时值。如果组合逻辑延迟较小则可能发生保持时间违例,可以在数据路径上插buffer,但需要注意不能够导致建立时间违例。

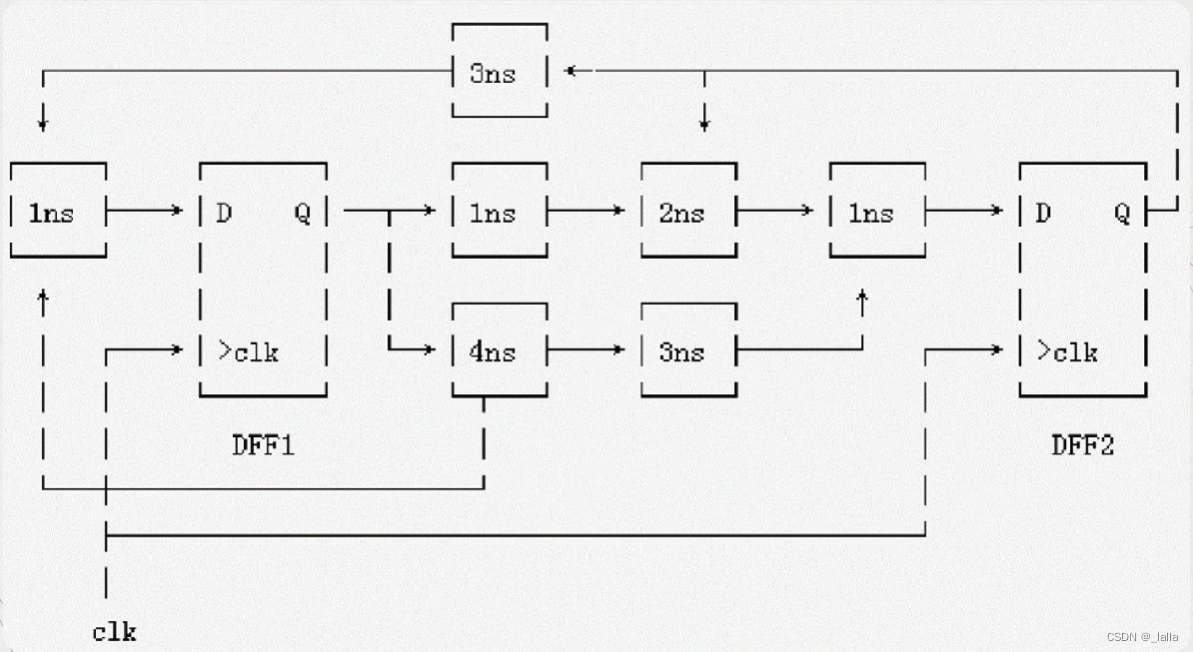

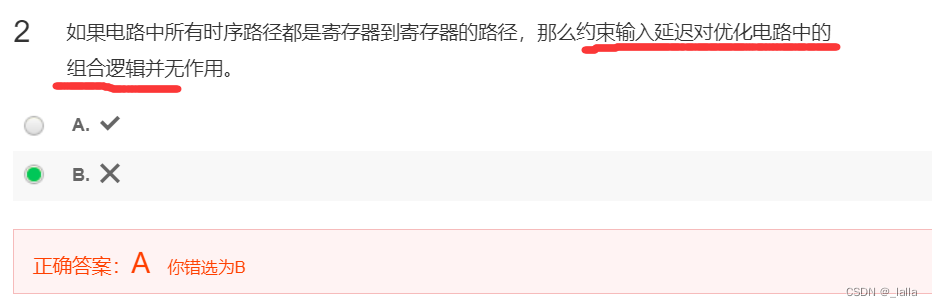

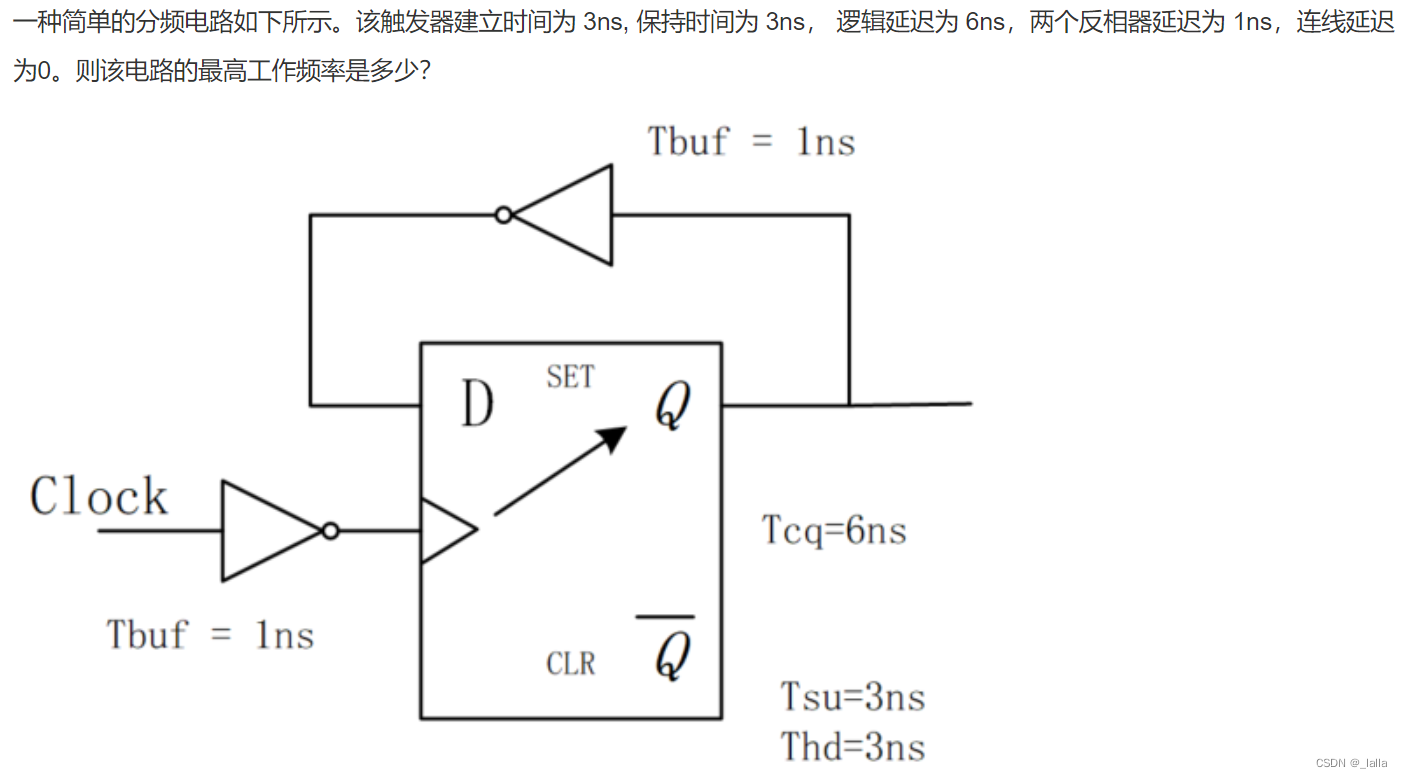

2、建立和保持时间例题(很重要!!!)

例1:

第二级触发器的建立和保持时间与第一级触发器无关

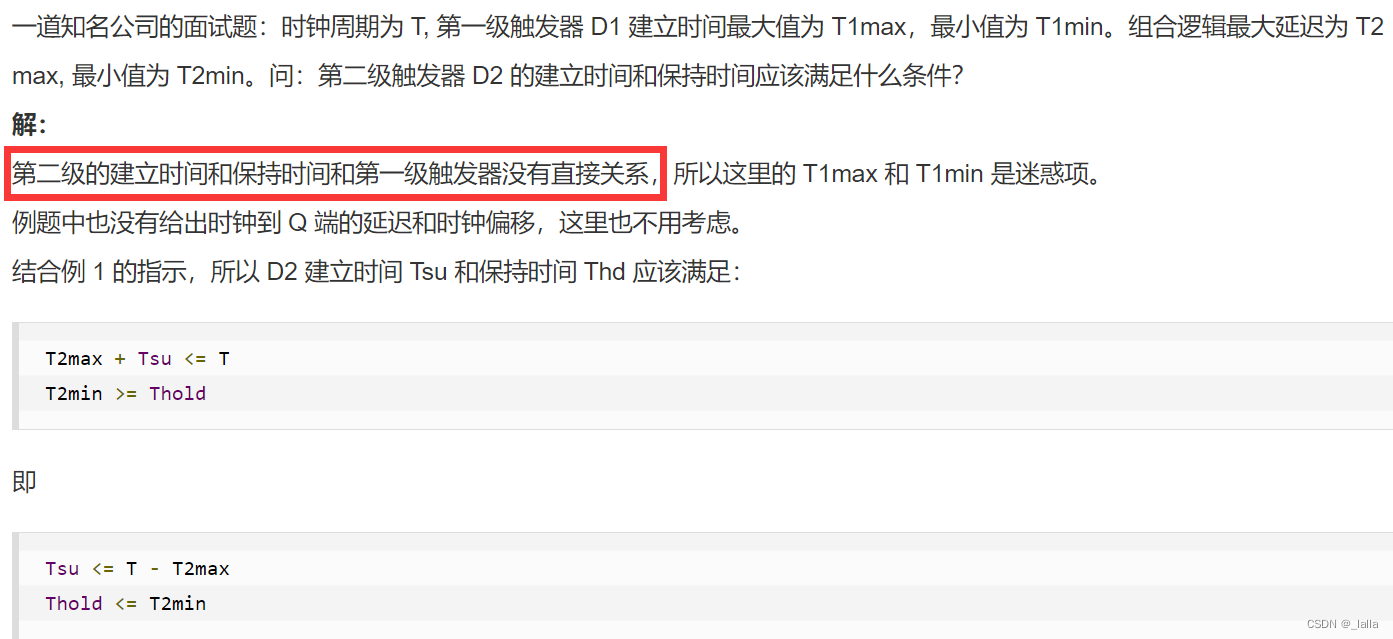

例2:

只有一个时钟存在,所以没有时钟偏移,Clock出来的是一个反相器延迟

这里的逻辑延迟要理解为时钟端到 Q 端的延迟,一定要注意不是电路中的组合逻辑延迟。

因为触发器 Q 端和 D 端连接,可以理解为两个触发器直接进行传输,所以 data path 没有组合逻辑延迟,只有一个反相器延迟。

因为只有一个钟,所以也没有时钟偏移,clock path 的反相器延迟也是迷惑项。

所以,时序约束条件为:

Tcq + Tbuf + Tsu <= Tclk

1 / (6+1+3) = 100MHz

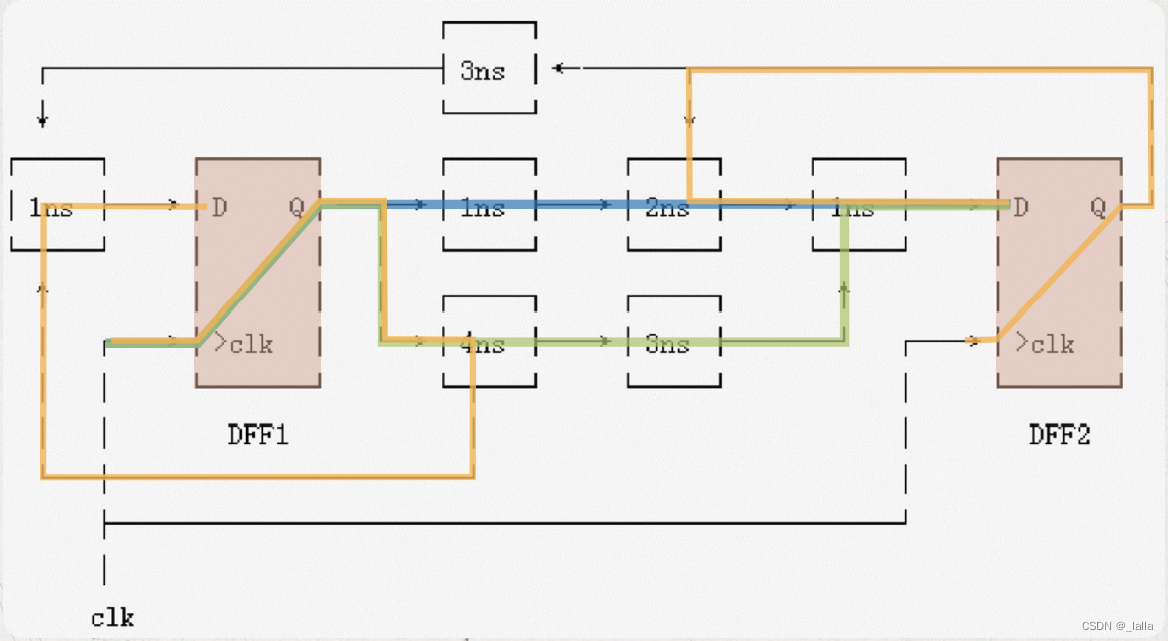

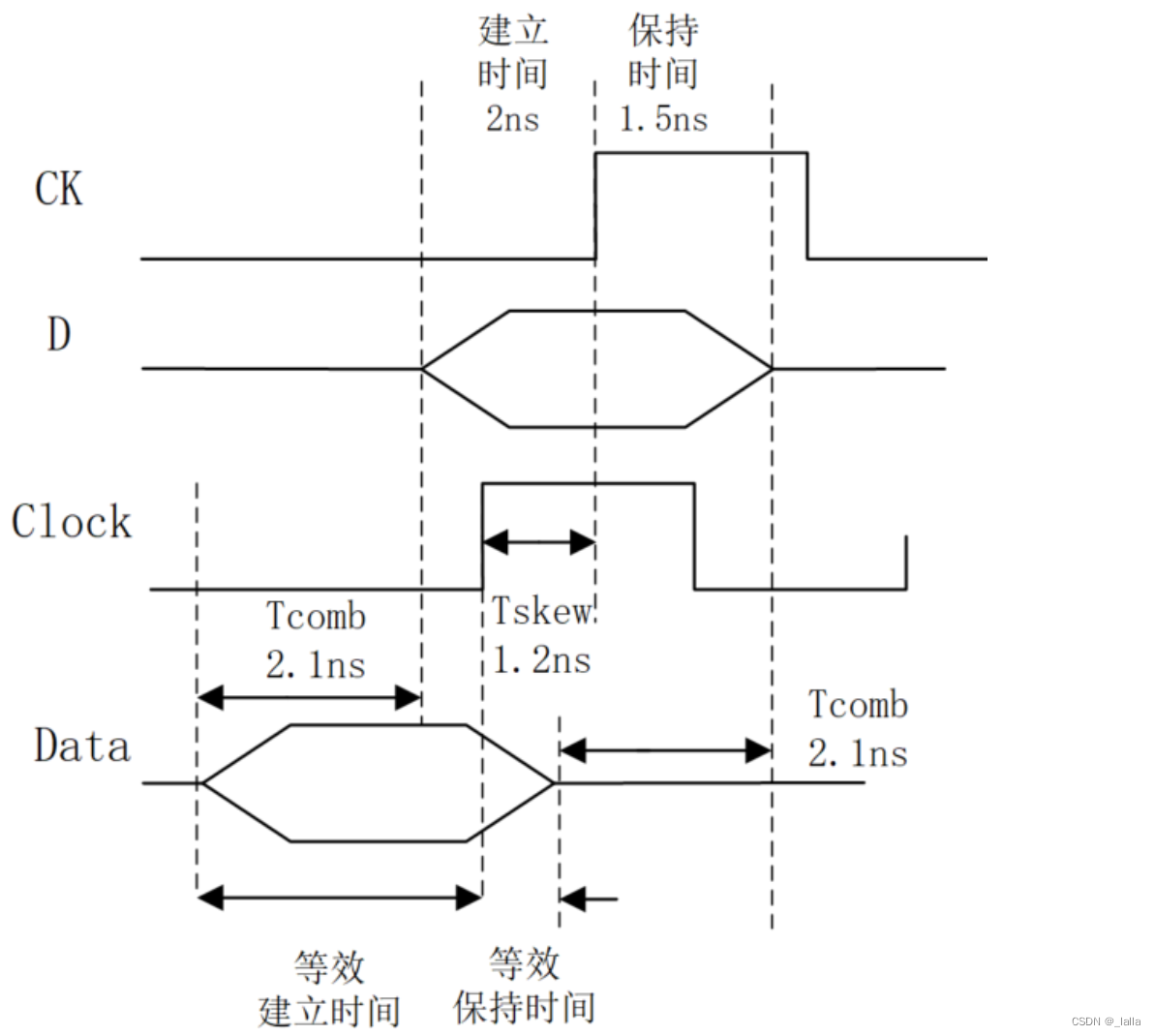

例3:

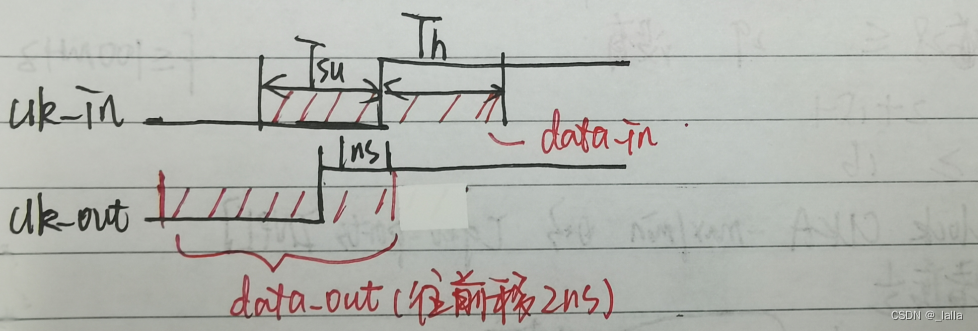

电路固有的建立时间和保持时间

求电路固有的建立时间和保持时间,其实就是求取时间裕量的过程。

该电路数据路径和时钟路径上均有延迟,为达到与触发器相同建立时间和保持时间的条件约束,则触发器 D 端和时钟端 CK,以及等效的数据端 Data 和时钟端 Clock 时序图如下:

(1) 由图可知:

该电路固有的建立时间为:2.1 + 2 - 1.2 = 2.9ns

固有的保持时间为:1.2 + 1.5 - 2.1 = 0.6ns

由此可知,数据路径的延迟会增加电路固有的建立时间,但是会减少电路固有的保持时间。而时钟偏移会减少电路固有的建立时间,增加电路固有的保持时间。

(2) 此电路仍然是自身到自身的反馈电路。所以没有时钟偏移,也无需考虑 T1= 0.9ns 的延迟。所以最高工作频率为: 1 / (1.8 + 1.2 + 2)ns = 200MHz

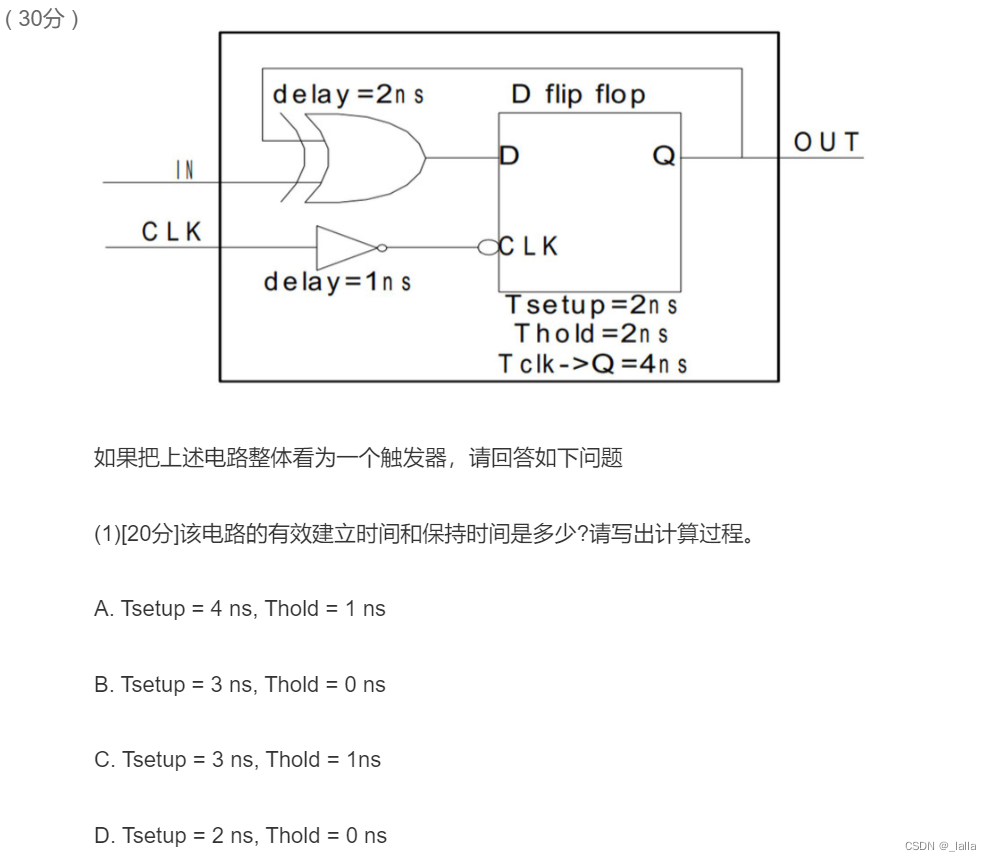

例4:

画出时序图,再进行判断

由于整个电路只有一个时钟,所以不存在时钟偏移,clk路径上的反相器是迷惑选项。

Tcq + Tcomb + Tsu <= T,4+2+2<=T,所以最高时钟频率伪125MHz

由于时钟周期和保持时间无关,所以排除法直接选择C

例5:

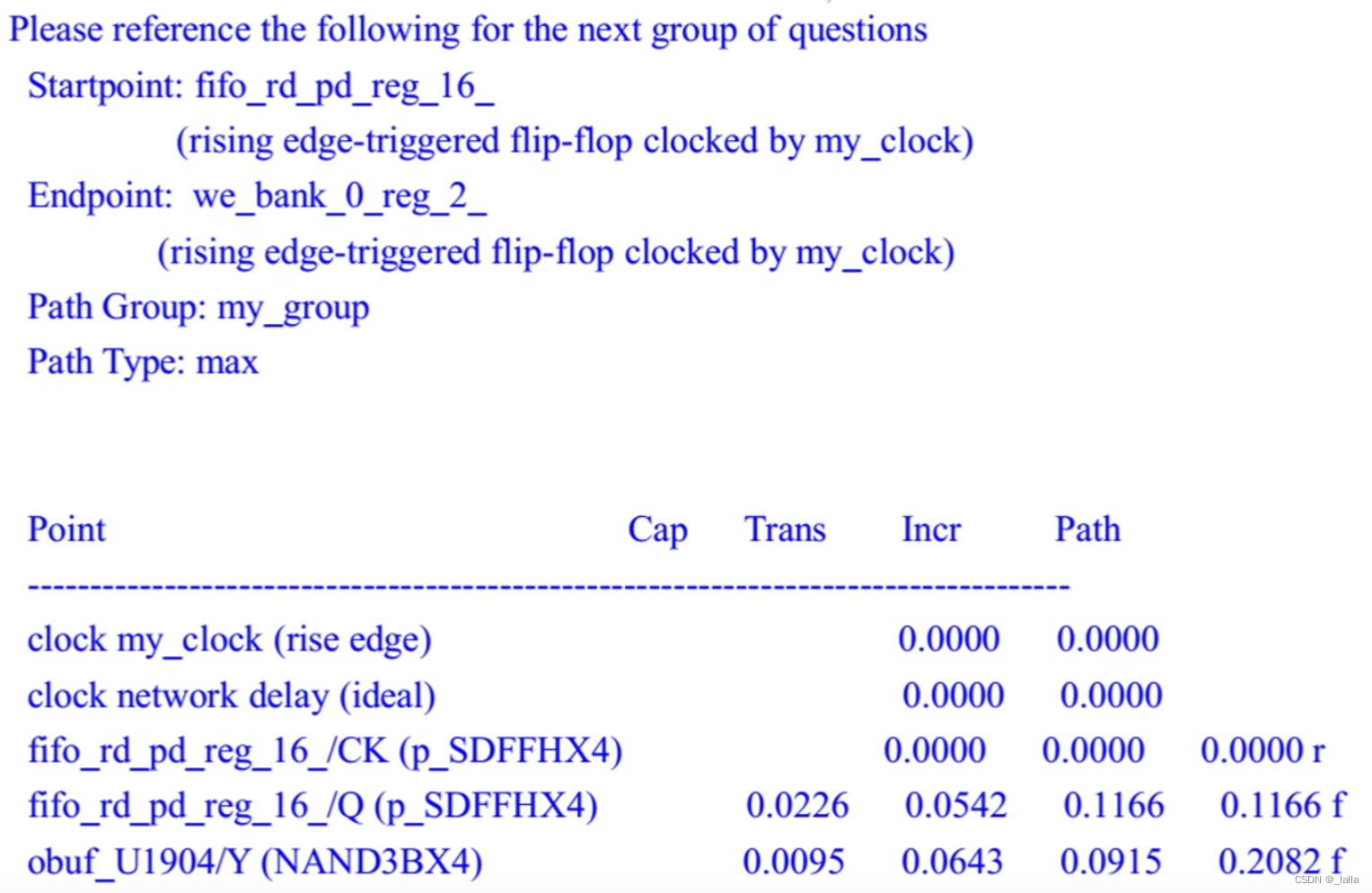

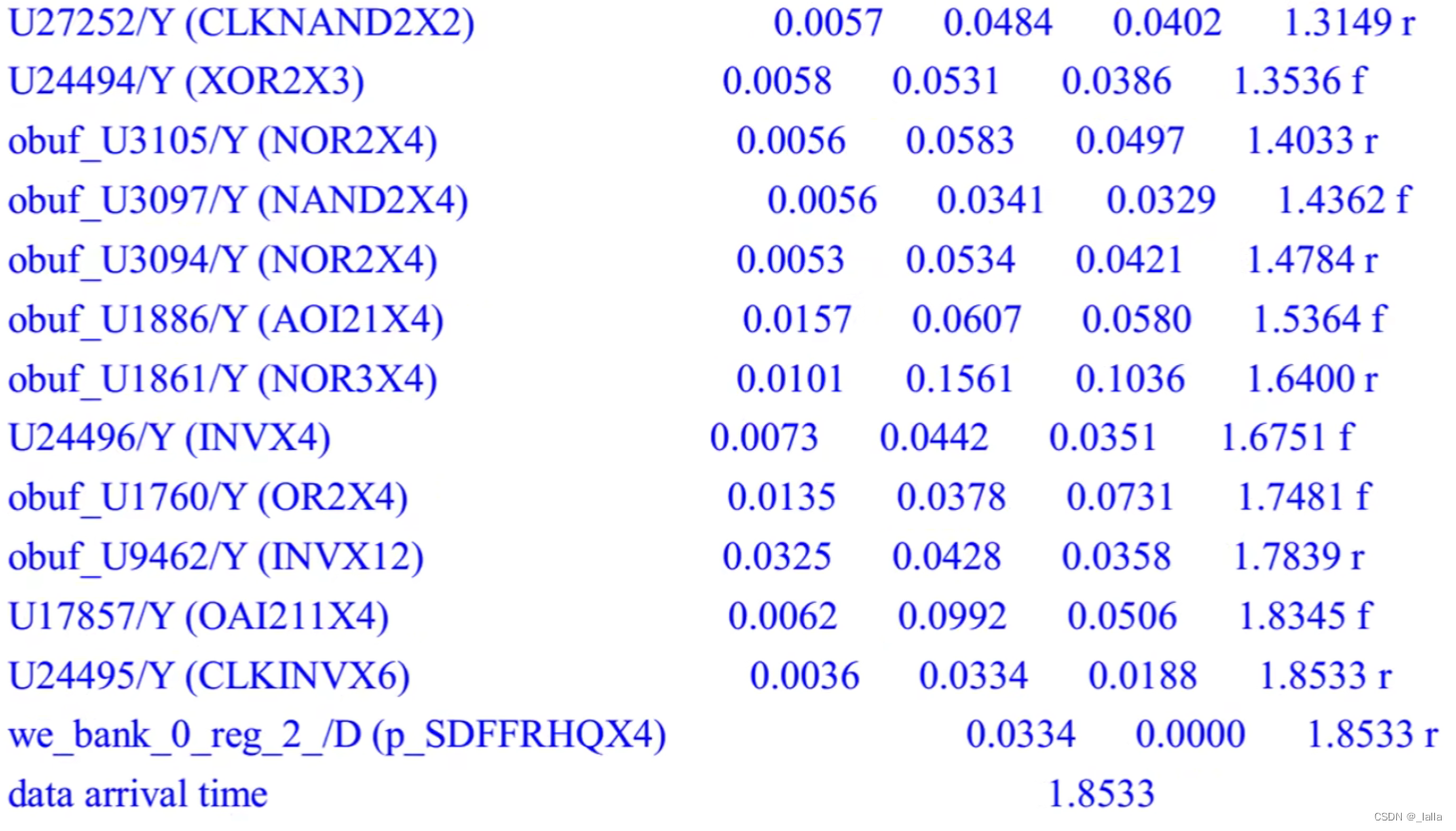

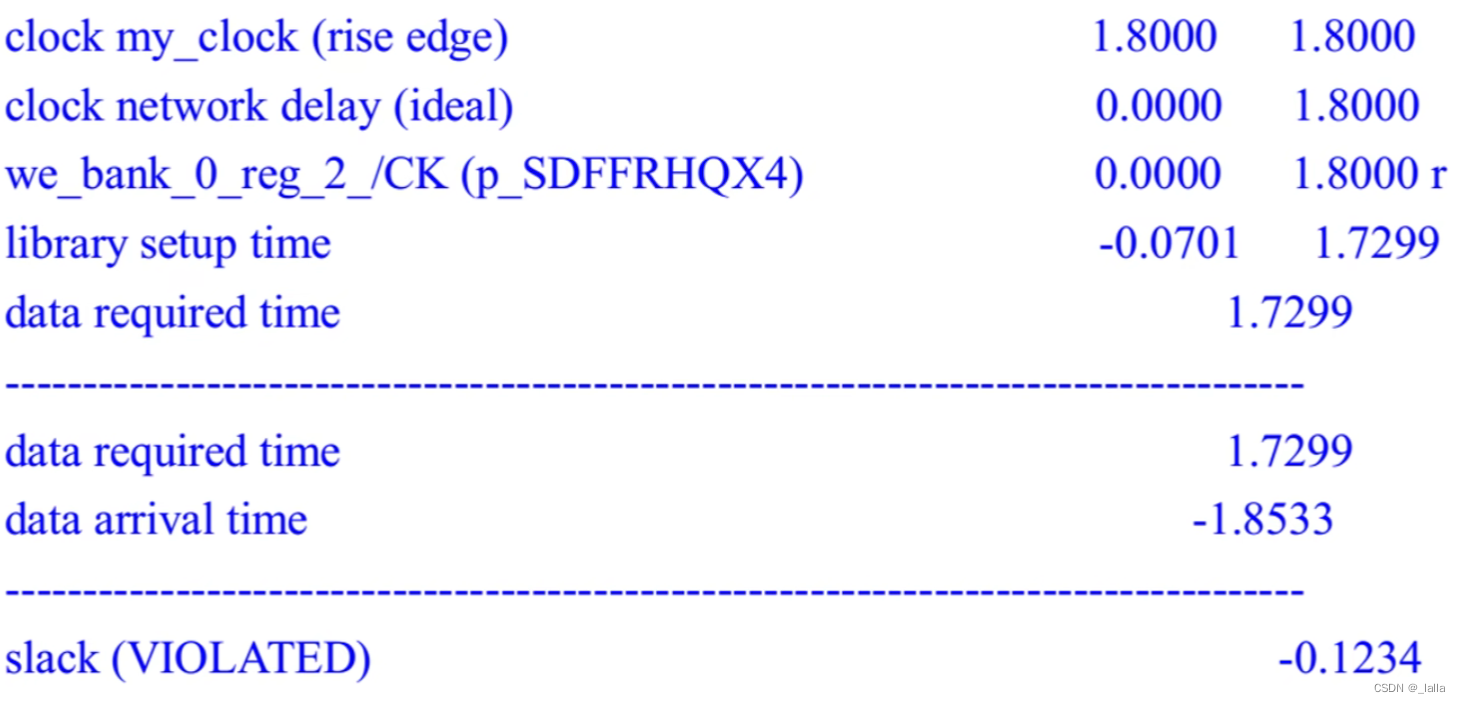

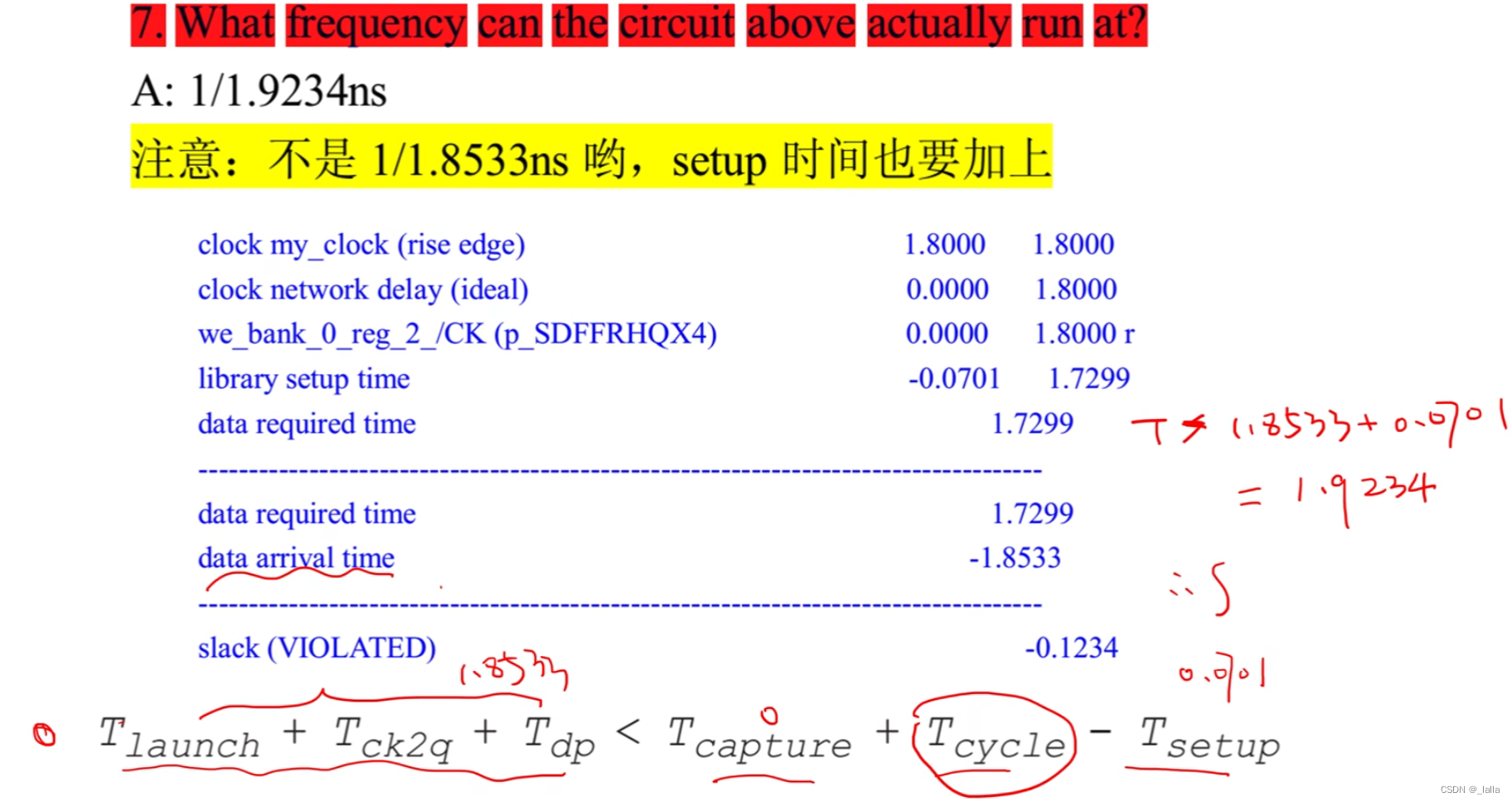

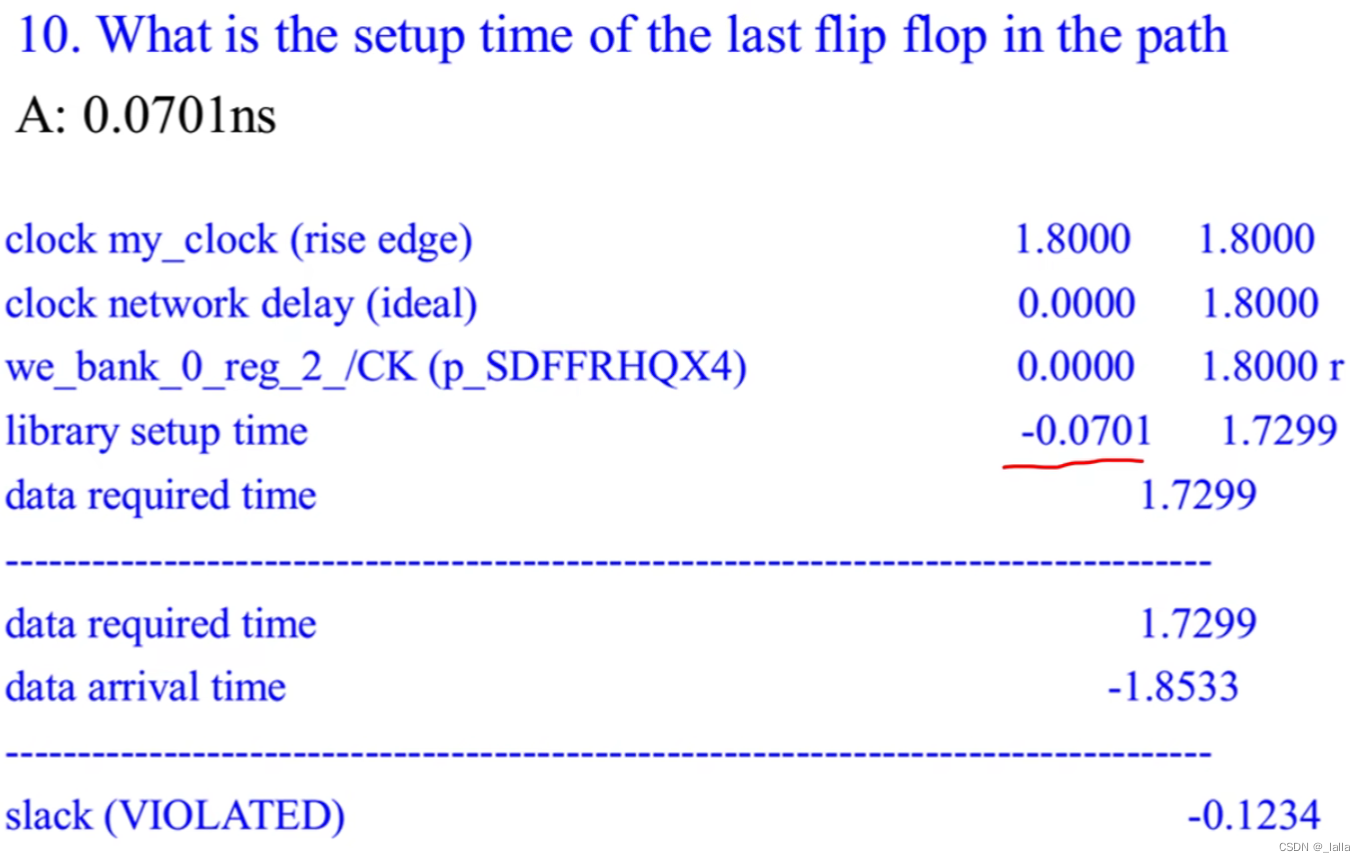

lt is PT/DC timing report. It shows there is a —0.1234ns reg2reg setup violation.

The report comes from Synopsys PT and DC.Encounter and other tools with STA functioncan create the similar report, but with different format.

Clock name is “my_clock” and frequency is 1/1.8ns

hold time无法从该报告中读出

建立时间检查是在最差的情况下检查(高温、低压、慢速)

它的时钟网络是没有延时的,理想情况,对流片没有帮助

621

621

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?