FPGA时序分析中的建立时间与保持时间

概述

总体从时序分析的概念,时序分析模型来分析建立时间与保持时间裕量,通过建立保持时间公式定性分析。

1、时序分析概念

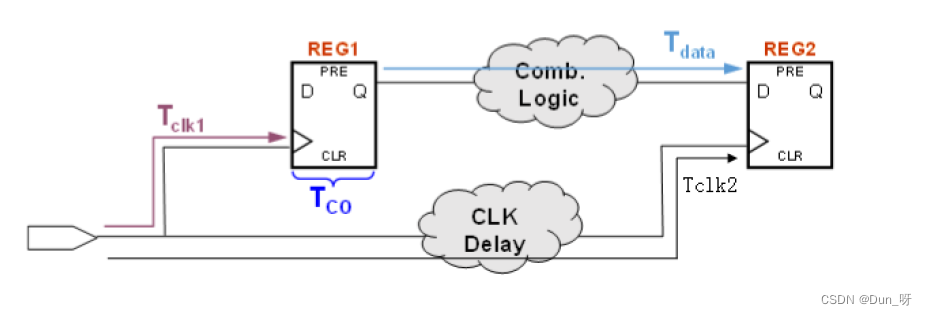

通过分析FPGA设计中各个寄存器之间的数据延时和时钟传输路径的时钟延时的关系,来确保所有寄存器都能正确的寄存数据。

2、时序分析

a、寄存器延时Tco:时钟上升沿到达D触发器 到 数据输出Q端的延迟;

b、组合逻辑延时Tdata:组合逻辑进行运算时产生的延时,一般为最长路径延时;

c、时钟延时Tclk_delay:从时钟IO口(时钟源),到寄存器的时钟端口延时;

e、时钟偏移Tskew (clock skew):指时钟信号到达数字电路各部分所用时间的差异;

f、建立时间Tsu:触发器的时钟上升沿来之前,输入端的数据必须保持不变的最小时间;

g、保持时间Th:触发器的时钟上升沿来之后,输入端的数据必须保持不变的最小时间;

如果数据在建立保持时间内发生跳变,系统就会产生亚稳态输出,即输出值在短时间内不确定(1/0/什么也不是)。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

8555

8555

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?