写在前面, DFT compiler 和Tessent 都有自己独立的DRC的检查, 可能在命名上有所重复,注意区别.

Flat model的创建(不是fault model哦)

这里的flat的意思 是 将设计中模块的界限打破,电路全部看成最基本的门电路组成;

ATPG工具会使用verilog模型区创建自己的工具内部的设计模型;设计中的cell会转换成ATPG library中的标准单元;

#使用

analyze_control_signals

create_flat_model

check_design_rules

#的时候都会创建flat model;

ATPG : Learning Analysis

在model被flattened之后,工具对设计会进行分析,获得更有利于 fault simulation和ATPG的行为;

执行gate-by-gate的仿真;会分析出设计中的一些特殊的电路结构:

例如:

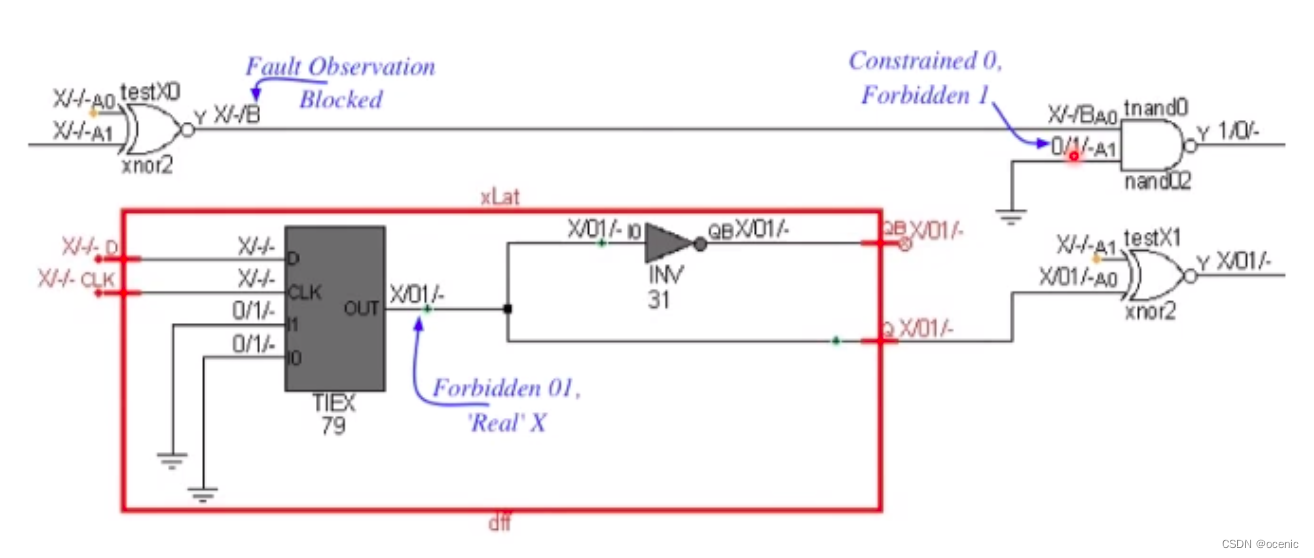

电路的等价关系;

判断是否存在

逻辑行为;

(判断设计中是否存在可以简化仿真的结构,比如 设计的结构act like a buffer,inverter,AND,OR)

潜在关系;

(判断是否存在 两个点 AB 存在逻辑值的等价关系)

forbidden的关系

(判断是否存在两点 AB A点为1的时候 B点肯定不为1)

常见的DRC 的错误

ATPG中的DRC

DRC确保设计能够按期望运行,去发现那些可能会影响测试和fault simulation的问题;包括:

1. general rule checking

2. procedure rules checking

3. bus mutual exclusivity analysis(bus相互排斥分析)

4. scan chain tracing

5. shadow latch identification

6. data rule checking

7. transparent latch identification

8. clock rule checking

9. RAM rule checking

10. bus keeper analysis

11. extra rule checking

12. scanability rules checking

13. constrained/forbidden/block value calculation

clock rule

任何能够引起时序部件状态发生转变的私有输入,都会当成clock;包括 set reset的输入;

时钟的两个沿: LE leading edge(off->on); TE trailing edge(on->off)

引入一个概念: clock cone 是指与clock 相连的锥形逻辑范围,间接受时钟影响的逻辑为:effect cone; 既和时钟直接相连 又属于时钟间接影响的逻辑区域叫 both cone;

两种方式去展示时钟的信息:

- 使用 tessent visualizer 展示clock cone

- set_gate_report -clock_cone pin_name

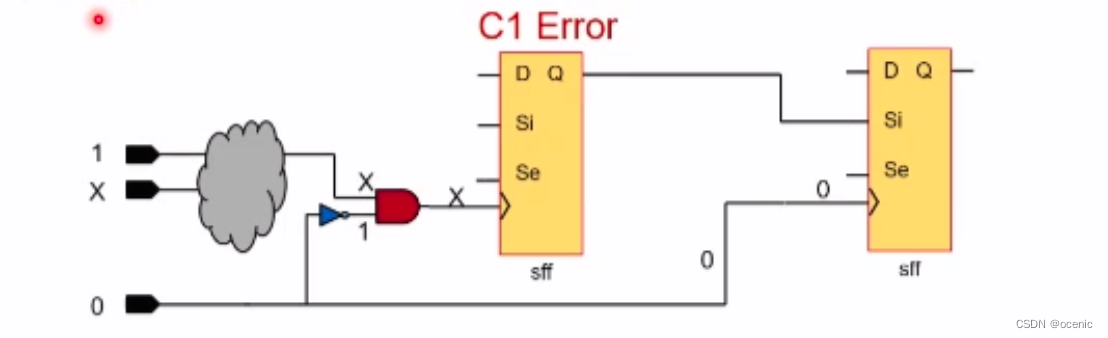

C1 (C1 clock类型的DRC违例)

RULE : Clock PIs off failed to off a clock line of MASTER/SLAVE ANDOR1(gate ID).(C1-1)

当所有指定的时钟都被设置为off 态 时,scan cell 不可以capture data; 在指定cell的时钟的关闭状态cell仍能接收数据

当所有定义的时钟处在off state, 约束的pin 设置成了所约束的值;

初始化之后的non-scan cell 被设置成他们的稳定值;

定义的cell constraint 被应用(包括 C0C0DX C1 C1DX等)后 就会检查simulation value 去确定有没有 C1的error;

发生的原因:clock的off state定义有错,或者 primary input没有初始化为一个已知的值.

#如何debug C1的错误

analyze_drc_violation c1-1

#追踪时钟 到他的PI

#验证时钟的定义是否正确

report_clock -all

#验证pin 的约束是不是按需要设置了

report_input_constraints <pin_name>

#如果时钟的off state 定义错误了

#可以使用

delete_clock <clock_name>

add_clocks <off_state> <name>

#如果off state是正确的的

#问题很有可能出现在 相关的PI没有被初始化为一个已知的值;

#通过增加PIN的约束来修改

add_input_constraints EN -C0

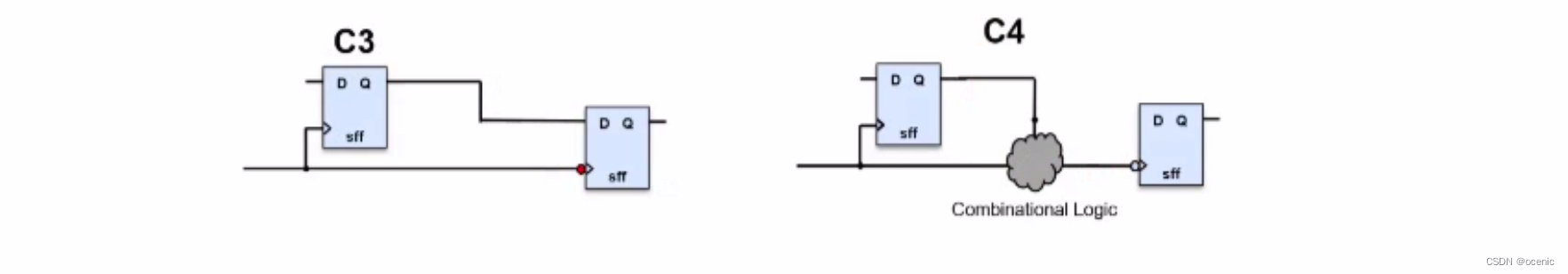

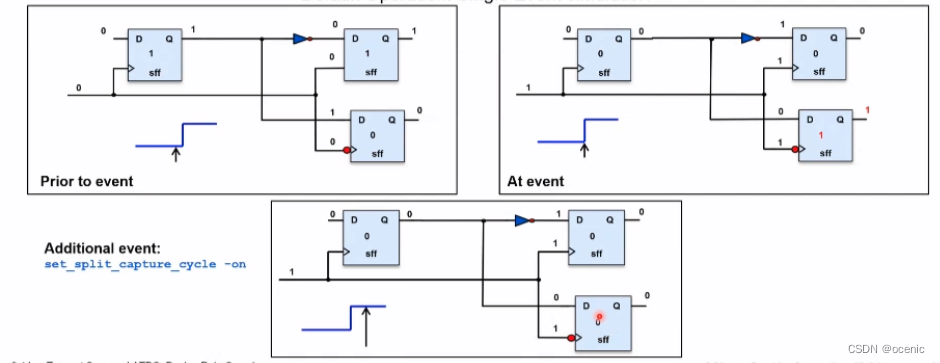

C3 /C4

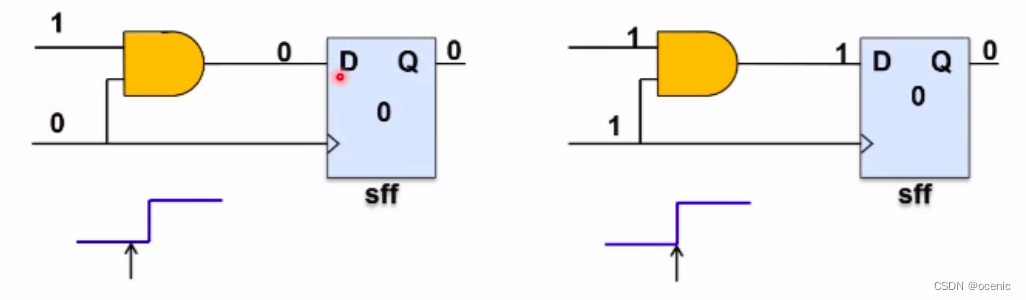

Rules: scan chains 上同时存在 LE TE 的scan cell 存在simulate capture 错误的可能性,以及生成的simulation的mismatch;(仿真的值和期望的值不一样);

工具会假设在 LE的时候 所有的scan cell 都会 capture到正确的值;对于TE 的scan cell 由于他也是在LE 的时候去取值,这会造成 实际的功能和预测的功能之间的mismatch;

如图 类似 C3 TE 的scan cell 是可以在一个周期内的负沿上踩到的; 所以这种类型的DRC属于 warning;

工具可以自动 fix 这种问题.

#解决办法

set_split_capture_cycle -on

如上图所示,存在两个异沿的寄存器,在未set_split_capture_cycle -on之前,都是在上升沿更新寄存器,而他本来是需要capture 上一个寄存器更新之后的值.所以当option on之后,会在clock 的on state进行capture 而不是leading edge;

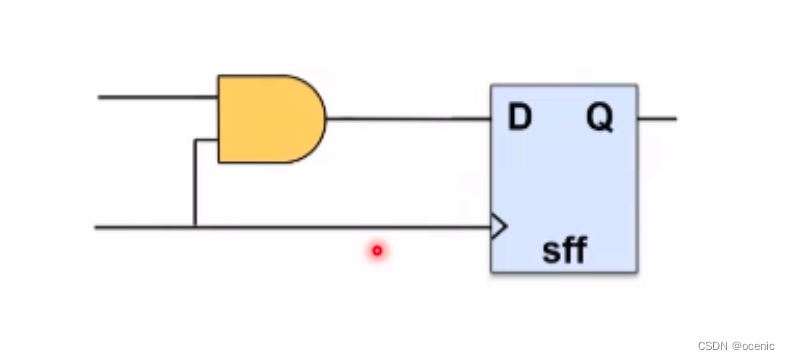

C6

rule: 时钟一定不能影响正在 capture的值, 如果影响到了,一般情况下 都会导致不正确的simulate results;也就是数据的竞争冒险的情况

如上图所示, data来自于clock,对于寄存器来说,data和 clock哪个先到,最后踩到的值也会不一样.

工具会检查 scancell的 data和clock 端是否受同一个clock的影响;

等级为 warning;

massage如下:

clock P failed rule C6 on input I of N(G) (c6-1)

P 为时钟的引脚

I 为时钟的gate input number

N 为门的实例代号

G 是门的ID

如何解决C6的违例?工具会自己进行处理.

set_clock_off_simulation on

这个选项会给那些受C6违例影响的cell 在默认的LE event之前强制赋值(提前去做capture)

这里就有点问题了, 寄存器的行为我们是没办法控制的呀,除非这是在仿真阶段, 有工具将寄存器赋值;

C3/C4/C6的违例

实际上都是在create_patterns的时候解决的,通过调整pattern capture的位置,来解决对应的问题.

D1 data disturbed (数据的错位 扰乱)

描述:load 的数据或者 capture 到scan chain中的数据 可能被扰乱(存在cycle的错位,这就是很严重的错误了);

仿真的mismatch 仅仅是在串行的testbench中才会被detect到,那些并行的 testbench 只有在使用非独立的shift的时才有可能发生;

set_drc_handling D1 warning

#使用上述选项,将error标记为warning;

#改成 warning之后 就不报错了,但是如果发生D1 violation的数量太多 会影响到最后的 test coverage;需要去逐个的解决发生failure的source;

massage:

N(G) disturbed during time Tof P procedure (D1-1)

T 是哪个周期

P procedure;

例: 在load_unload的第一个cycle是给scan_enable信号一个足够的transition时间,做initial用的,如果在procedure中第一个cycle就开始pulse clock那么就有可能发生D1的违例.

D5

当电路中 存在没有识别为scan chain 的存储单元,就会报告D5的 DRC violation;

会基于 setup load_unload shift的仿真结果设置一个初始值;

那些 nonscan cell会被看做 TieX/0/1 Init-X/0/1 , Tie 单元会影响到 test coverage;

#使用

report_drc_rules D5 -type T0

[-NOType I0] ...

D6 非扫描单元的latch;

错误等级: warning

描述:所有的nonscan 的latch 都要表现为 transparent latch(transparent latch 是指能够传播值 但不能hold值)

如果一个latch 创建了一个潜在的回路,那么这条路径必须被scan cell 或者除了transparent latch 之外的scancell 打破;

latch 不许有能够传播到可观测点的路径;

latch 在所有定义时钟在off state时 也能够capture到 经过的值;

#设置 忽略D6的错误

set_drc_handling D6 ignore;

#工具会将 D6的单元 当做 Tie -X 对待,会影响到测试覆盖率

E4 contention check(竞争检查)在load unload cycle

没太理解这里,

检查在 testprocedure的赋值的时候有没有两个冲突的值驱动同一条net;

E4就是在 load_unload 的时候去查看是否有一个 X值到达 bus gate;

(bus gate 是啥啊??)

经常怎么解决呢? 就是在test_setup和 laod_unload 的时候 去force statement;

解决办法,经常就是对 bidi pins 在load_unload 的procedure中做 force Z;

错误等级: warning;

BIDI 的端口是双向端口?? 对于双向端口来说,在ATPG的时候会固定地把它看做输出端口或者输入端口.

E5 X态会被传播到 其他观测点

错误等级: Note,但会影响到你的coverage;

描述: 当应用引脚的约束被应用以及PIs将它强制赋值的时候, X态不能传播到任何一个观测点上.

T3 扫描链回溯

描述: shift procedure必须能 创建一条从扫描链的输出到输入的畅通的路径.不正确被激活的门会导致错误.

检查T3的DRC的时候会对 laod_unlaod和shift 的procedure进行仿真,然后回溯扫描链.

经常造成T3违例的原因是设计在测试的时候不是在一个稳定的状态.可能是由于 non_scan blocks没有被正确的初始化,或者在测试时不能维持一个稳定的状态.

错误等级: Error;

T4 T5

T4描述: 在shift procedure的一些时序周期内,扫描连上的存储单元必须有活跃的时钟存在

T5描述:在扫描链上的存储单元不能存在X值输入的时钟,set/reset的输入.

错误等级: Error;

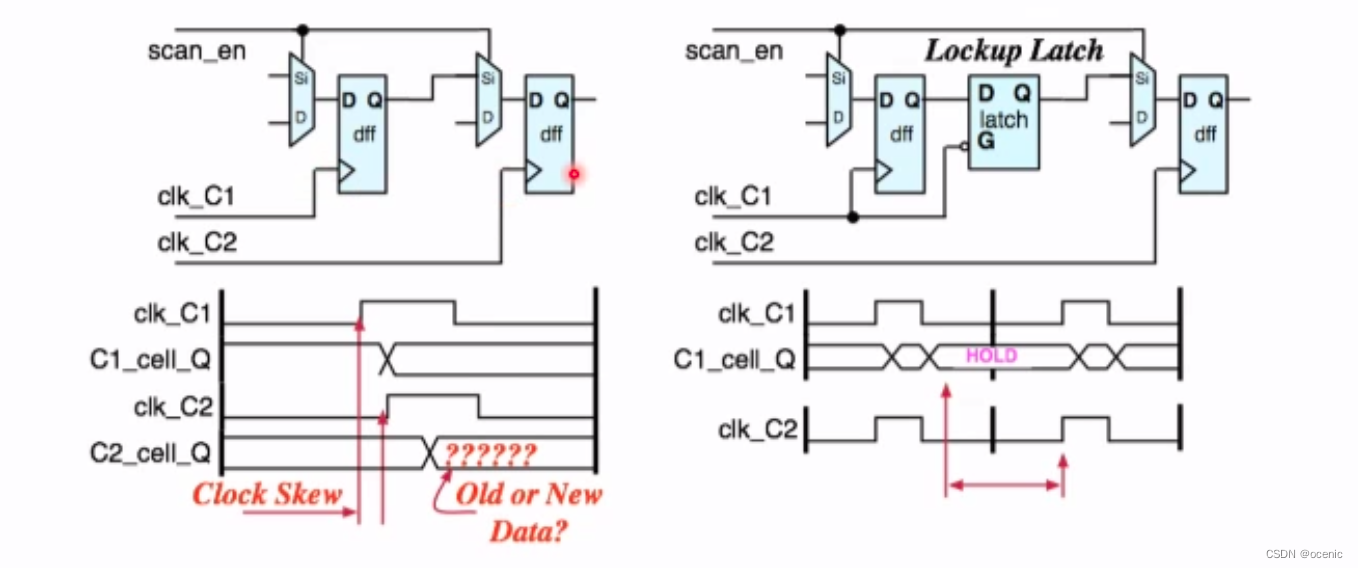

Trace 24 (T24) Rule

描述: 当一条扫描链使用两个clock domain的时候,需要添加lockup cell去处理 跨时钟域的clock skew的问题. lockup cell用来保护从源寄存器到目的寄存器的旧数据. lockup cell 一般就是latch;

T24 就是 这种latch miss掉了

错误等级:error;

如何 debug DRC

#使用

report_drc_rules

#去查看drc的违例,包括fail的次数,工具的处理;

#使用

check_design_rules

#将所有的drc违例 list出来

### 使用可视化的方法 去debug;

#使用

analyze_drc_violation #去展示 DRC在 schematic中的位置

#如果 analyze 对于指定的DRC不可用,

#使用:

open_visualizer

add_shematic_objects object_spec -display flat_schematic;

# 改变 change the gate report data as nessessary

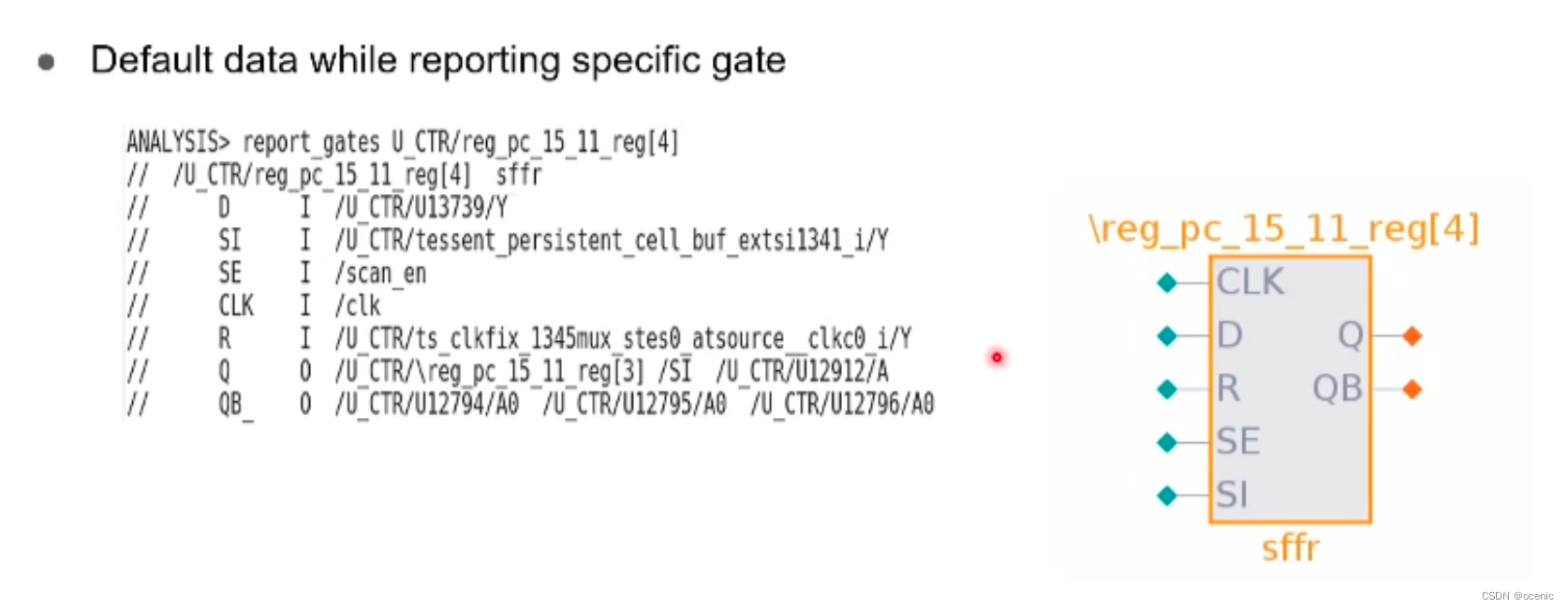

gate report

通过 set_gate_report

设置报告的选项,默认的gate_report的内容如下

通过set_gate_report 可以配置report的内容.

添加constrains value的信息

set_gate_report constrain_value

会报告gate 引脚上的约束值;包括:

CV/FV/B

分别是 constrained value forbidden value 和是否被blocked;

constrained values 是在通过 DRC check的

ANALYSIS mode 下才可用,

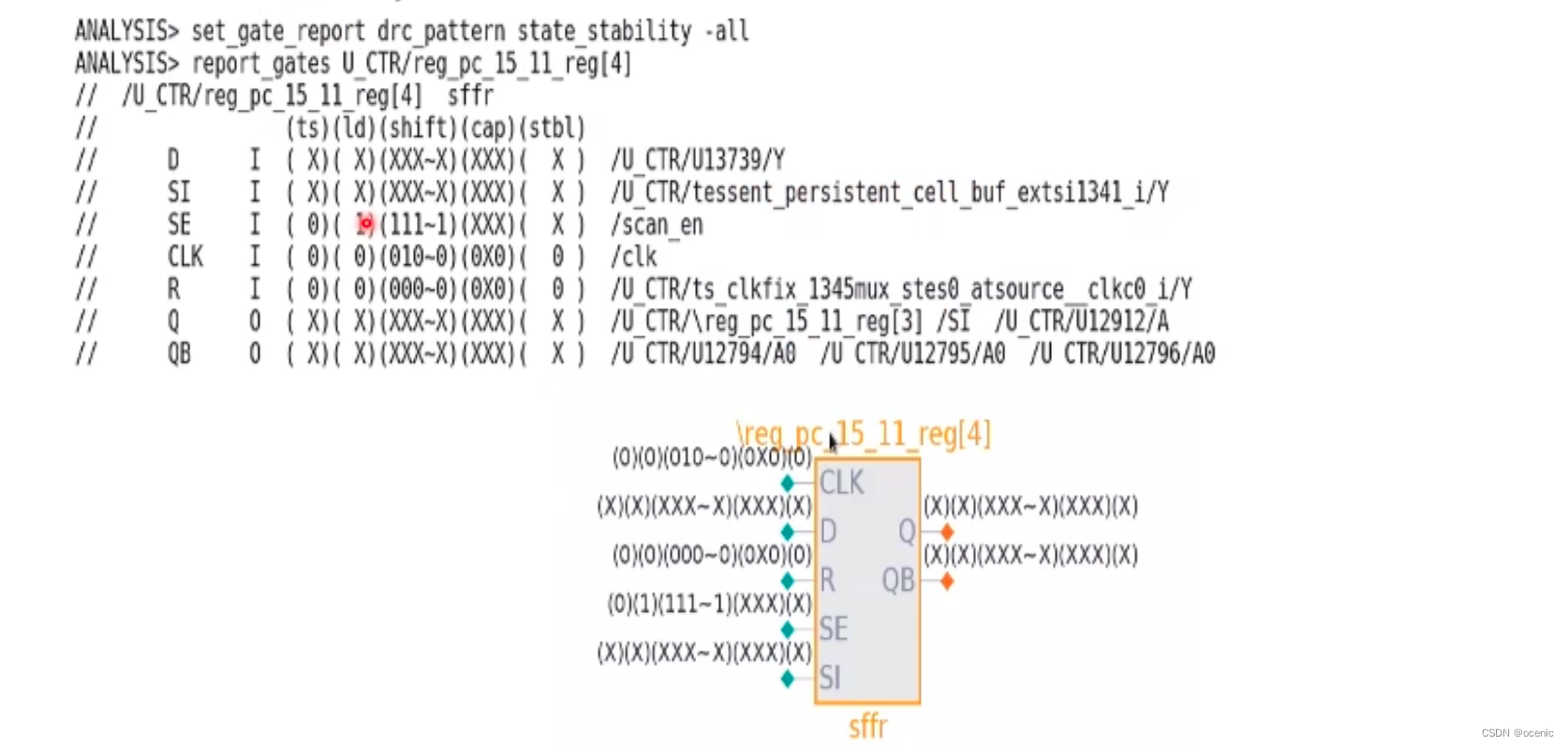

添加state stability的信息;

会增加一列信息:展示的是存储单元每一个procedure结束时的稳定值

(ts)(ld)(shift)(cap)(stbl)

会把每个event cycle中的门的引脚的上的值报告出来;

ts (test setup): 展示的是 test_setup procedure的最后的值;

ld(load cycles): 展示load_unload 时候 第一个procedure的稳定值;

shift(010~0):展示shift第一个cycle对应clock pulse的前中后三个阶段.最后一个值为shift结束之后的稳定状态.

cap(capture cycel): 应该也是对应clockpulse的前中后是哪个阶段.

984

984

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?