上一篇文章简单说了一下对眼图的理解,下面继续整理关于眼图的那些事。这个是上一篇文章的链接: 信号完整性之眼图(eye)理解(一).

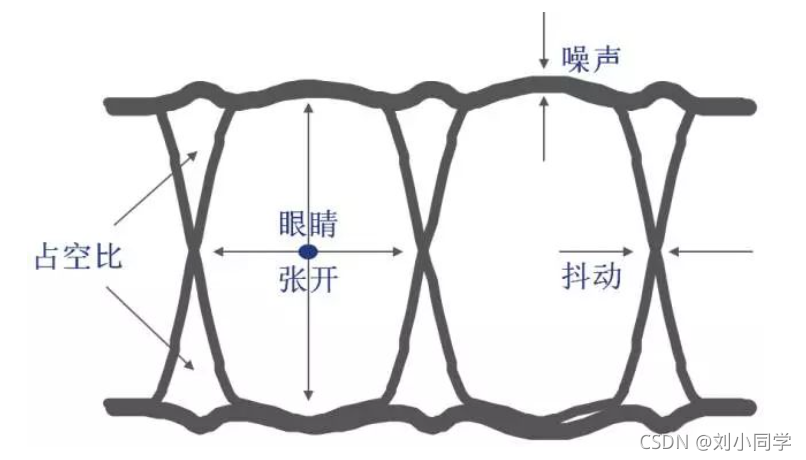

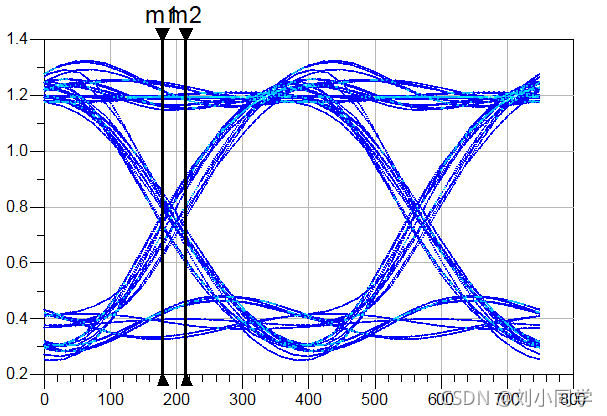

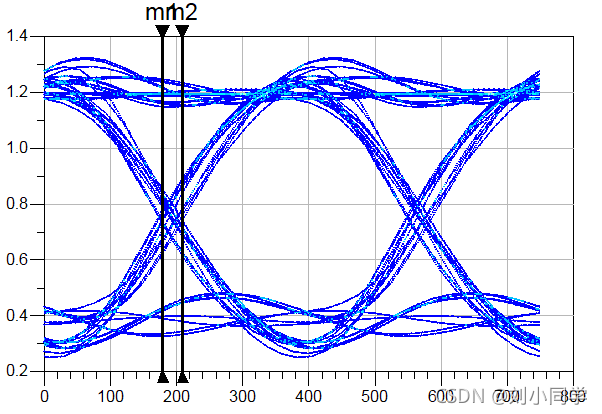

1.眼形窗定义

可以改变眼形窗起始和眼形窗终止的百分数:眼形窗起始控制设置眼图测量的水平起始点,眼形窗终止控制设置眼图测量的水平终止点。这些控制会影响眼图高度、眼宽宽度和品质因数测量。默认的眼图窗起始值是40%,终止值是60%。

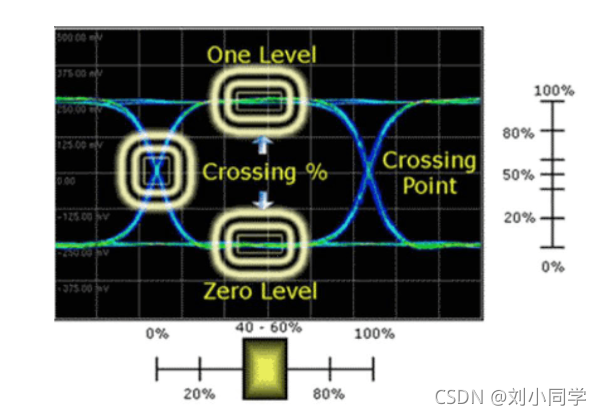

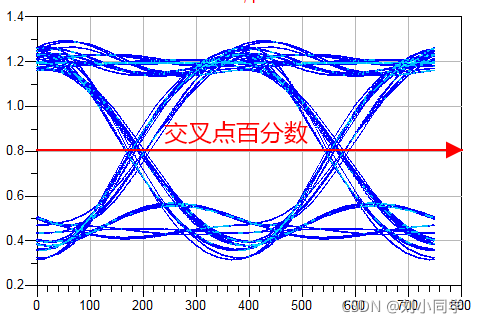

2.交叉点百分数的定义

眼图是高速信号依据时间对累加1及0振幅的相对关系。由两个位所组成的眼图信号,其中中间的一个位是眼晴张开得以让信号顺利通过的关键。交叉点百分数是眼图上升沿与下降沿的交叉点与Vtop和Vbase的差的比值。由于眼图交叉百分比,是测量交叉点振幅与信号1及0位准之关系,因此不同交叉比例关系可传递不同信号位准。举例来说,一般标准的信号其交叉百分比为50%,即代表信号1及0各占一半的位准。这个概念可能不是很好理解,所以在网上找了一张图片很好的表达了这个定义,大家可以看一下:

3.占空比失真的定义

占空比失真为在中间域值处的眼图的下降沿和上升沿之间的时间量度。占空比有两种表现形式:时间和百分数,1)计算在中间阈值处的下降沿中点和上升沿中点的实际时间差,2)以百分数格式表示时,以占整个位宽的百分数来计算时间差。

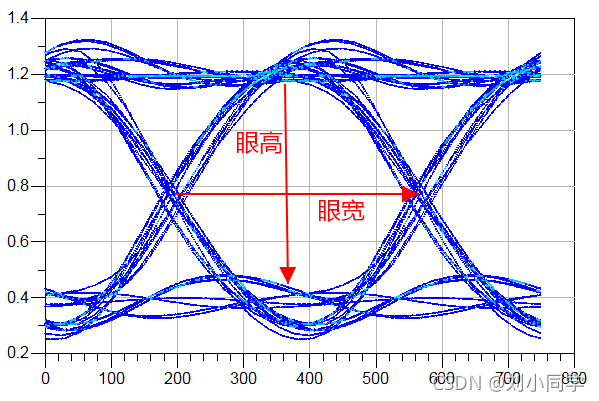

4.眼高和眼宽的定义

眼图高度即眼高,是测量眼图的垂直开口的高度。眼图宽度即眼宽,是测量眼图的水平开口的大小。

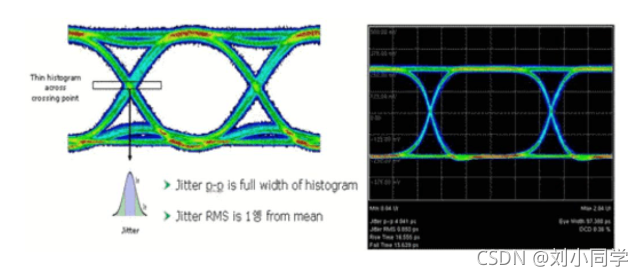

5.眼图抖动的定义

眼图抖动测量交叉点的时间位置的变化。抖动,描述了信号的水平波动,即信号的某特定时刻相对于其理想时间位置上的短期偏离。

抖动质量是高速信号最常验证的项目,也是重要的测量参数之一,可有效验证相对理想时间下的飘移情形。在计算抖动时,常以眼图交叉点上升及下降边缘的信号对时间统计之分析方式作测量依据。如图下图所示,在所选取的区块中进行抖动点对点(Jitter p-p)及抖动均方根值(Jitter RMS)之验证;其中Jitter p-p是以所取选取区块之统计宽度作为计算,而Jitter RMS是以平均分布标准差1奈秒作计算;而对应的真实抖动眼图如右方所示。

6.眼图品质因数的定义

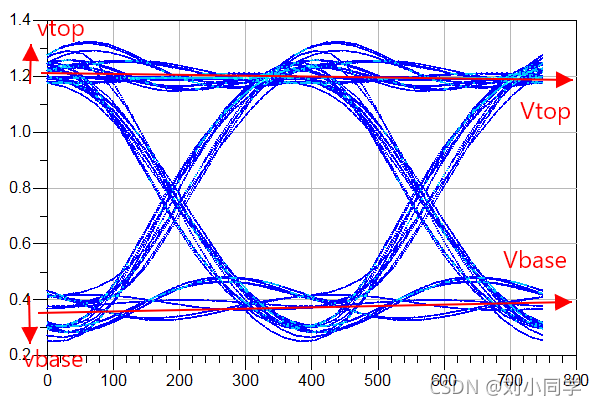

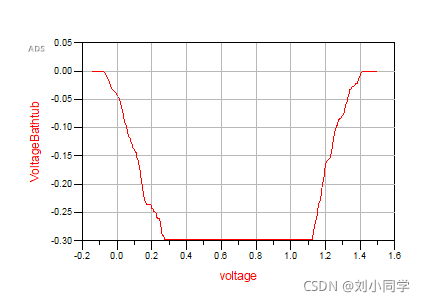

眼图的品质因数,它等于垂直眼图张开度与高电压电平和低电压电平处的噪声和之比。

品质因数=(Vtop-Vbase)/(vtop-vbase)

Vtop:为垂直直方图波顶峰值的平均电压,Vbase:为垂直直方图波低峰值的平均电压

vtop:为垂直直方图波顶峰值的标准偏差,vbase:为垂直直方图波低峰值的标准偏差

7.眼图中上升时间和下降时间的定义

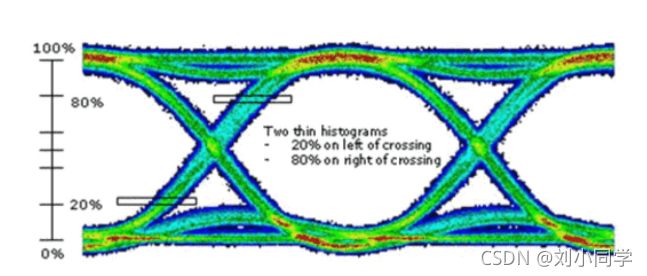

一般测量上升及下降时间,是以眼图占20~80%的部分为主,其中上升时间如下图,分别以左侧交叉点左侧(20%)至右侧(80%)两块水平区间作此传递讯息上升斜率时间之换算。计算公式如下: 上升时间=平均(80%时间位准)-平均(20%时间位准) 。

8.眼图中误码率的定义

误码率(SER:symbol error rate)是衡量数据在规定时间内数据传输精确性的指标,误码率=传输中的误码/所传输的总码数*100% [1] 。如果有误码就有误码率。 另外,也有将误码率定义为用来衡量误码出现的频率。进行特定条件下的误码率研究,对增强无线通信系统性能,改善数据传输质量意义重大。

码率是最常用的数据通信传输质量指标。它表示数字系统传输质量的式是“在多少位数据中出现一位差错”。举例来说,如果在一万位数据中出现一位差错,即误码率为万分之一,即10E-4 [3] 。误码率=错误码元数/传输总码元数。计算公式为:

误比特率=错误比特数/传输总比特数。

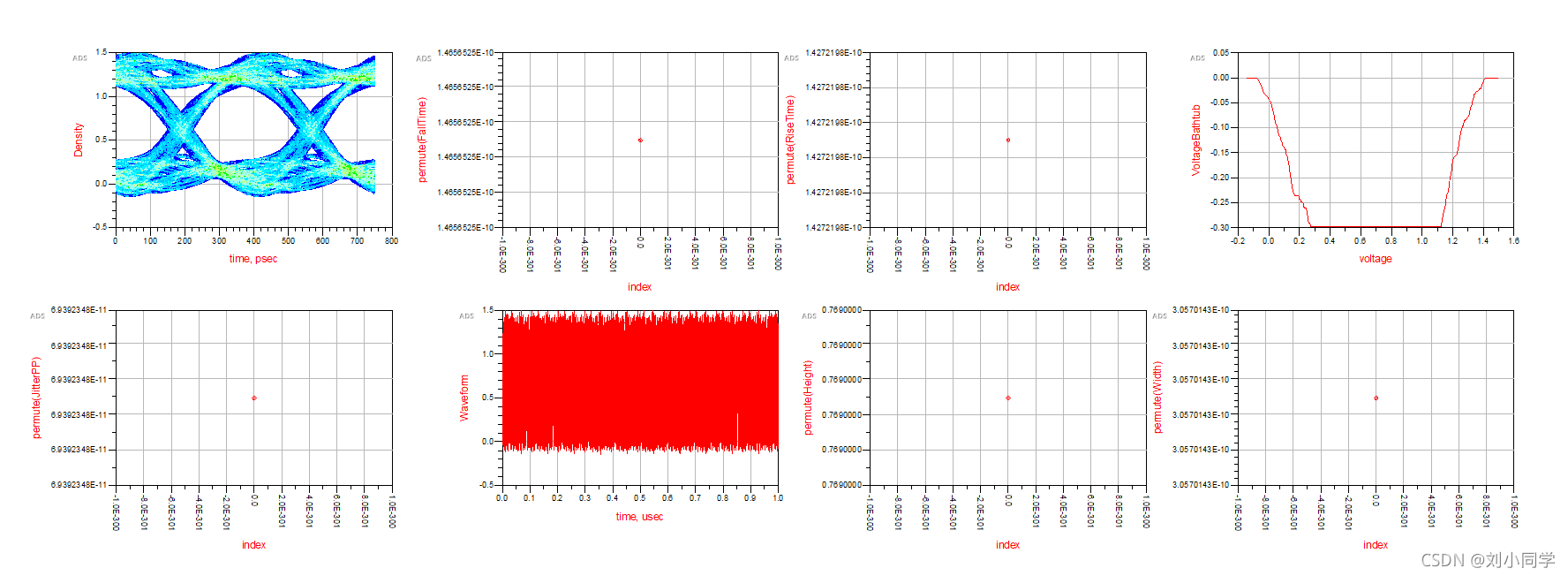

9.眼图测试结果

以上是本人对于信号完整性设计的简单整理总结,其中有些遗漏,会及时更新。

如有错误,希望各位大神留言指正,顺便点个赞👍关注,感谢!!!

下面链接是之前几篇文章总结的信号和电源问题,大家可以浏览一下:

链接: link.链接: link.链接: link.

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?