本内容学习自领航者ZYNQ 之FPGA开发指南 V1.0

1.RAM IP核简介

Xilinx 7 系列器件内部的块RAM 全部是真双端口RAM(True Dual-Port ram,TDP),这两个端口都可以独立地对块RAN 进行读/写。但其也可以被配置为伪双端口RAM(Simple Dual-Port ram,SDP)(有两个端口,但是其中一个只能读,另一个只能写)或单端口RAM(只有一个端口,读/写只能通过这一个端口来进行)。单端口RAM 只有一组数据总线、地址总线、时钟信号以及其他控制信号,而双端口RAM 具有两组数据总线、地址总线、时钟信号以及其他控制信号。

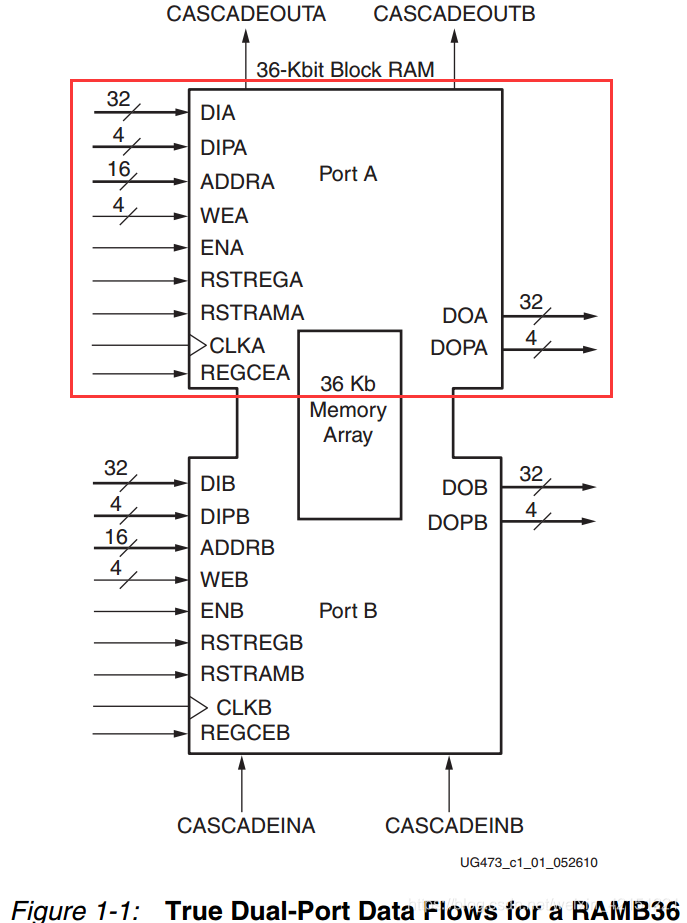

Xilinx 7 系列器件内部的真双端口块RAM 的端口框图如下图所示。

可以看到,其中包括了Port A 和Port B,我们在接下来的实验中,会例化一个单端口RAM 的IP 核,其只会用到Port A,如图中的红色方框所示。下面是Port A 中的端口描述,Port B 的端口功能和Port A 是一模一样的:

DI A:数据输入总线,用于写操作。

DO A:数据输出总线,用于读操作。

ADDR A:地址总线。

WE A:写使能信号,为高代表写操作,为低代表读操作。

EN A:端口A 的使能引脚,为高时使能端口A,若端口A 的使能引脚被禁止,则端口A 上的读/写操作都会变为无效。使能极性是可配置的,默认情况下高使能。

CLK A:端口A 的时钟信号。

2.RAM IP核的使用。

首先创建一个名为ip_ram 的工程,然后我们创建ram IP 核。在Vivado 软件的左侧“Flow Navigator”栏中单击“IP Catalog”,“IP Catalog”按钮以及单击后弹出的“IP Catalog”窗口如下图所示。

在“IP Catalog”窗口中,依次展开“Memories & Storage Elements”——“RAMs & ROMs & BRAM”,然后双击“Block Memory Generator”,如下图所示。

本文详细介绍了Vivado 18.3中如何使用RAM IP核,包括真双端口RAM的结构和单端口RAM的配置。通过创建工程并实例化Block Memory Generator,设置Port A的参数,如宽度、深度等,展示了IP核的生成和综合过程。在RTL编码阶段,解释了如何例化IP核模板以及与之交互的ram_rw模块的工作原理。

本文详细介绍了Vivado 18.3中如何使用RAM IP核,包括真双端口RAM的结构和单端口RAM的配置。通过创建工程并实例化Block Memory Generator,设置Port A的参数,如宽度、深度等,展示了IP核的生成和综合过程。在RTL编码阶段,解释了如何例化IP核模板以及与之交互的ram_rw模块的工作原理。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

7402

7402

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?