本视频学习自正点原子ZYNQ领航者FPGA视频-P9

1.Vivado Simulator仿真简介

Vivado 设计套件内部集成了仿真器Vivado Simulator,能够在设计流程的不同阶段运行设计的功能仿真和时序仿真,结果可以在Vivado IDE 集成的波形查看器中显示。Vivado 还支持与诸如ModelSim、Verilog Compiler Simulator (VCS)、Questa Advanced Simulator 等第三方仿真器的联合仿真。

功能仿真需要的文件:

1.设计HDL 源代码,也被称为UUT(Unit Under Test):可以是VHDL 语言或Verilog 语言,既可以是设计的顶层模块,也可以是设计的下层子模块。

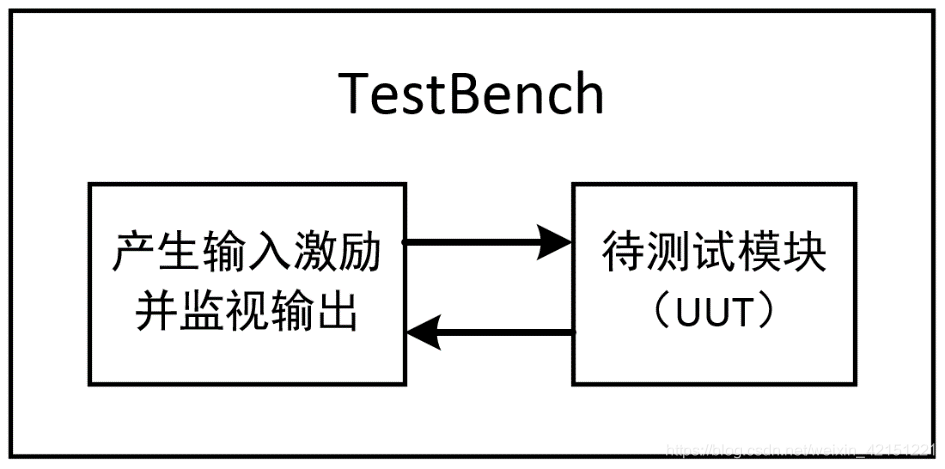

2.测试激励代码,也被称为TestBench:根据UUT 顶层输入/输出接口的设计要求,来产生顶层输入接口的测试激励并监视顶层输出接口。由于不需要进行综合,书写具有很大的灵活性。

TestBench 和UUT 之间的关系如下图所示:

3.仿真模型/库:根据设计内调用的器件供应商提供的模块而定,如:FIFO、ADD_SUB 等。在使用Vivado Simulator 时,仿真器所需的仿真模型/库是预编译好并集成在Vivado 中的,因此不需要进行额外的预编译操作,直接加载HDL 设计和TestBench 即可执行仿真。

2.功能仿真/HDL仿真步骤

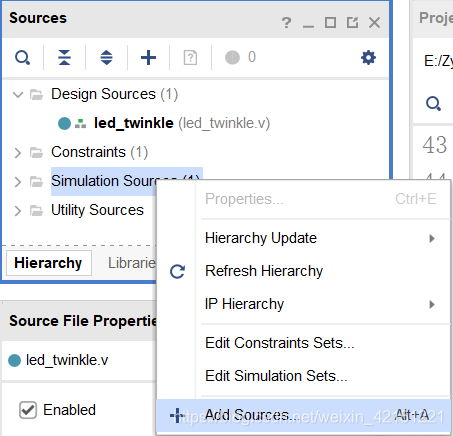

在Vivado IDE 中进行仿真,首先需要创建一个TestBench。我们点击“Sources”窗口中的“+”号(Add Sources 命令),在弹出的窗口中选择“Add or Create Simulation Sources”,如下图所示:

本文详细介绍了如何在Vivado 18.3中进行功能仿真,包括Vivado Simulator的特点,仿真所需文件,创建TestBench的步骤,以及仿真过程中的Scope、Objects和波形窗口的使用。通过实例演示了如何运行和管理仿真,为FPGA设计中的验证提供了清晰的指导。

本文详细介绍了如何在Vivado 18.3中进行功能仿真,包括Vivado Simulator的特点,仿真所需文件,创建TestBench的步骤,以及仿真过程中的Scope、Objects和波形窗口的使用。通过实例演示了如何运行和管理仿真,为FPGA设计中的验证提供了清晰的指导。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

824

824

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?