XDMA调试记录

1 XDMA硬件设计

1.1 XDMA IP核简介

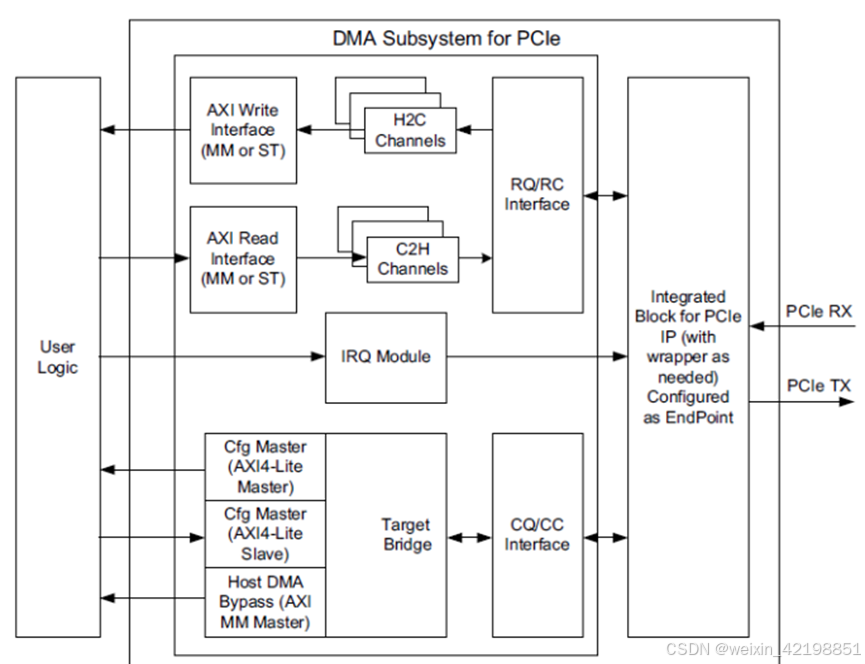

Xilinx 提供的DMA Subsystem for PCI Express IP(简称XDMA)是一个高性能,可配置的、适用于PCIE2.0,PCIE3.0 的SG 模式 DMA,提供用户可选择的 AXI4 接口或者 AXI4-Stream接口。具体的可参考官方文档PG055,一般情况下配置成 AXI4 接口可以加入到系统总线互联,适用于大数据量异步传输,通常情况都会使用到 DDR,AXI4-Stream 接口适用于低延迟数据流传输。

XDMA 是SGDMA,并非Block DMA,SG 模式下,主机会把要传输的数据组成链表的形式,然后将链表首地址通过BAR 传送给XDMA,XDMA 会根据链表结构首地址依次完成链表所指定的传输业务。

如上图所示,XDMA 提供如下接口:

- AXI4/AXI4-Stream:必须选择其中一个,用来数据传输。

- AXI4-Lite Master:可选,用来实现PCIE BAR 地址到 AXI4-Lite 寄存器地址的映射,可用来读写用户逻辑寄存器。

- AXI4-Lite Slave:可选,用来将XDMA 内部寄存器开放给用户逻辑,用户逻辑可以通过此接口访问 XDMA内部寄存器,不会映射到BAR。

- AXI4 Bypass接口:可选,用来实现PCIE 直通用户逻辑访问,可用于低延迟数据传输

1.2 XDMA硬件设计

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

877

877

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?