一、基础介绍

1、PCIE的输出接口常用金手指。

2、PCIE差用差分信号的方式传输。

3、PCIE X1 就是1个发送差分对,1个接收差分对。PCIE X4就是4个发送差分对,4个接收差分对.

X8、X16亦是如此。

4、PCIE共有的引脚是: WAKE#信号、SMBUS、JTAG、热插拔信号PRSNT1#、IIC信号 SLCK SDA、时钟差分对RFCLK+ RFCLK-、复位信号PERST#。

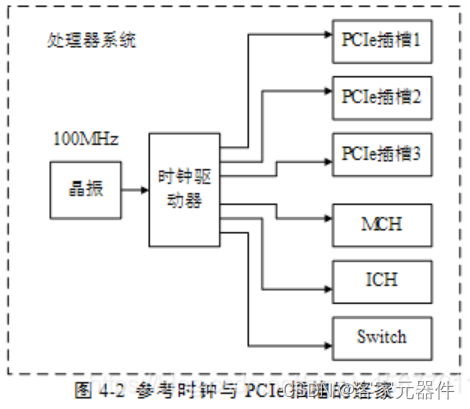

5、PCIE插槽和PCIE设备都需要差分时钟信号。频率的范围是100MHz±300ppm。

目的是与处理器系统同步。不同PCIE插槽间RFCLK+ RFCLK-差分时钟的传送延时差约为2.5ns。

PCIE设备可以使用独立的参考时钟,不使用RFCLK+ RFCLK-信号。可在PCIE设备配置空间的Link Control Register中配置。

Common Clock Configuration == 1,则说明与PCIe链路端设备使用同相位的参考时钟;

如果为 Common Clock Configuration == 0,则表示用的是异步时钟。

PCIE是交流耦合方式。

3972

3972

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?