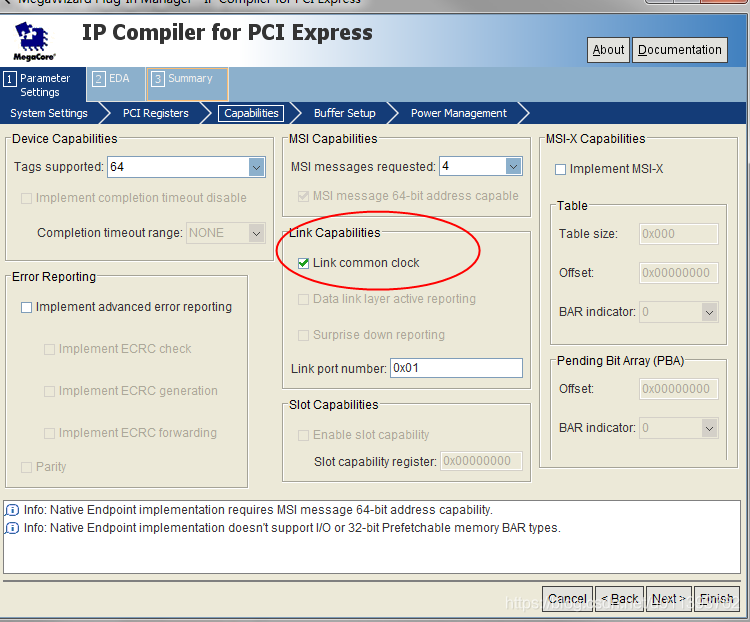

PCIe插槽需要提供参考差分时钟,其频率范围在100MHZ±300ppm。在PCIE IPcore生成过程中含有“Link Control Register”中,“Common Clock Configuration”位

当该位为1时,表示该端与PCIE链路对端设备使用“同相位”的参考时钟(如FPGA与CPU相连,FPGA输入的参考时钟由CPU输出,CPU与FPGA有数据差分线tx/rx连接之外,CPU与FPGA还需要有两根差分时钟线连接);如果为0,表示该设备与PCIE链路的对端设备使用的参考使用是异步的,表示PCIE设备使用的参考时钟跟对端设备灭有任何联系。这个时候CPU与FPGA不需要两根差分时钟线连接,只需要数据传送时差分信号线tx/rx即可。

本文介绍了PCIe链路中参考差分时钟的作用及配置方法。重点讲述了通过设置“CommonClockConfiguration”位来确定链路两端设备是否使用同相位参考时钟,及其对数据传输的影响。

本文介绍了PCIe链路中参考差分时钟的作用及配置方法。重点讲述了通过设置“CommonClockConfiguration”位来确定链路两端设备是否使用同相位参考时钟,及其对数据传输的影响。

1154

1154

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?