Xilinx 7系列时钟篇(UG472)

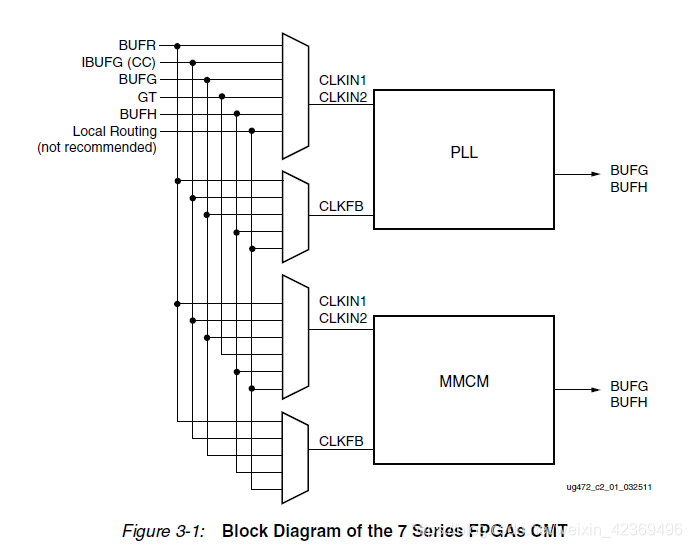

CMT结构图

MMCM、PLL的功能可以总结为3点:

(1)

频率综合:将外部输入的固定频率时钟调理成多路可调节频率的时钟。

(2)

去抖动(百度时钟抖动的含义,这里不具体介绍)。

(3)

去偏斜(百度时钟抖动的含义,这里不具体介绍)。

MMCMs和PLLs

7系列设备包含多达24块CMT。MMCMs和锁相环作为频率内部时钟和deskew时钟。

7系列FPGAs中的锁相环是MMCM功能的一个子集,它基于MMCM,不一定基于以前的锁相环设计。MMCM支持的其他功能包括:

- 使用CLKOUT将HPC直接发送到BUFR或BUFIO [0:3]

- 倒转时钟输出(CLKOUT[0:3]B)

- CLKOUT6

- CLKOUT4_CASCADE

- CLKOUT0_DIVIDE_F的分式除法

- CLKFBOUT_MULT_F的分数乘

- 精细移相

- 动态移相

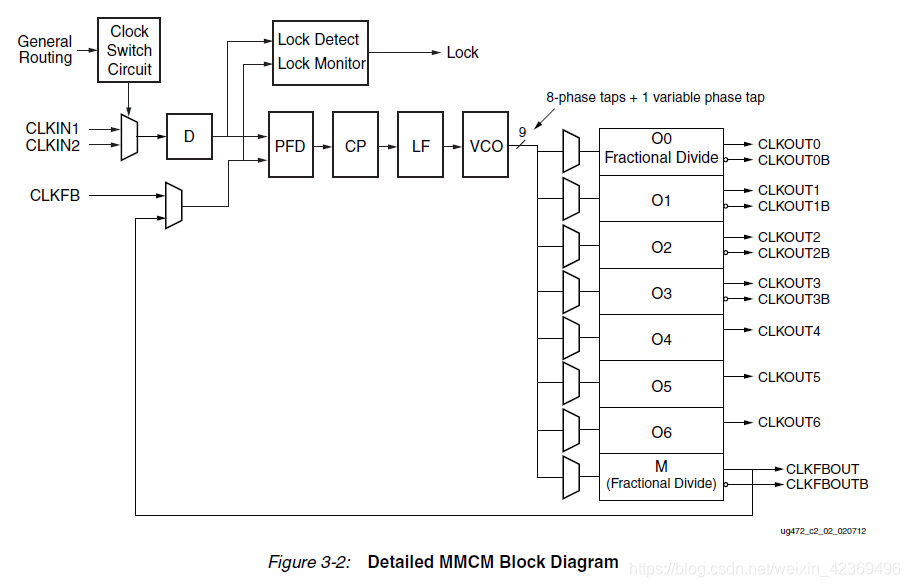

输入多路复用器从IBUFG、BUFG、BUFR、BUFH、GTs(仅限CLKIN)或互连(不推荐)中选择参考时钟和反馈时钟。每个时钟输入都有一个可编程计数器分频器(D)。相频检测器(PFD)比较输入(参考)时钟和反馈时钟上升边缘的相位和频率。如果保持一个最小的高/低脉冲,占空比是辅助的。

PFD用于产生与两个时钟之间的相位和频率成比例的信号。这个信号驱动电荷泵(CP)和环路滤波器(LF)产生VCO的参考电压。PFD向电荷泵发出向上或向下的信号和环路滤波器,以确定VCO应在较高或较低的频率运行。当压控振荡器以过高的频率工作时,PFD会触发一个下行信号,导致控制电压降低,从而降低压控振荡器的工作频率。当压控振荡器的工作频率过低时,上行信号会增加电压。VCO生产8个输出相和一个可变相用于精细相移。

可以选择每个输出阶段作为输出计数器的参考时钟(图3-2和图3-3)。每个计数器都可以为给定的客户设计独立编程。

还提供了一个特殊的计数器M。该计数器控制MMCM和锁相环的反馈时钟,允许广泛的频率合成。

除了整数除输出计数器外,MMCMs还为CLKOUT0和CLKFBOUT添加一个分数计数器。

上图咱们一目了然,MMCM有2个时钟输入,使用时任选1路即可,输入时钟经过PFD(phase-frequency detector),CP(charge pump),LF(loop filter)后产生一定幅度的电压输入到VCO,VCO产生频率与输入电压幅度成比例的高频时钟,再被除以M倍并反馈到PFD。因此VCO的输出频率是一个稳定的、输入频率M倍的高频时钟,该时钟除以不同的倍数(用户可调)即可输出时钟clkout0clkout6。另外第0路输出和反馈输出是可以被分数除法,且第0路第3路提供反相180度的输出,VCO的输出还可以精确调整相位,这是7系列FPGA特有的。

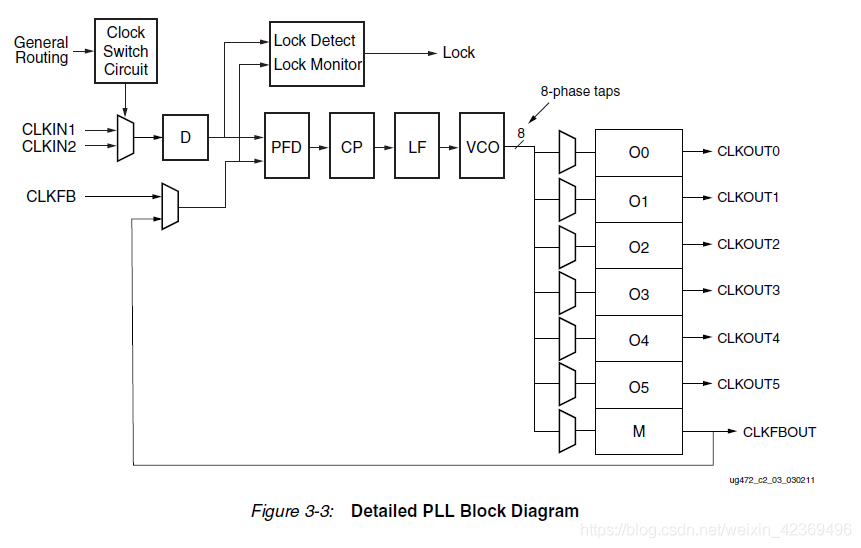

其结构与MMCM大体一致,但没有反相输出、分数倍数的除法、精确的动态相位调整以及CLKOUT6。

这里强调一下:MMCM、PLL均可实现时钟整数倍的频率综合、去抖、去偏斜,但MMCM还可以实现分数倍的频率综合、反相时钟输出以及动态的时钟相位调整。当然,对于咱们一般的应用来说,用不到MMCM的这些高端功能,两者使用没啥区别。

1173

1173

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?