前言:

本文介绍AXI Bridge For Pcie Express Gen3 Subsystem 的使用方法。这个IP兼具简单与实用,将PCIE协议层实现于内部,仅留出AXI用户接口,不需要处理复杂的PCIE协议数据。

本文无关PCIE协议本身,仅分享实用性的工程经验,以PCIE IP为核心,一步一步搭建一个简单的子系统,以此说明用法。

文中所有内容均已通过项目检验。

1.时钟

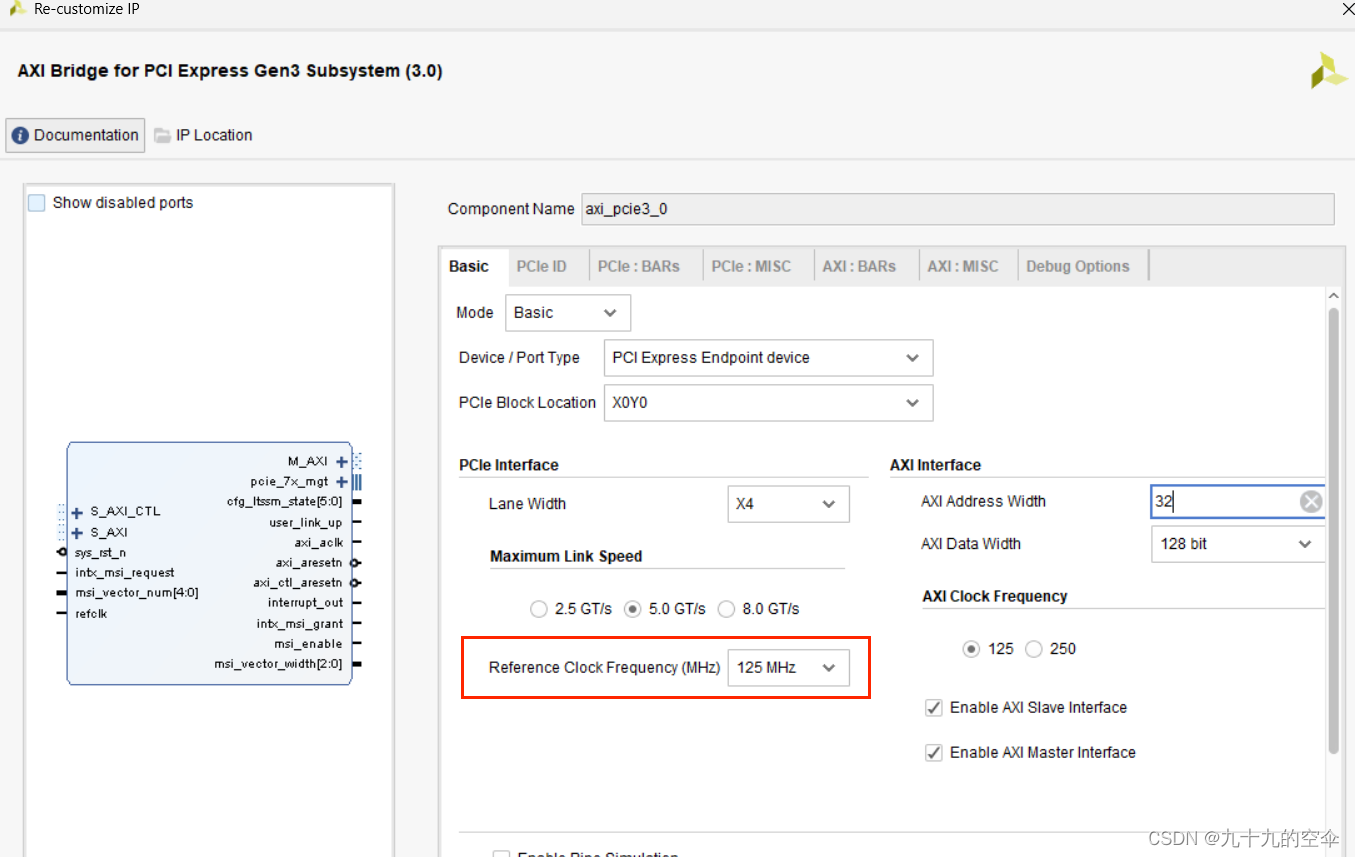

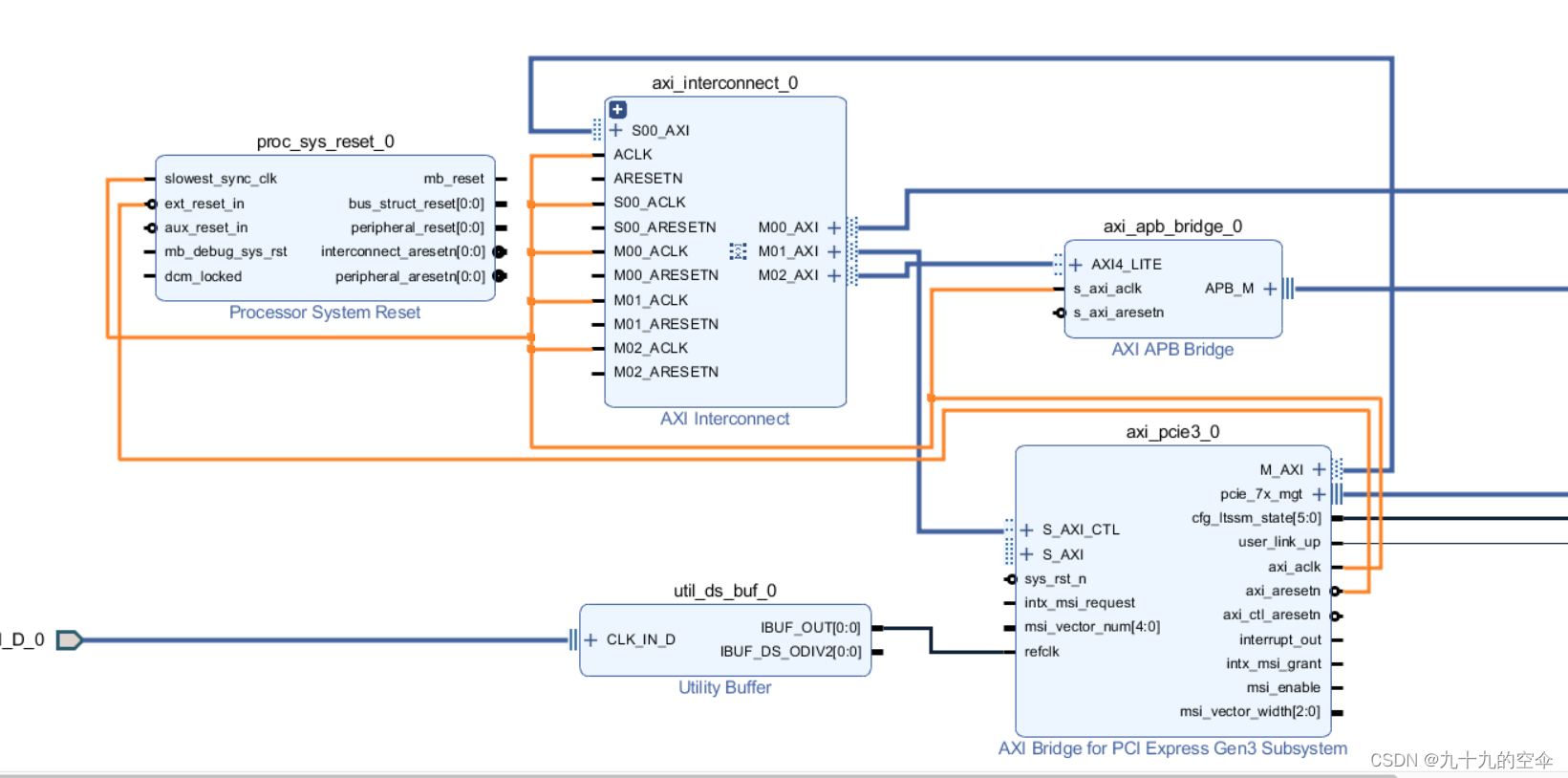

IP需要一个参考时钟,即下图中的refclk,频率可设置,如图,这里选择125MHz。

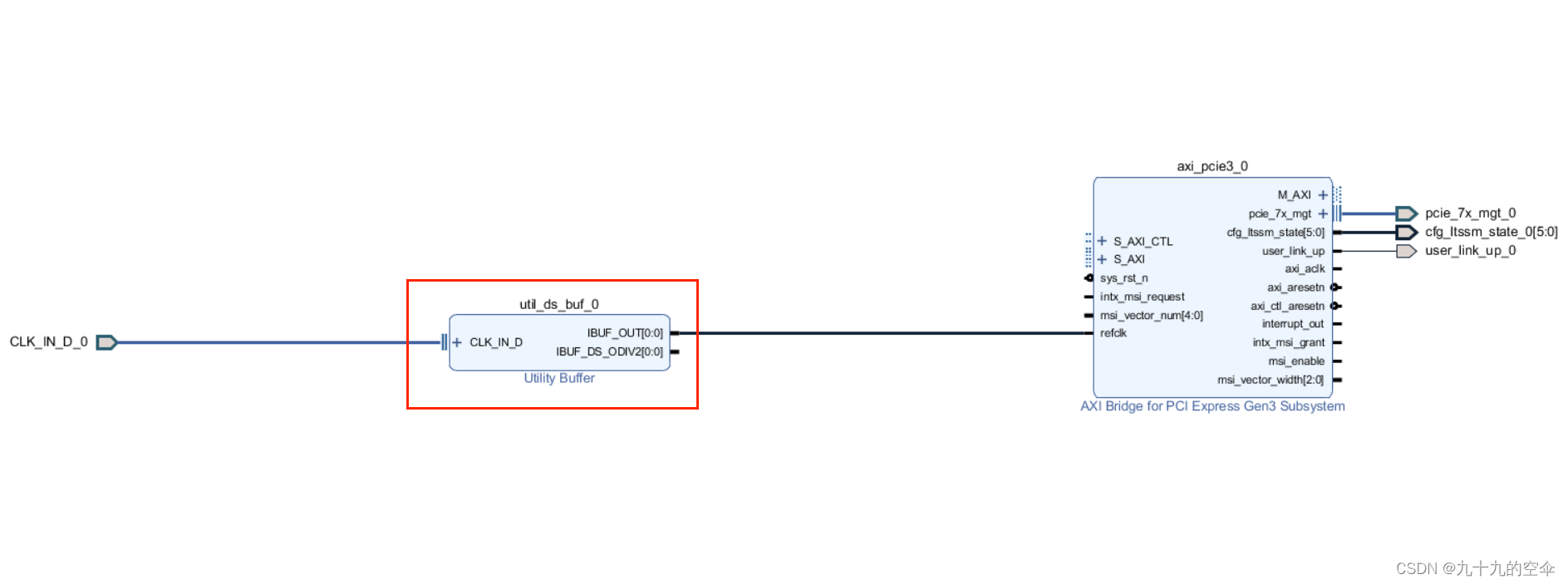

在外部,时钟源是差分的,需要通过一个Utility Buffer转成单端。

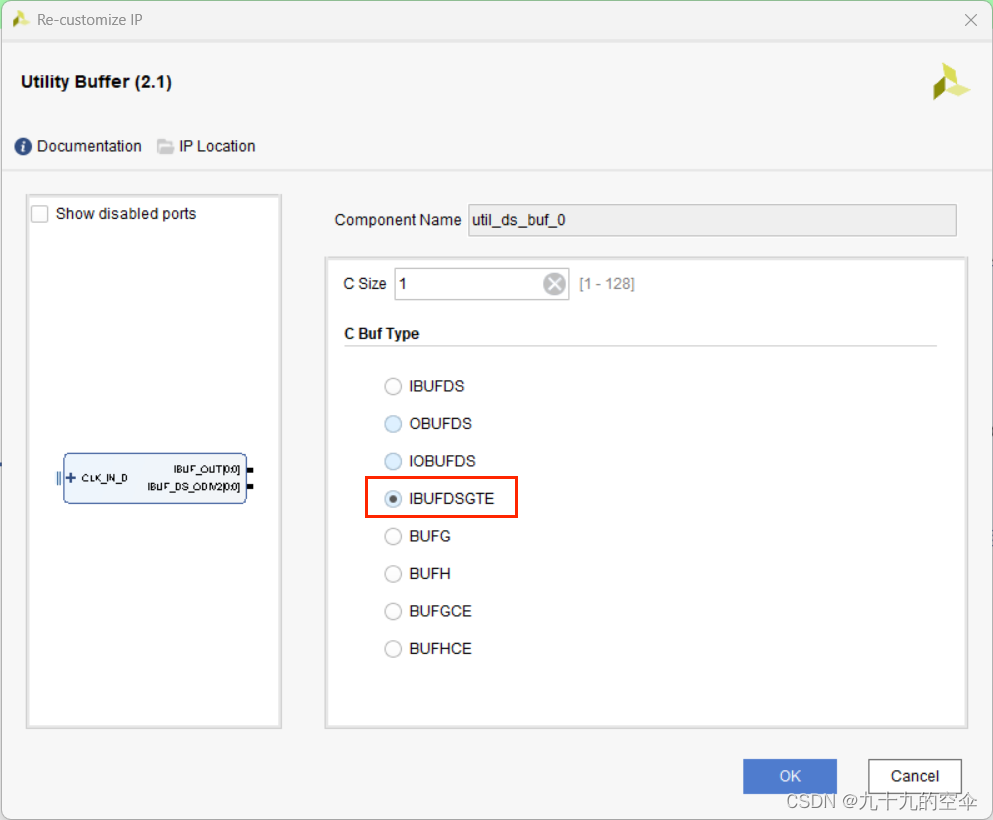

注意Utility Buffer内部选择IBUFDS GTE,因为PCIE需要用到GT收发器,该参考时钟即为高速接口 BANK的参考时钟,必须选择高速接口专用的IBUFDS_GTE

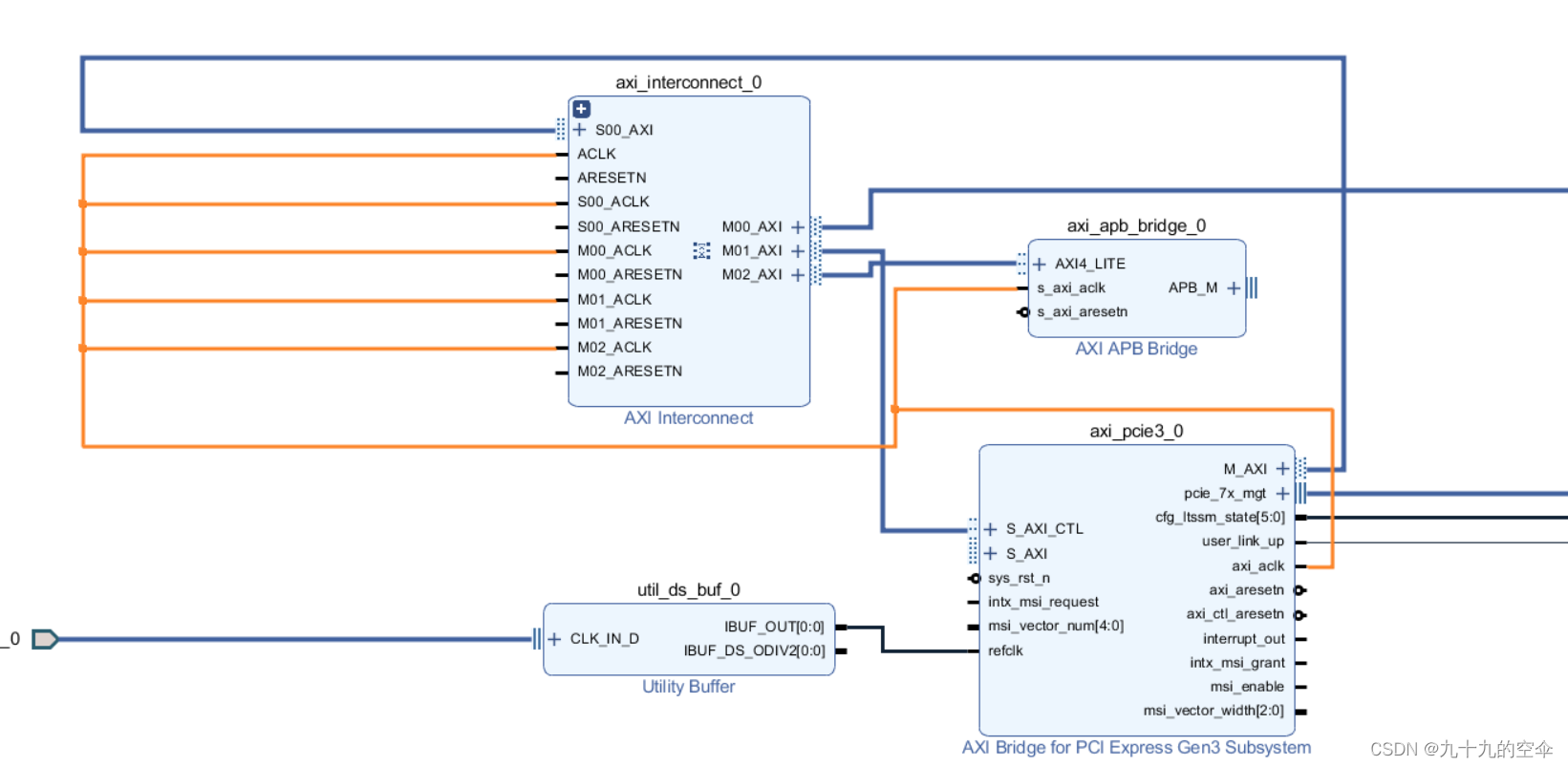

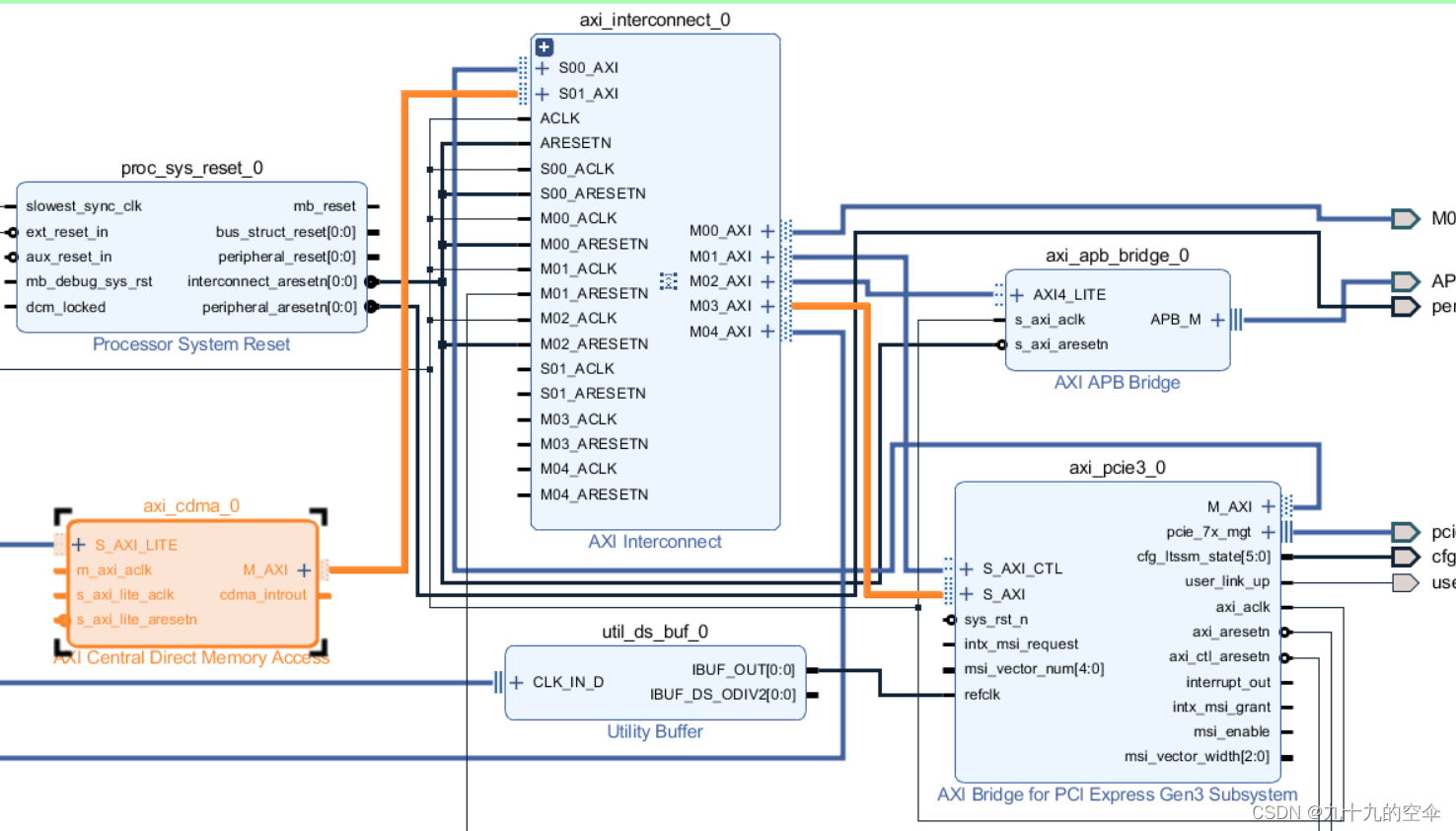

PCIE输出的axi_aclk,可作为axi互联模块和一众外设的时钟信号,如图,图中的APB桥, 以及图中没有的各种APB外设都需要用这个时钟。

2.复位

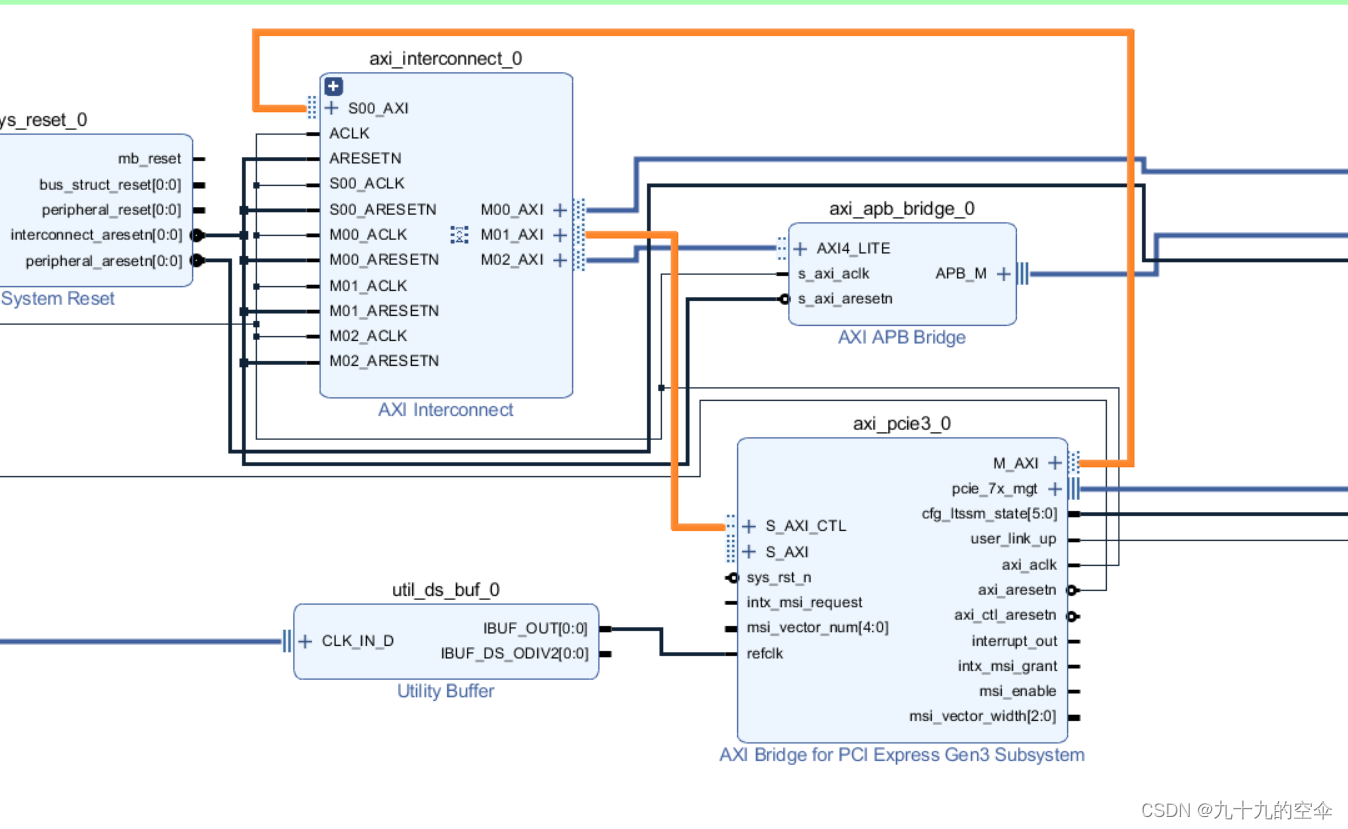

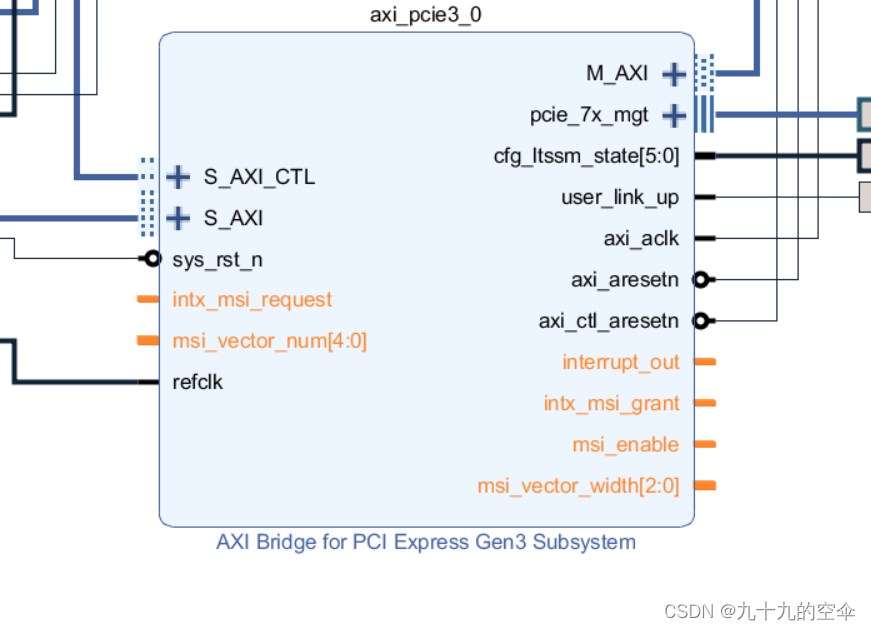

首先,PCIE IP有一个系统复位信号输入sys_rst_n,这个没有很固定的用法,可以用FPGA的全局复位信号,或外部逻辑生成的复位信号,如图

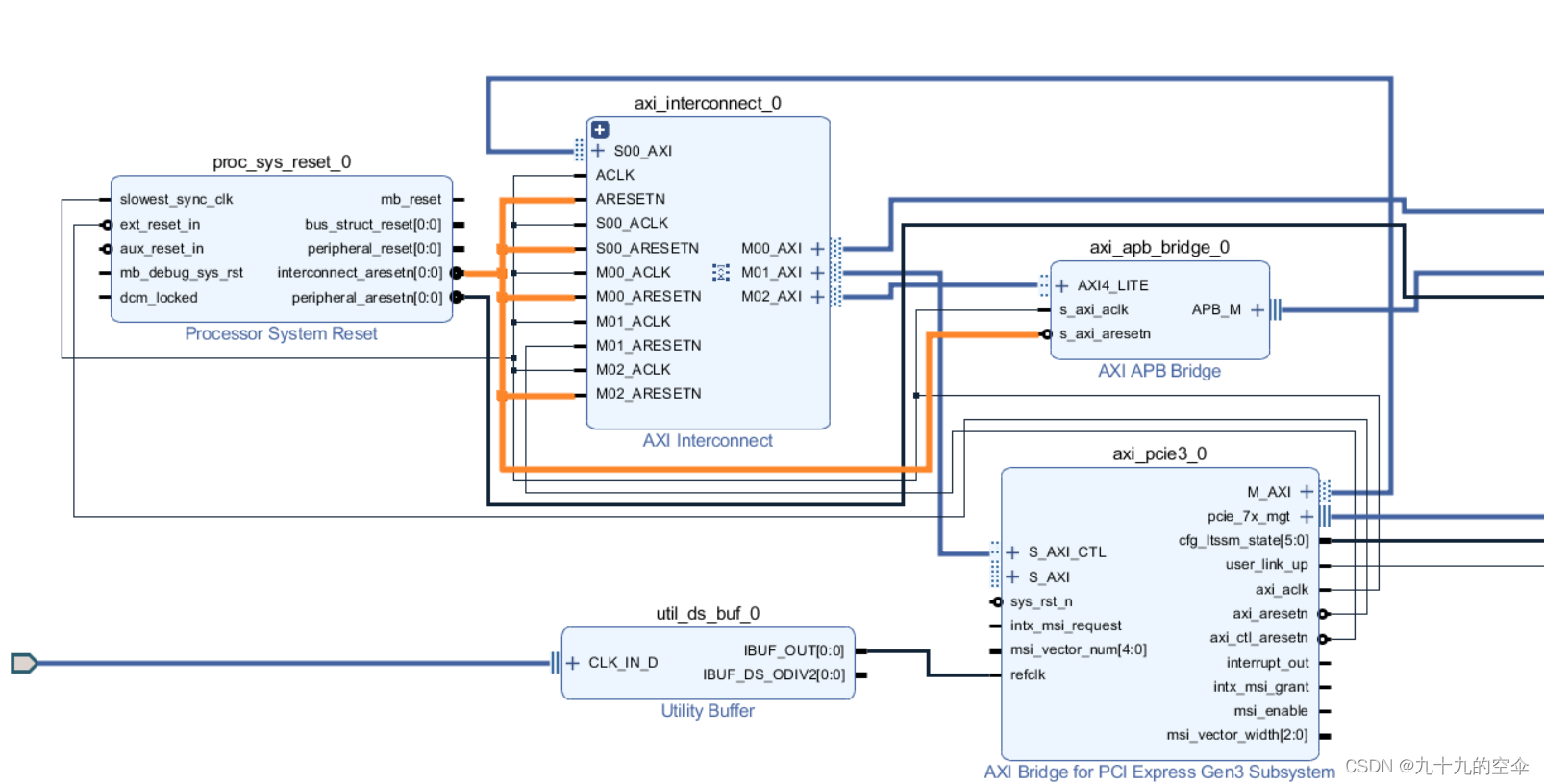

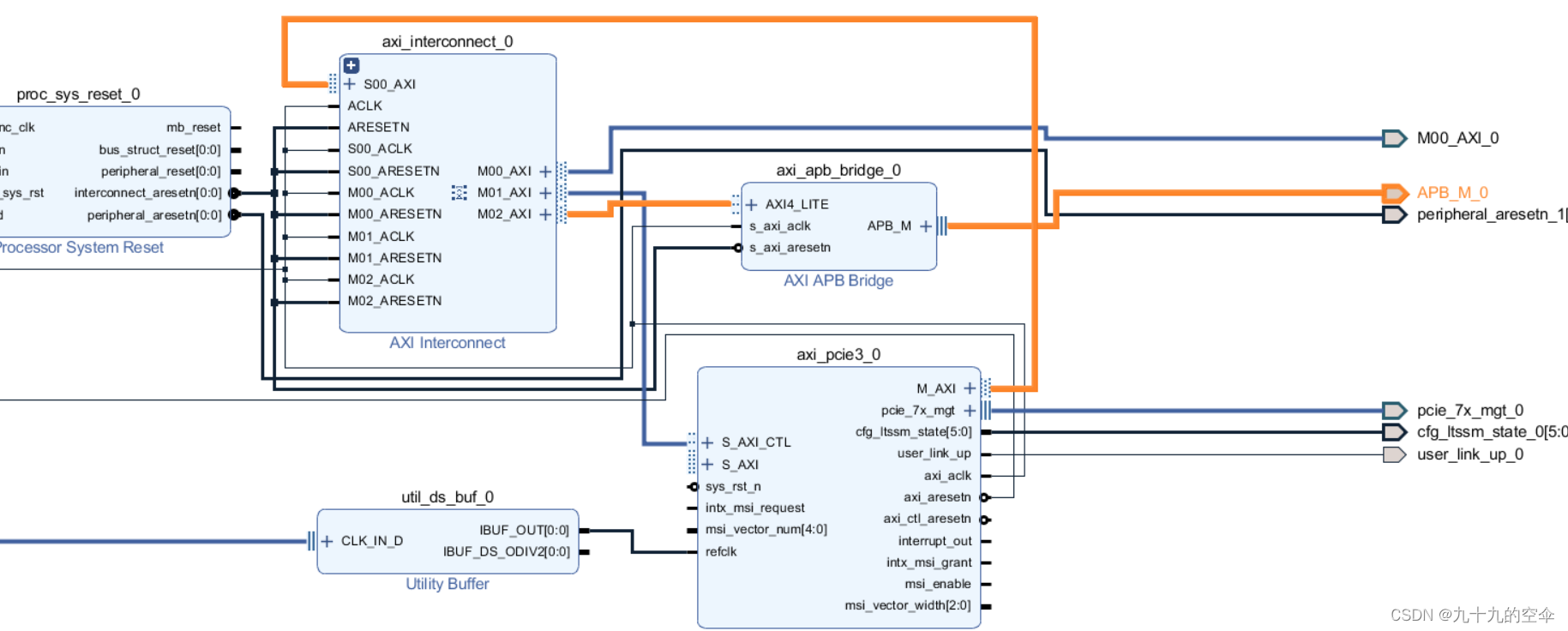

接下来处理系统内部复位,首先加入一个processor system reset IP核,使用PCIE IP输出的axi_aclk和 axi_aresetn作为输入,如下图

processor system reset IP输出两个复位信号:

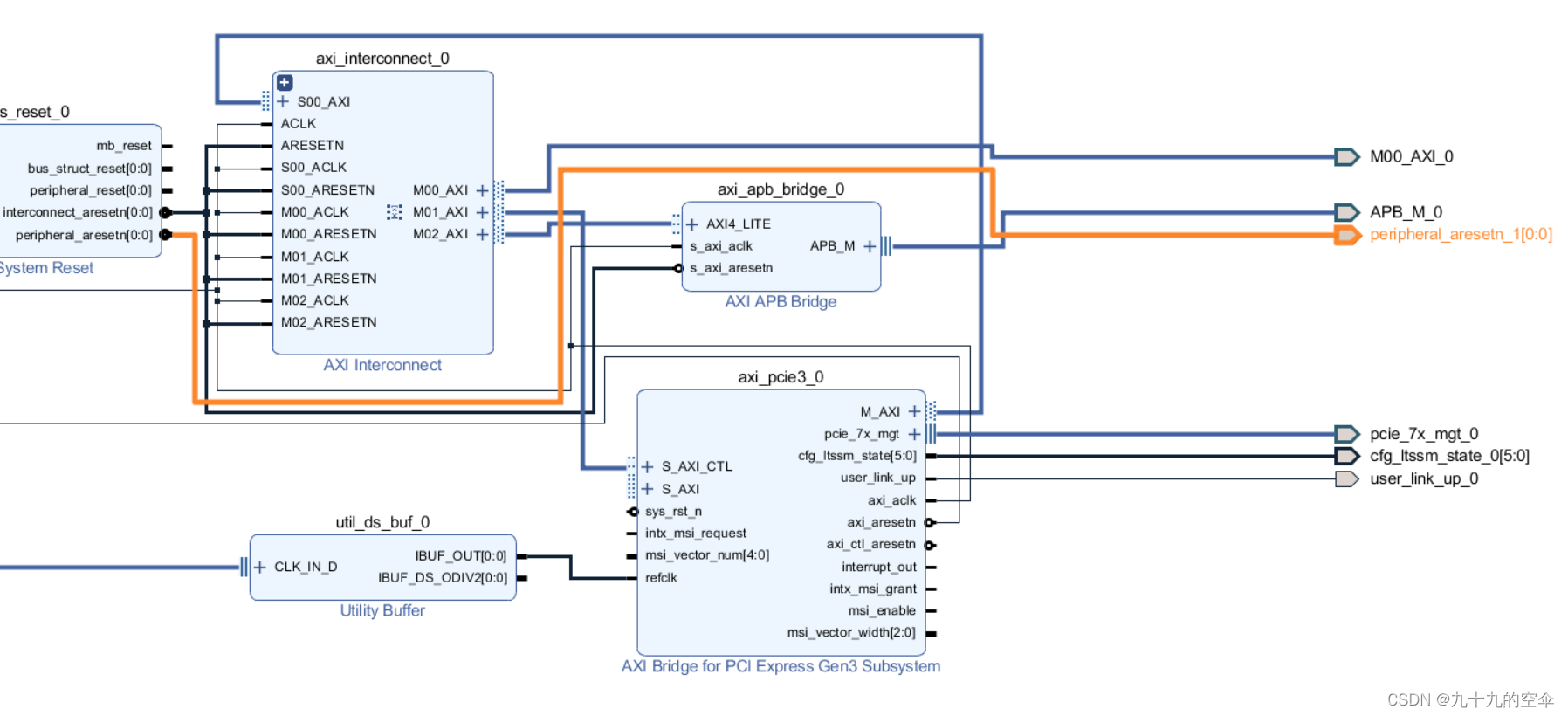

①AXI互联系统复位信号,interconnect_aresetn,AXI接口的复位信号都用它,如图。

此处有一个特例,AXI_CTL接口有专用的复位信号,不能混用,特别注意,如图

②外设复位信号peripheral_aresetn,比如APB外设就可以用它作为复位信号,我们就直接引出去了,如图。

interconnect_aresetn和peripheral_aresetn差别在于,后者将晚于前者释放,参见PG164。其实并无太大差别,工程实践中混为一谈也不是不可以,但谨慎起见还是分开。

3.数据传输通路

PCIE是有主从之分的,FPGA一般作为从端(即Root Terminal,RT),主端(Root Complex,RC)可以是DSP或者是CPU。

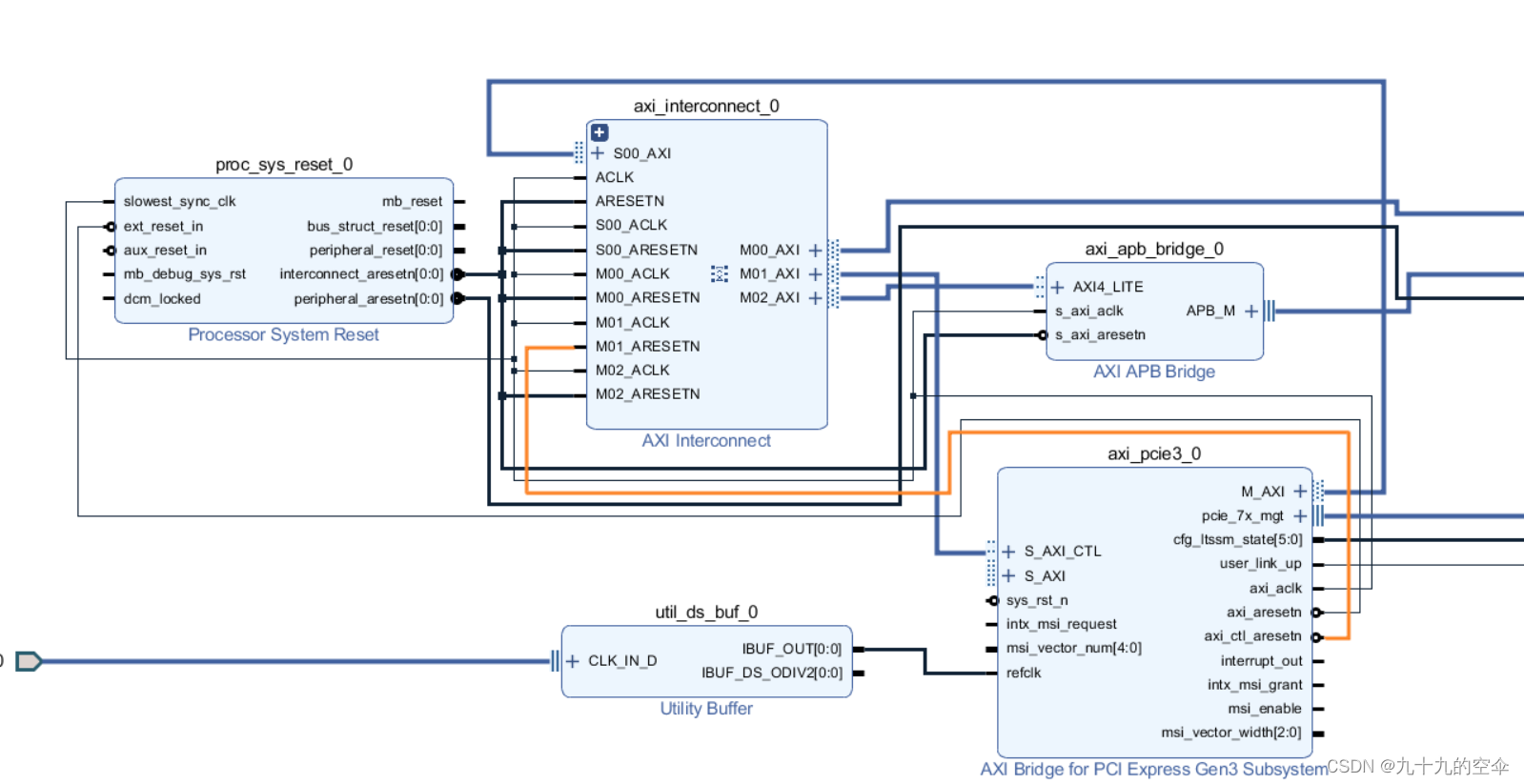

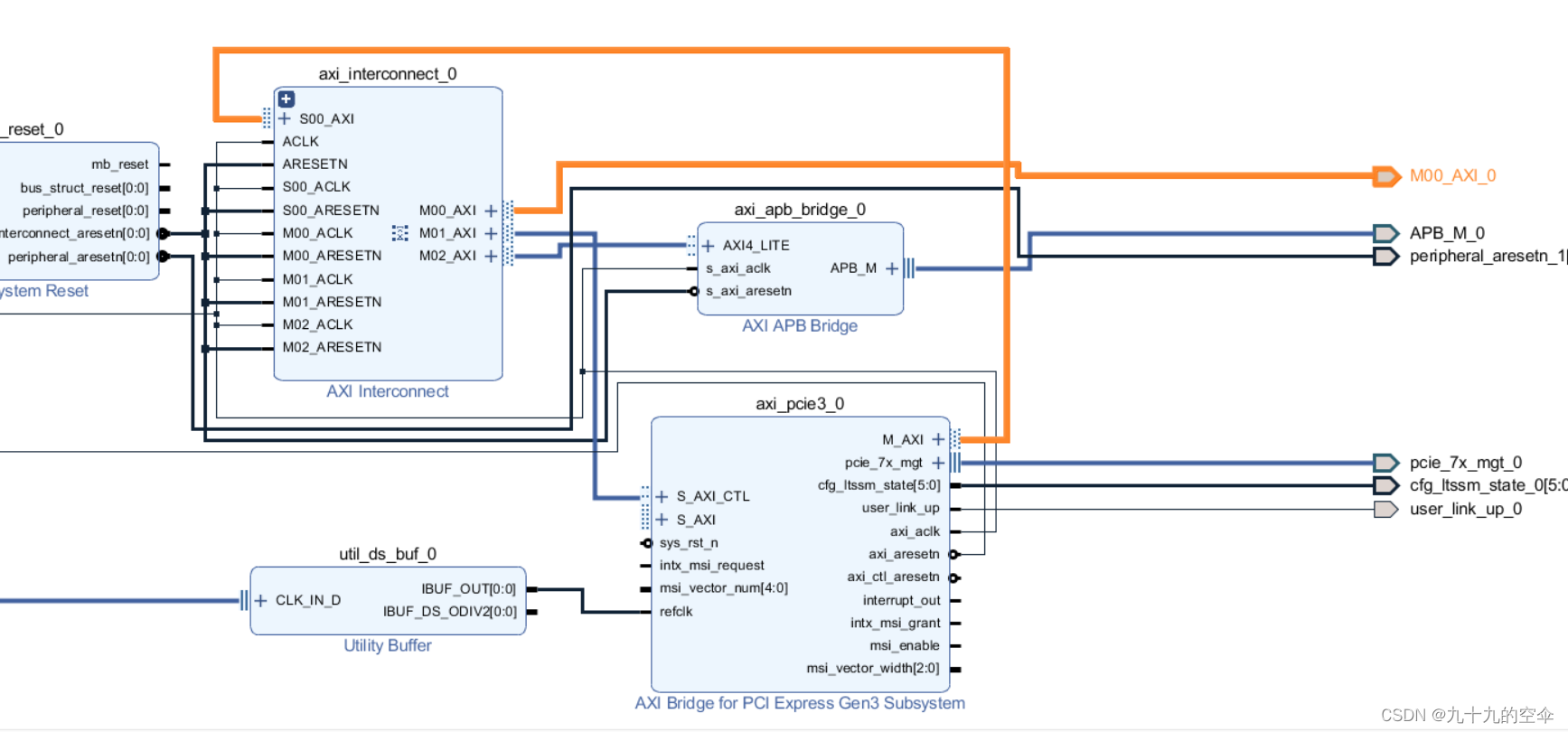

RT主动发起的数据传输,通过PCIE IP的M_AXI接口给到FPGA,可以通过一个互联模块完成对各地址空间访问。举例说明如下:

如图,表示RC通过PCIE给FPGA的APB外设传输数据。

RC也可以访问RT的配置空间,如图

或者,也可以直接把AXI引出去,连接DDR子系统之类的,如图

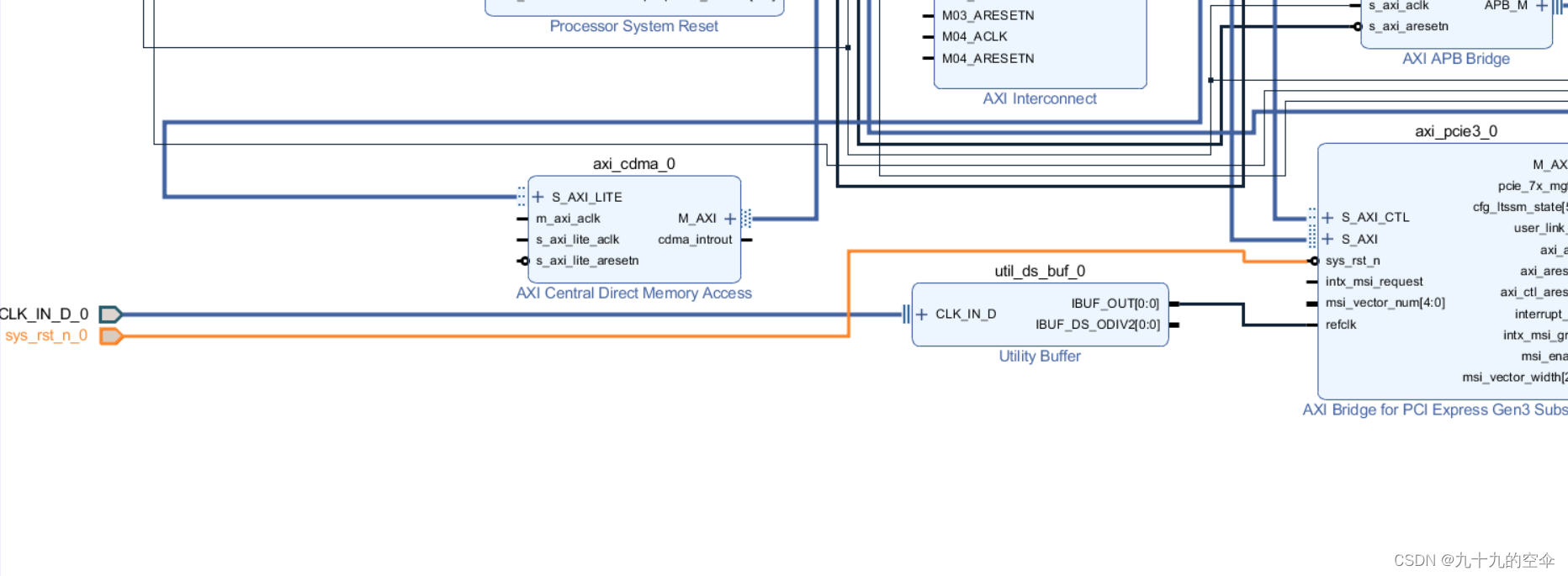

FPGA作为从端也是可以主动发起数据传输的,这时候就要用到S_AXI,比如通过一个CDMA实现对RC端地址空间的访问,如图

PCIE还有中断信号可以用,如图。

不是很复杂,可以自己了解下。

至此已经有一个简单的基本开发框架了,但还是不能直接用,因为PCIE IP内部配置同样重要,这部分在下一篇文章中再讲吧。

本文详细介绍了如何使用AXIBridgeForPcieExpressGen3Subsystem,包括设置时钟、复位机制、数据传输路径以及PCIE的主从模式,为读者提供了一个基于PCIEIP的简单子系统搭建步骤。

本文详细介绍了如何使用AXIBridgeForPcieExpressGen3Subsystem,包括设置时钟、复位机制、数据传输路径以及PCIE的主从模式,为读者提供了一个基于PCIEIP的简单子系统搭建步骤。

6539

6539

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?