为了节省大家时间,摘要奉上,enjoy~

大数据AI/ML应用爆发驱动大内存需求,但内存增长受限,CXL互联方案应运而生

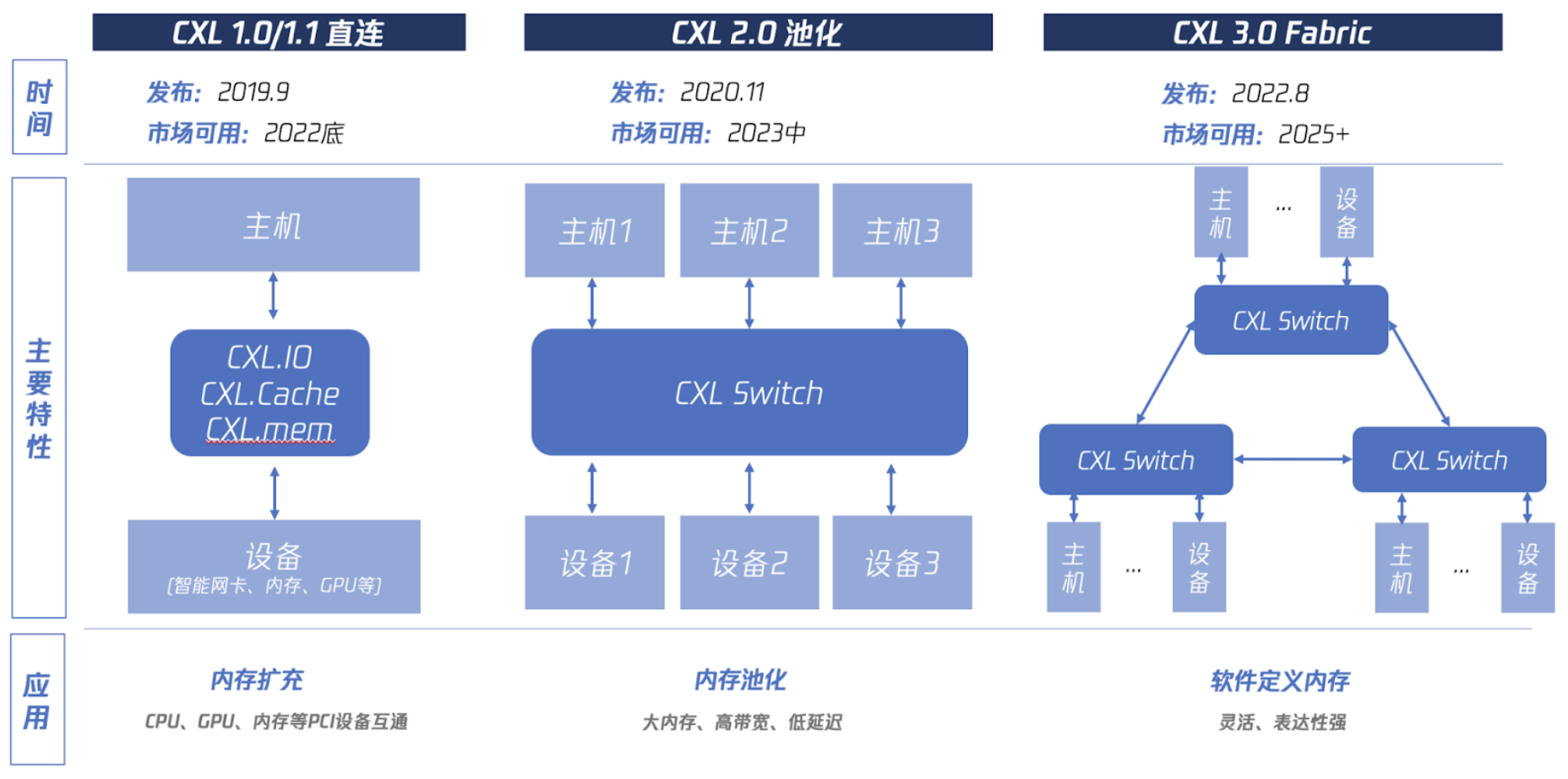

CXL分为1.0/2.0/3.0版本,分别提供直连、池化、Fabric能力,预计在2022年/203年/2025年之后市场可用,目前看来池化对于软件的影响最大

CXL更多是对于已有架构的性能优化,全新的机会不多,较大的机会在于系统软件、内存即服务,以及内存数据库和内存云结构

CXL大概率将成为跨计算引擎的内存结构标准,短期利好云厂商,长期会数据中心架构产生结构性的变革

大数据AI/ML计算驱动大内存需求,但内存不够用了

随着健康码/行程码的广泛应用,大家可能已经亲身体会过被大数据支配的恐惧。另外就是最近ChatGPT已经被大家玩坏了~

其实还有很多大家不常接触的应用,如:

这些应用数据量,处理这些数据需要强大的算力。

为了加快CPU速度,需要把大量数据放入内存,甚至需要迭代计算(典型是ML的模型训练),这就造成了对大内存的强烈需求。

直接堆内存条不行?不行,理由有2个:

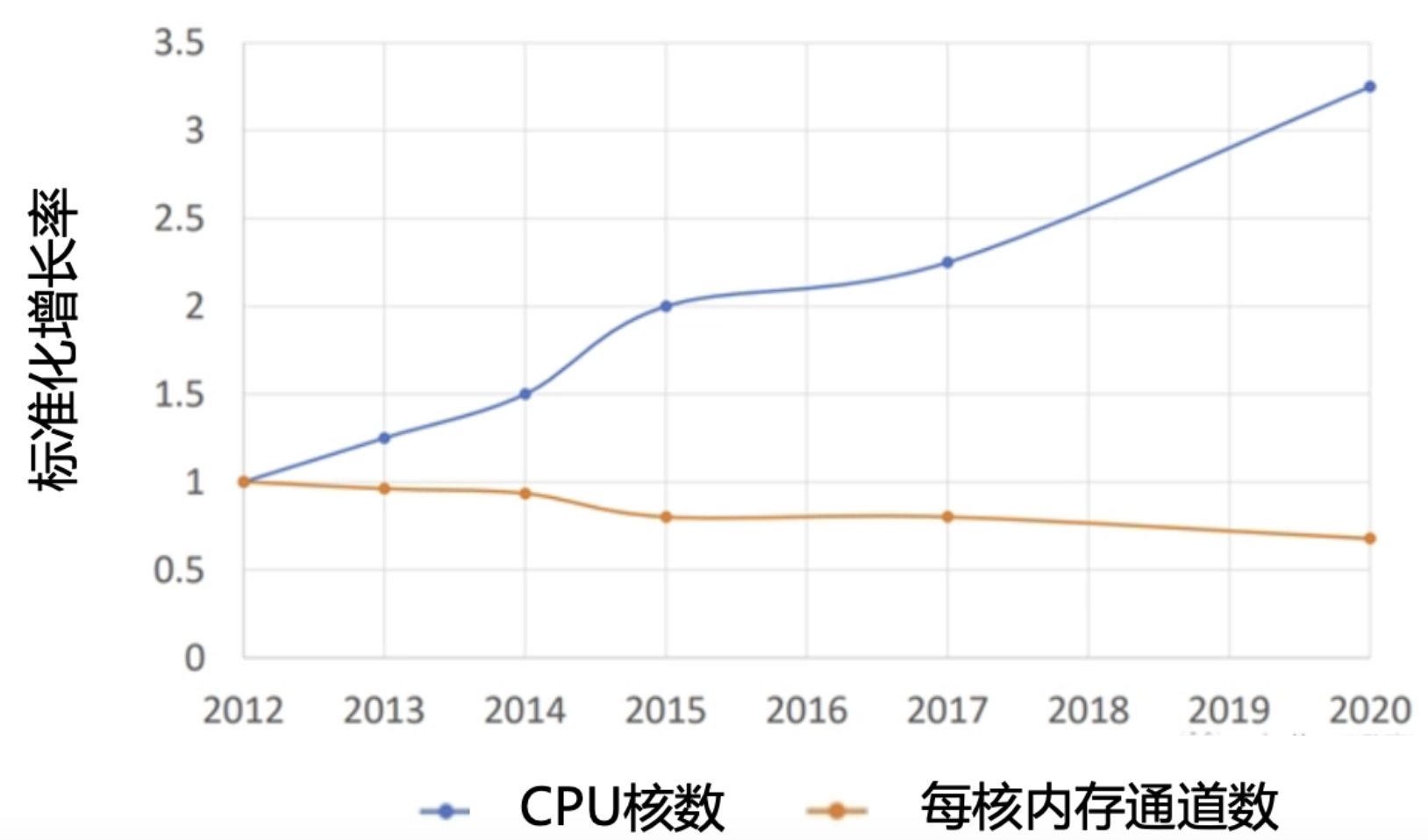

理由一:CPU能装的内存条是有限的

CPU核心数目前已经二十四核,甚至更多,但是每核能插入的DDR内存条数量是有限的。这么一剪刀差下来,每核能够使用内存反而是下降的,且差距不断在扩大。

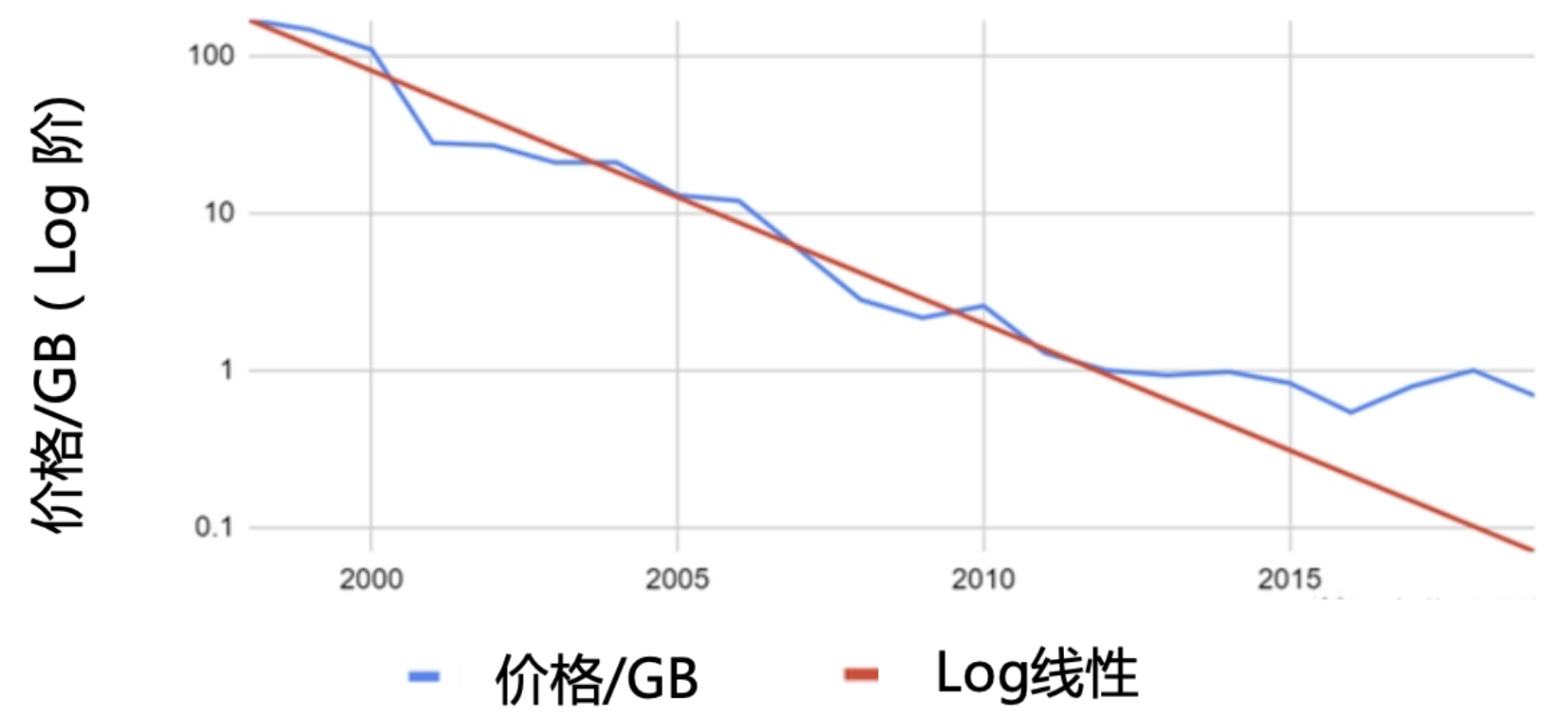

原因二:内存价格降不下来

CPU价格是一降再降,但是内存却从2013年起基本保持平稳,大概20元/GB,相比之下,SSD大概 1元/G,硬盘 4毛/G,是不是差很大~

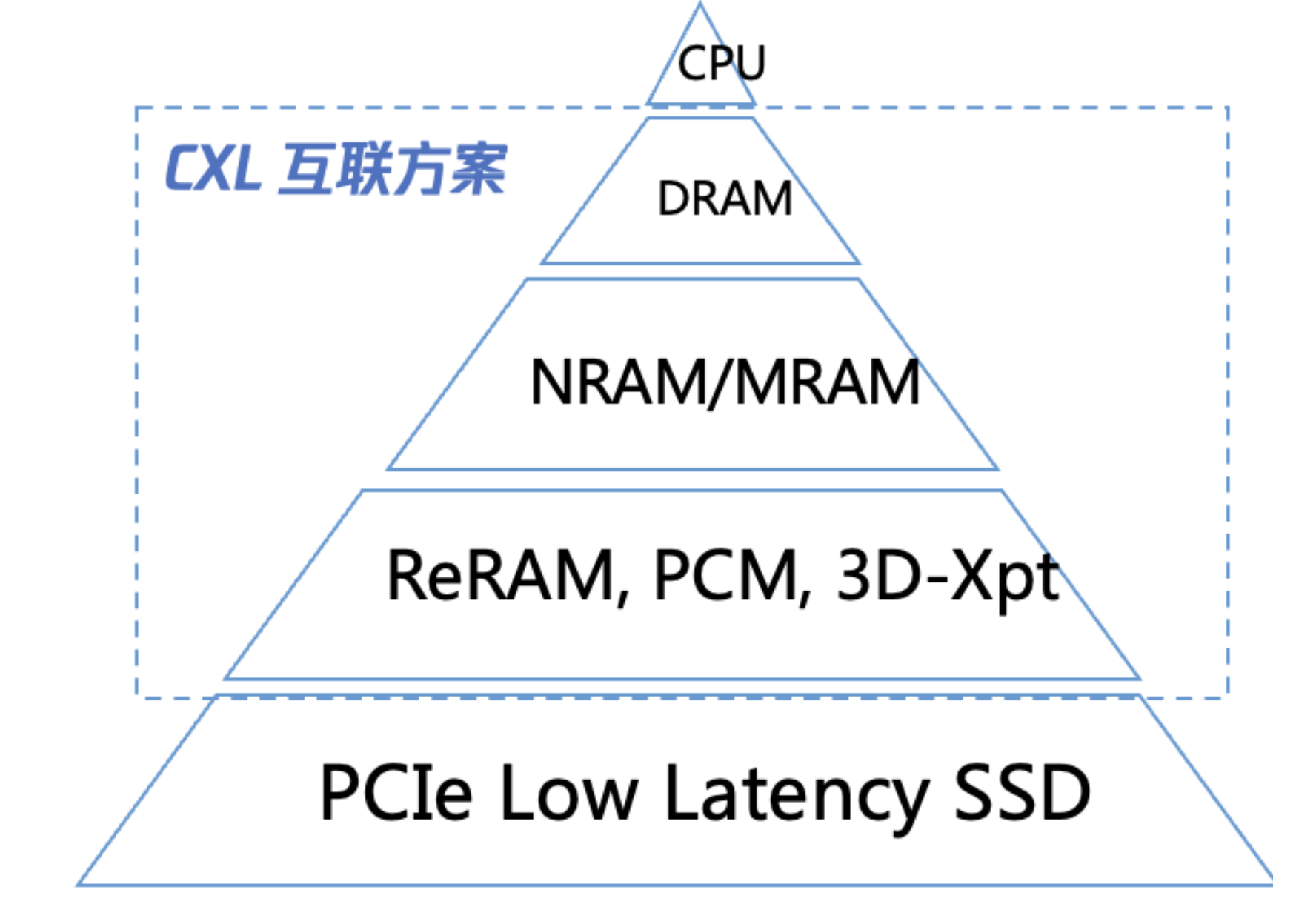

不是还有PCIe外部设备嘛,内存拿出来一起用?

可以,但是一起用总需要有个规矩,也不能乱来是吧,这个规矩就是CXL(Compute Express Link),较专业定义为:

CXL是一种开放性互连协议标准,旨在提供 CPU 和专用 加速器、高性能存储系统之间的高效、高速、低延时接口,以满足资源共享、内存池化和高效运算调度的需求。

其实术语我看的也晕,大家理解它做的啥事就行了~

这个想法看上去也不难嘛,为什么现在才有CXL?

其实,聪明人还是很多的,之前有很多类似协议,如Gen-Z(HPE)、OpenCAPI(IBM)以及CCIX (Xilinx)。但是问题是,人家老大Intel想多卖自家的CPU,不屑于参与,导致一直没有成气候。

但是这次不一样,CXL本身就是Intel提出来的,主要是因为受NVIDIA GPU强劲挑战,Intel想做一个大局搞开放,所以这次声势很大~

所以,CXL具体是啥?

前面提到过,CXL主要目的是让大家把内存共享出来一起用,协议本身也是一直在演进的。

从2019年9月份发布CXL 1.0/1.1,到2020年11月发布CXL2.0,到最近发布CXL 3.0,它的功能一直在发生着变化,总结如下:

CXL1.0/1.1 可归纳为“直连”,也就是让主机CPU可以直接访问PCIe设备的内存,具体分为三个子协议:CXL.io用于设备注册发现、CXL.cache用于设备访问CPU内存、CXL.mem 用于CPU访问设备内存。这可达到主机内存扩充的目的。

CXL2.0 可归纳为“池化”,就是让多个主机CPU和多个设备可通过一个CXL Switch硬件连接在一起,可以相互访问,在较小延迟影响的前提下提供高容量大带宽。这可达到内存池化的目的。

CXL3.0 可归纳为Fabric,可以让多个Switch形成级联结构,支持更复杂的结构。这可以达到“软件定义内存”的目的,此处借用了“软件定义网络”的概念,具体能干啥我暂时也想不出来~

当然,目前只是协议发布,真正到市场使用大概还需要一段的时间,预计CXL 1.0/1.1需要到2022年,CXL 2.0要到2023年中,至于CXL 3.0可能要等2025年之后了。

那CXL有啥应用,有哪些新机会?

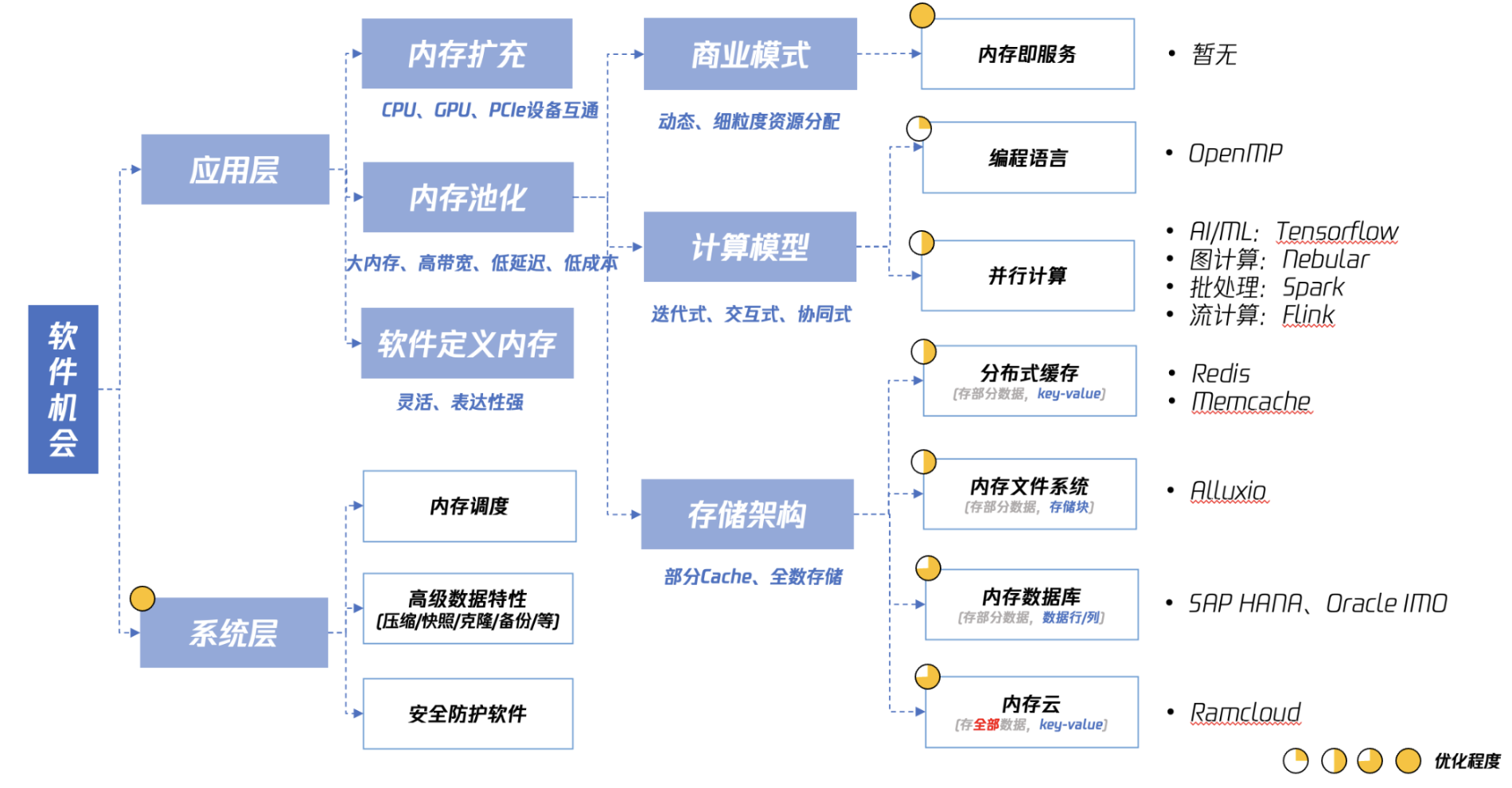

系统盘点了CXL在软件方面(不涵硬件)的新机会,总结如下:

可以初步得出结论:

CXL更多的是对于已有架构进行性能优化,全新机会并不多。

目前看来全新的机会包括,1)系统层的内存管理软件,以及2)应用层内存即服务,其余的均为现有系统的优化增强,图中以圆圈面积表示优化强度。

系统层

先从系统软件层面看,由于CXL需要支持这么复杂内存共享结构,必须有一套新软件支撑,包括三个机会:

-

内存调度管理器;

-

内存高级数据特性,包括内存压缩、快照、克隆、备份等;

-

内存安全防护;

这个将是新的机会,也有看到创业厂商想做此类的事情,但是这块核心的风险是,系统软件和CXL协议本身界限不是特别清晰,有可能就是做着做着,为CXL打补丁了,并不能成为一个产品。

应用层

CXL1.0/1.1所做的事情在于建立基础,而CXL3.0支持更复杂的结构,本文认为更多的应用在于CXL2.0的池化特性。

新技术一般会有两层面应用,一个是技术产品创新,另外就是随之而生的新商业模式。

商业模式

池化内存容量大、粒度细、分配灵活,直接衍生出“内存即服务”模式,这个是利好云厂商的。

云厂商卖内存通常有以下痛点:

-

内存必须绑定计算实例售卖

-

内存售卖粒度较粗

-

内存无法超卖

-

售卖的内存大部分闲置,内存利用率低

在内存池化场景下,云厂商可以提供内存PaaS API服务,只卖内存给应用;也可以细粒度按需分配,收费更灵活,同时可以超卖内存,并将平常闲置的内存进行更高效的利用。

调查发现,在微软Azure,有高达25%的内存都是闲置的,有50%的虚拟机使用的内存占比仅为50%。谷歌也类似,谷歌服务器集群中DRAM内存平均利用率约为40%,这将是巨大的机会。

不过这个机会虽然诱人,却是云厂商的,跟创业厂商没有什么关系~

「文章较长,怕大伙看累,且听下回分解」

关于我

我是张范,美元基金投资人,关注Data/AI/VRAR/区块链等Infra领域早期项目。企业服务领域十多年经验,前BAT产品负责人,前中科院技术专家,美国顶尖商学院MBA。寒冬中期待交流合作,让我们相互取暖,一起守得云开见月明~

联系我

欢迎各路大佬指导!

关注我,获取行业趋势、创业机会、产品洞见:)

6749

6749

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?