1、转换器理论信噪比

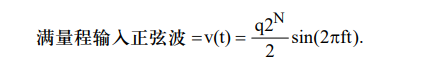

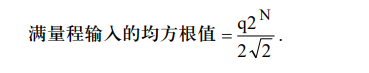

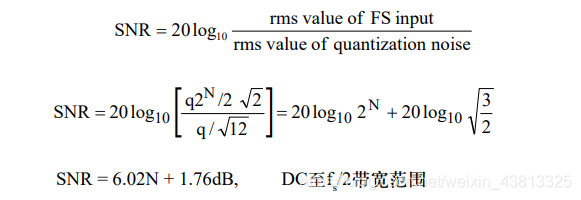

理想转换器对信号进行数字化时,最大误差为±1/2LSB,量化噪声近似于高斯分布,几乎均匀地分布于从DC至fs/2的奈奎斯特带宽。其量化误差可以通过一个峰峰值幅度为q(一个LSB的权重)的非相关锯齿波形来近似计算。现理论信噪比可以通过满量程输入正弦波计算,可以估计得到均方根量化噪声如下:

因此,输入信号的均方根值为:

因此,只考虑ADC量化噪声,理想N位转换器的均方根信噪比为:

这就是信噪比SNR = 6.02N + 1.76dB的来源,考虑DC~FS/2带宽范围,并且有效位数增加1信噪比提升6dB。

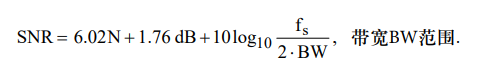

2、处理增益

在实际应用中,目标信号带宽往往小于奈奎斯特带宽,如果使用数字滤波器滤除带宽BW之外的噪声成分,只考虑目标带宽内的噪声,必然会带来信噪比上的提升,因此相较SNR=6.02N+1.76dB。只考虑带宽内噪声时信噪比还会有一个处理增益,即10log(Fs/2BW)。

从公式可以看出信噪比与有效位数、采样率和带宽的关系,同等条件下输入信号带宽越小得到的信噪比越好,另外根据信噪比和输入满幅功率可以得到带内噪声功率Pfs-SNR=Pnoise,从而可以得到噪声功率密度NSD=Pnoise-10log(BW),如果知道NSD也可以通过公式反算出SNR。在实际应用中需要考虑宽带信号由于器件非线性需要回退信号功率,通常将信号回退到PAPR可以满足大部分要求,因此上述公式就要变为:

SNR=6.02N+1.76dB+10log(Fs/2BW)-PAPR。

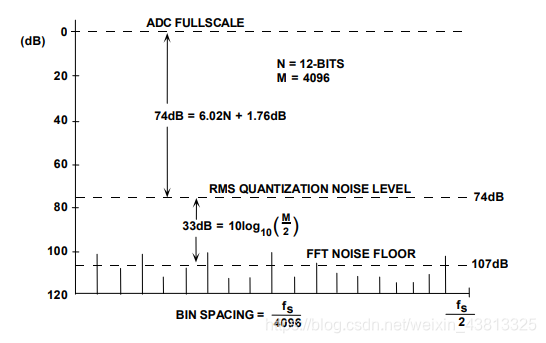

3、理想信噪比与处理增益

对于SNR为74 dB的理想12位ADC,4096点FFT将产生10log10(4096/2) = 33 dB的处理增益,因此总FFT噪底为74 + 33 = 107 dBc。事实上,FFT噪底可以通过提高FFT点数来进一步降低,就像模拟频谱分析仪的噪底可以通过缩小带宽来降低一样。因此,利用FFT测试ADC时,必须确保FFT足够大,使得失真能够与FFT噪底本身区别开,如下图所示转换器理论信噪比组成有理想信噪比加处理增益,在具体的ADC芯片应用是还可以通过减小信号带宽或者增加采样率提升信噪比。

4、举个例子

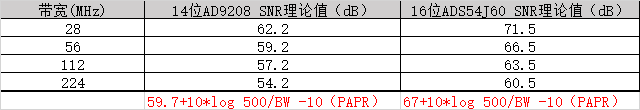

选用ADI的14位AD9208和TI 16位ADS54J60在1G采样率下做对比,中频500M得到不同带宽下其信噪比计算如下,其中59.7dB和67dB分别是满幅输入单音信号信噪比测试曲线图中获取的,可以看出信噪比差距大约在6dB左右,这是因为有效位宽ENOB差距1位。

另外单音测试功率不完全等于6.02N+1.76dB,比如ADS54J60有效位数10.8计算得到单音信号满幅功率输入时信噪比应该为66.7dB,这是因为系统热噪声以及时钟抖动造成的信噪比损失。

5、时钟抖动对信噪比的影响

ADC噪声由三部分组成:

①ADC量化噪声

②ADC孔径抖动

③ADC时钟抖动

前两者由芯片本身决定(量化噪声和孔径抖动),而ADC时钟抖动由外供时钟参考决定,如下图所示,ADC时钟抖动对信噪比影响,可以看到输入频率越大时钟抖动的影响越大,再相同输入频率下时钟抖动越小,信噪比越好。

本文探讨了ADC(模拟-to-数字转换器)的信噪比计算,包括理论信噪比6.02N+1.76dB的来源和处理增益的影响。处理增益通过数字滤波器提升信噪比,具体表现为10log(Fs/2BW)。以12位和16位ADC为例,展示了不同带宽下信噪比的差异。时钟抖动对信噪比也有显著影响,特别是在高输入频率下。最后,通过具体ADC芯片的应用实例,说明了如何通过改变带宽和采样率提升信噪比。

本文探讨了ADC(模拟-to-数字转换器)的信噪比计算,包括理论信噪比6.02N+1.76dB的来源和处理增益的影响。处理增益通过数字滤波器提升信噪比,具体表现为10log(Fs/2BW)。以12位和16位ADC为例,展示了不同带宽下信噪比的差异。时钟抖动对信噪比也有显著影响,特别是在高输入频率下。最后,通过具体ADC芯片的应用实例,说明了如何通过改变带宽和采样率提升信噪比。

6211

6211

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?