前言

在电子行业发展过程往往会受很多硬件限制,由于基带处理速率的限制在高速数据应用中往往会采用多相技术降低接口速率,比如实现模数转换的ADC器件,随着采样率提高数据速率增加,传统串行的传输方式必然导致接口速率随着采样率增加大幅度提升,本文简单记录下对多相数据概念的理解。

多相数据抽取

此时为了降低接口速率,通过在时钟的不同相位(相数x)提取采样数据,并将x相数据对齐后并行输出,从而实现将接口速率降低至fs/x运行。

如在AD9208工作在双通道模式,3000M采样率,下抽6倍,每个通道输出250M 2相复数,通过下抽和多相技术将数据速率降低到250M,即3000/6=250*2。

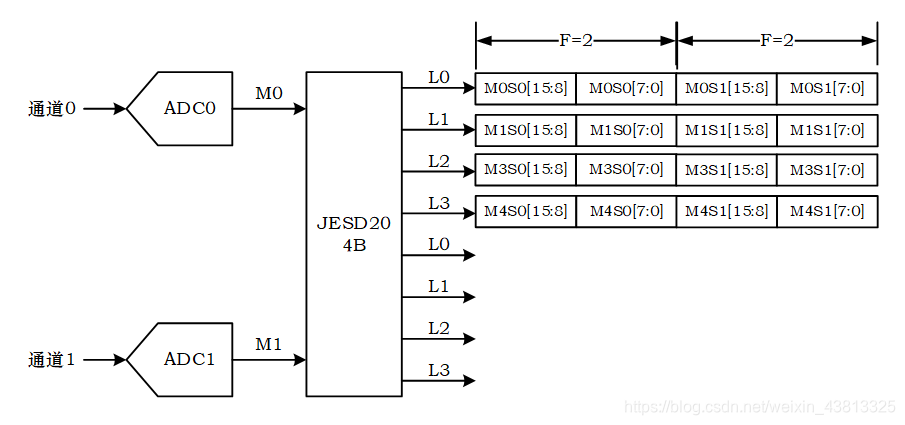

再比如ADS54J60工作在9

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

787

787

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?