前言

之前在使用JESD204B IP CORE时,将对应example design 复制到自己的工程时,example design中定义的XDC和我自己工程的XDC定义重复,GTH不知道该使用那些引脚导致gth复位的引脚错乱(表现在gth复位的引脚会有一个0.8V左右的直流偏置,有直流偏置的引脚和XDC定义引脚对应不上,导致jesd204链路一直无法link上),最后注释掉example design中定义的XDC就好啦~。过程中排查问题时使用IBERT做回环测试FPGA的高速收发器是否能正常工作,记录ibert的使用方法入下。

调用IP CORE

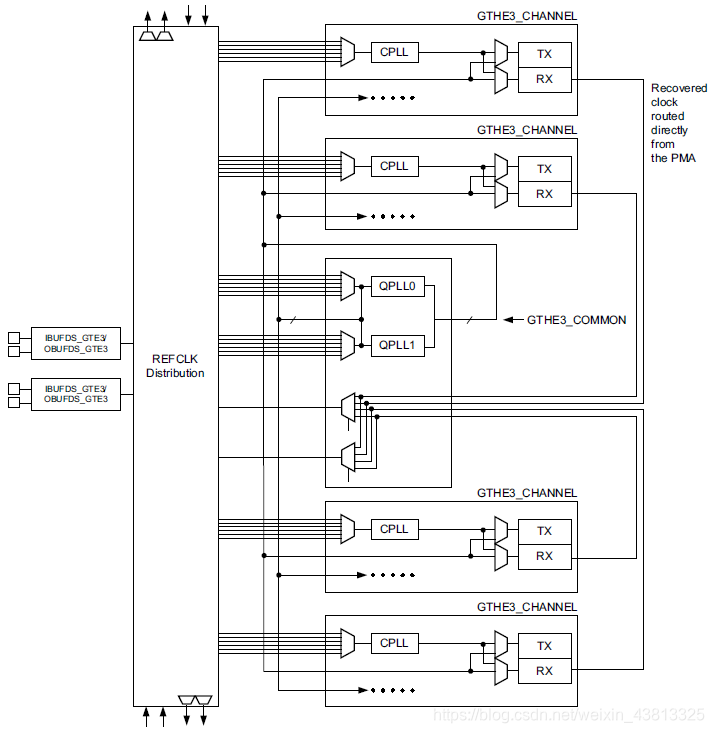

如下GTH的基本功能框图,每个GTH BANK包含两个参考时钟输入,4路收发通道,每个通道数据时钟可以通过CPLL和QPLL倍频得到,每个GTH BANK包括两个QUAD PLL(QPLL0和QPLL1),每个通道包含一个CHANNEL PLL。

IBERT是赛灵思提供的集成误码率测试仪,用于检测和评估高速收发器,每个ibert ip最多支持三种协议(协议即不同lane rate /data width/refclk/quad count的组合);每个协议中需要确定lane rate 即gth lane的速率,refclk即gth bank的参考时钟,quad count即用到的quad(一般一个quad即一个gth bank 包含四对收发通道)数量,PLL即输入

本文介绍了在使用Xilinx FPGA时,如何通过IBERT IP CORE进行高速收发器的测试。内容涉及GTH的基本功能、IBERT的配置选项,如参考时钟、均衡模式、链路耦合等,并详细阐述了回环测试的四种模式,以及如何通过硬件管理器观察误码率和眼图。

本文介绍了在使用Xilinx FPGA时,如何通过IBERT IP CORE进行高速收发器的测试。内容涉及GTH的基本功能、IBERT的配置选项,如参考时钟、均衡模式、链路耦合等,并详细阐述了回环测试的四种模式,以及如何通过硬件管理器观察误码率和眼图。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

475

475

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?