代码仅供参考:

链接:pan.baidu.com/s/1VekND1K50yclOKdkSI-otw

up1k

数字电路——多路复用器及控制信号产生逻辑的实现

一、实验目的

- 熟悉多路复用器以及模型机的工作原理。

- 学会使用 VHDL语言设计多路复用器。

- 掌握 generic的使用,能运用设计参数化多路复用器。

- 学会使用VHDL语言设计模型机控制信号产生逻辑。

二、实验内容

- 用 VHDL 语言设计模型机的 8 重 3-1 多路复用器;

- 设计参数化多路复用器,调用该参数化多路复用器定制为 8-1 多路复用器。

- 用 VHDL 语言设计模型机的控制信号产生逻辑。

三、实验方法

1、 实验方法

采用基于FPGA进行数字逻辑电路设计的方法。

采用的软件工具是Quartus II。

2、 实验步骤

(三个工程过程相同,以8重3-1多路复用器为例)

1、 新建三个工程,编写源代码。

(1).选择保存项和芯片类型:【File】-【new project wizard】-【next】(设置文件路径+设置project name为MUX)-【next】(设置文件名MUX.vhd—在【add】)-【properties】(type=AHDL)-【next】(family=FLEX10K;name=EPF10K10TI144-4)-【next】-【finish】

(2).新建:【file】-【new】(第二个AHDL File)-【OK】

2、 写好源代码,保存文件(MUX.vhd)。

3、 编译与调试。确定源代码文件为当前工程文件,点击【processing】-【start compilation】进行文件编译,编译成功。

4、 波形仿真及验证。新建一个vector waveform file。按照程序所述插入a,b,c三个节点(a、b为输入节点,c为输出节点)。(操作为:右击 -【insert】-【insert node or bus】-【node finder】(pins=all;【list】)-【>>】-【ok】-【ok】)。任意设置a,b的输入波形…点击保存按钮保存。(操作为:点击name(如:I0(0)))-右击-【value】-【clock】(如设置period=200;offset=0),同理设置name I1(0)(如120,,60),保存)。然后【start simulation】,出name S的输出图。

5、 时序仿真或功能仿真。

6、 查看RTL Viewer:【Tools】-【netlist viewer】-【RTL viewer】。

四、实验过程

A. 8 重 3-1 多路复用器

1、 编译过程

a. 源代码如图(VHDL设计)

b. 编译、调试过程

无错误信息,编译通过。

c. RTL视图

d. 结果分析及结论

实现8重3-1多路复用器就是在三个8维向量中选择一个输出,需要两个选择信号,用VHDL实现较为简单。

2、 波形仿真

a. 波形仿真过程(详见实验步骤)

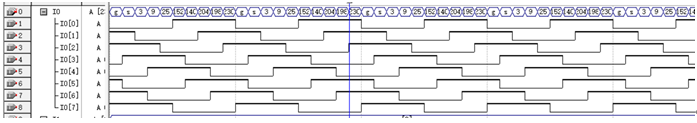

b. 波形仿真波形图

当选择输入s为00时选择I0的八维输入,正确

选择输入S为01时,输出I1,正确

当选择输入S为10时,输出I2,正确

c. 结果分析及结论

当选择输入s为00时选择I0的八维输入,正确

当选择输入S为01时,输出I1,正确

当选择输入S为10时,输出I2,正确

3、 时序仿真

a. 时序仿真过程

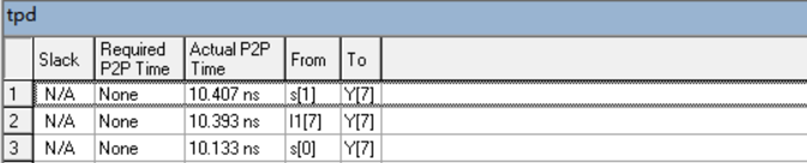

做好上述步骤后,编译【classic timing analysis】-在compilation report中选择【timing analysis】-【tpd】(引脚到引脚的延时)

b. 时序仿真图

c. 结果分析及结论

由S(1)引脚到Y(7)引脚所需时间最长为10.407ns,因此总体时间为10.407ns。

tpd (引脚到引脚的延时)

B. 参数化多路复用器,调用该参数化多路复用器定制为 8-1 多路复用器

1、 编译过程

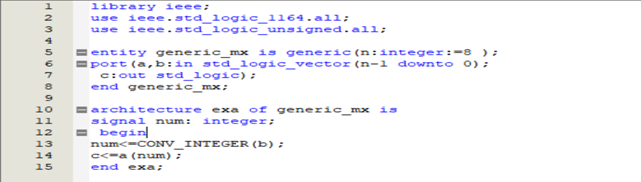

a. 源代码如图(VHDL设计)

参数化多路复用器:

定制为 4 位加法器:

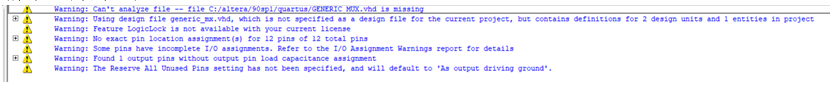

b. 编译、调试过程

无编译警告及错误。

c. RTL视图

d. 结果分析及结论

参数化多路复用器的设计较为困难,将输入信号个数n作为参数,选择信号在参数多路复用器中同样设计为长度为n的二进制数,在定制的时候注意选择参数的位数即可。

2、 波形仿真

a. 波形仿真过程(详见实验步骤)

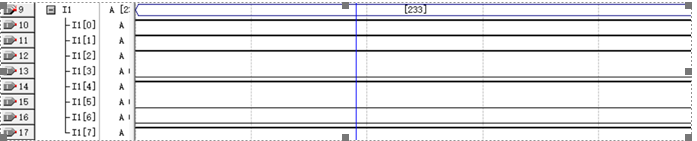

b. 波形仿真波形图

c. 结果分析及结论

0-2.5ns:s=”000”,F输出I0,正确

2.5-5ns:s=”001”,F输出I1,正确

5-7.5ns:s=”010”,F输出I2,正确

7.5-10ns:s=”011”,F输出I3,正确

10-12.5ns:s=”100”,F输出I4,正确

12.5-15ns:s=”101”,F输出I5,正确

15-17.5ns:s=”110”,F输出I6,正确

17.5-20ns:s=”111”,F输出I7,正确

3、 时序仿真

a. 时序仿真过程

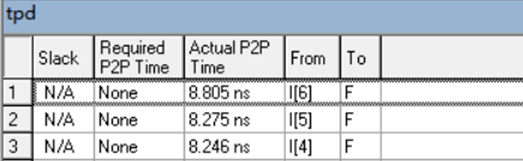

做好上述步骤后,编译【classic timing analysis】-在compilation report中选择【timing analysis】-【tpd】(引脚到引脚的延时)

b. 时序仿真图

c. 结果分析及结论

I(6)引脚到F引脚的延时最长,为8.805ns,因此总时长为8.805ns。

tpd (引脚到引脚的延时)

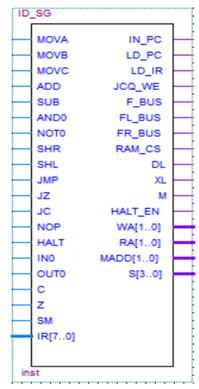

C. 模型机的控制信号产生逻辑

1、 编译过程

a. 源代码如图(VHDL设计)

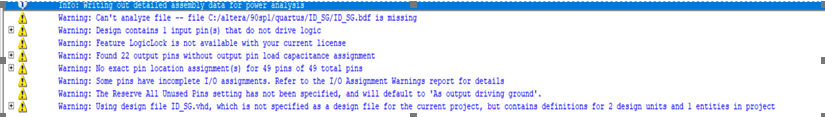

b. 编译、调试过程

c. RTL视图

逻辑符号:

d. 结果分析及结论

每一个控制信号都需要根据时钟周期与控制指令信号进行逻辑上的判断,需要掌握各个指令的执行过程,进而写出我们需要的控制信号的逻辑表达式。输入信号包括8位指令、状态位C,Z,SM,译码器输出的指令。通过这些输入产生执行指令阶段的控制信号,每条控制信号的产生逻辑见VHDL。下面的波形仿真只要检查控制信号的产生逻辑即可。

2、 波形仿真

a. 波形仿真过程(详见实验步骤)

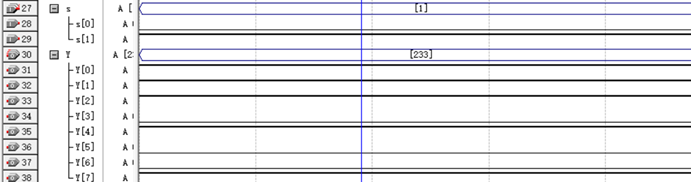

b. 波形仿真波形图

(仅ADD有变化时)

c. 结果分析及结论

当仅ADD为1,SM为0时是取操作,此时INPC为1,MADD为00,CS为0,XL为0,DL为1,LDIR为1,波形正确。

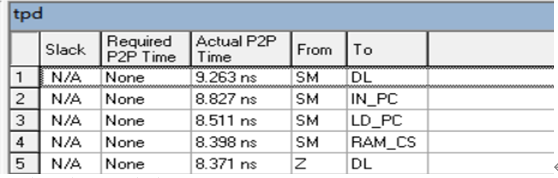

3、 时序仿真

a. 时序仿真过程

做好上述步骤后,编译【classic timing analysis】-在compilation report中选择【timing analysis】-【tpd】(引脚到引脚的延时)

b. 时序仿真图

c. 结果分析及结论

SM引脚到DL引脚的实际p2p时间最长且为9.263ns,故整体为9.263ns。

tpd (引脚到引脚的延时)

五、实验结论

前两个工程比较简单,只要正确理解工程要实现的功能就可以将代码简化到最佳,其中参数化多路复用器中使用了一个函数conv_integer将二进制数转化为了十进制数,进而能够直接输出选择信号(二进制)控制的输入信号中的哪一个(十进制)直接进行输出。这个方法有些不怎么好,虽然简便但是利用十进制数不能体现多路复用器的实现原理,而仅仅是实现了它的功能。

模拟机控制信号的逻辑产生较为复杂,需要将CPU的执行过程以及各个控制信号的功能完全理解清楚,在我写RAM的XL信号以及DL信号时理解错误,XL仅仅在MOVB为1时有效,各个信号在取周期与执行周期的逻辑取值可能不同,经过长时间的艰苦奋斗,我终于将控制信号逻辑判断了大概,但可能里面还存在一些逻辑上的错误判断不出来。

980

980

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?