提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

1. 前言

本实验教程主要指导大家如何将程序固化到QSPI FLASH中,并让ZYNQ芯片上电启动自动加载QSPI中的程序。

2. Vivado工程的编写

(1)本实验使用的Vivado工程延用《ZYNQ AXI GPIO中断实验——FPGA Vitis篇》中使用的Vivado工程,大家可以查看该文章来了解Vivado工程的建立以及下载该工程源码。

(2)由于要使用ZYNQ来加载QSPI FLASH的程序,需要修改下Vivado工程。通过配置ZYNQ7 IP核将QSPI FLASH接口给勾选上,如下图所示(具体管脚分配和电平标准需要根据实际电路进行配置,图中是以ZedBoard开发板为例进行配置的)。

(3)对工程进行保存,并最终通过“Generate Bitstream”生成Bit文件。在菜单栏“File -> Export -> ExportHardware…”导出硬件信息(.xsa文件),这里就包含了PS端的配置信息。该步骤如有疑问,可以参考以前的文章《ZYNQ串口打印输出——FPGA Vitis篇》。

3. SDK工程的编写

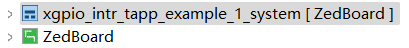

(1)由于本实验使用的工程延用《ZYNQ AXI GPIO中断实验——FPGA Vitis篇》中使用的工程,因此SDK中已经有“xgpio_intr_tapp_example_1_system”该APP工程。

(2)由于在我们修改了Vivado工程,.xsa文件也有变动,因此我们需要先更新下ZedBoard平台工程。右键“ZedBoard”平台工程,并点击“Update Hardware Specification”。

(3)选择刚更新的xsa文件,并点击“OK”按钮,对平台工程进行更新。

(4)新建一个名为“FSBL”的APP工程,该工程是一个二级引导程序,完成MIO的分配、时钟、PLL、DDR控制器初始化、SD、QSPI控制器的初始化,通过启动模式查找bitstream配置FPGA,然后搜索用户程序加载到DDR,最后交接给应用程序执行。详情可参考U281文档。

该APP工程的模板选择为“Zynq FSBL”

(5)在FSBL工程里,“fsbl_debug.h”头文件中,增加“FSBL_DEBUG_INFO”宏定义。可以让ZYNQ启动输出FSBL的一些状态信息,有利于调试,但会导致启动的时间变长。

(6)修改后保存,并进行编译,生成“fsbl.elf”文件。

(7)创建“Boot Image”:右键选择“xgpio_intr_tapp_example_1_system”APP工程,点击“Create Boot Image”。

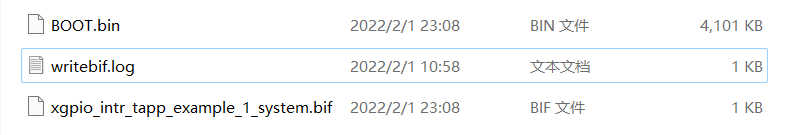

(8)弹出的窗口中可以看到生成的BIF文件路径,BIF文件是生成BOOT文件的配置文件,还有生成的BOOT.bin文件路径,BOOT.bin文件是我们需要的启动文件,可以放到SD卡启动,也可以烧写到QSPI Flash。

(9)在Boot image partition列表中有要合成的文件,第一个文件一定是 bootloader文件,就是上面FSBL APP生成的fsbl.elf文件;第二个文件是FPGA配置文件bitstream;第三个是应用程序,在本实验中为xgpio_intr_tapp_example_1_system.elf。点击Create Image生成。

(10)在生成的目录下可以找到BOOT.bin文件

4. QSPI FLASH烧写

(1)首先将ZedBoard的跳线帽“JP7”、“JP8”、“JP9”、“JP10”、“JP11”接到GND处,使得ZYNQ处于JTAG调试模式(可参考UG585)。

(2)在菜单栏选择“Xilinx”->“Program Flash”。“Image File”一栏选择刚生成的.bin文件,“Init File”一栏选择生成的FSLB ELF文件。点击“Program”按钮,将程序烧写到QSPI FLASH中。

(3)验证烧写的程序是否正确:关闭开发板的电源,将ZedBoard的跳线帽 “JP10”接到“3.3V”处(参考UG585),再打开开发板的电源。如果ZYNQ正常启动,则会上电自动启动GPIO中断点灯的工程。

A. 工程源码下载

如果大家对我们的文章感兴趣,可以关注我们的公众号:“FpgaHome”:

该工程对应的源码可以通过关注该微信公众号,在公众号输入 ZYNQ_QSPI 来获取工程的下载链接,工程采用的是Vivado2021.1版本。

参考文献:

[1] http://www.alinx.com.cn/.

[2]《ZYNQ 串口打印输出——FPGA Vitis篇》. 图灵研究院

[3]《ZYNQ AXI GPIO中断实验——FPGA Vitis篇》. 图灵研究院

[4]《Zynq-7000 SoC Technical Reference Manual》. UG585. Xilinx

1055

1055

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?