标题systemverilog中的package出现以及涉及的import和include的区别

概要

package(包)是sv相较于verilog新增的一个概念。至于为啥会新增一个这样的概念,主要是考虑到起一个易移植易修改的作用,为了使多个模块共享用户定义类型的定义。

因为多了package这样的一个概念,因此也多了一个import这样的一个概念,让人想到了`include的概念,下文详细描述。

Package举例及使用方式

package定义在package和endpackage之间。

package中可以进行变量声明、任务定义和函数定义甚至class,其中package中的变量和方法默认是static的。

package是一个独立的声明空间,不需要包含在Verilog模块中。

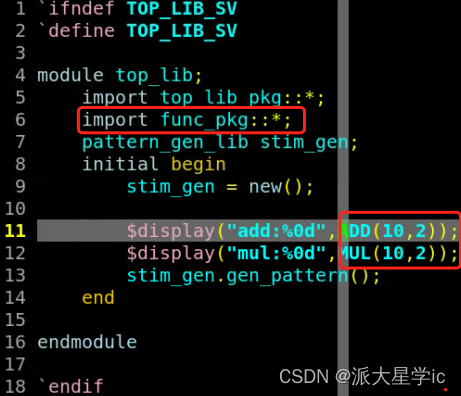

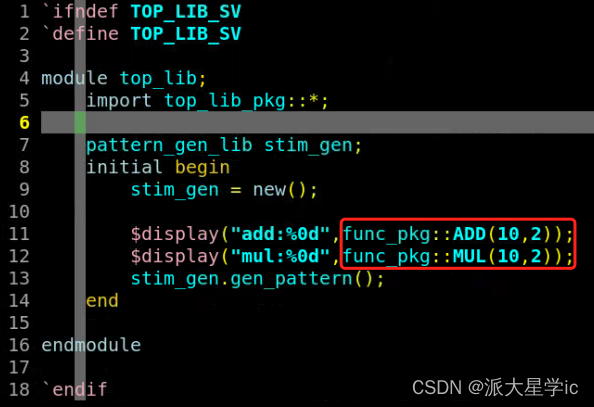

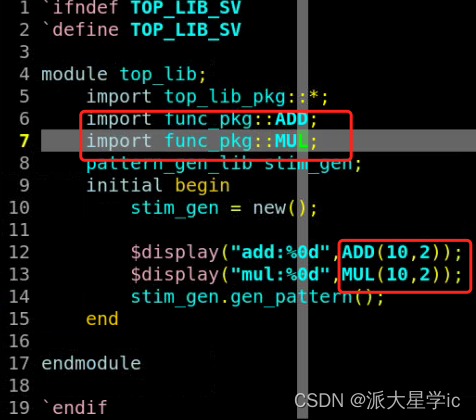

package的使用如下所示,func_pkg里存在两个自定义的函数ADD和MUL。

而package的使用方式有以下几种:

1、import:😗

2、通过pkg::func

3、导入package特定子项

多个module和class等可以通过以上三种方式完成对同一pkg中的内容的共享以及调用。

import及`include区别

`include相当于将文件的所有内容平铺到当前位置,而import则不是平铺,是将package中的内容的作用域引入当前位置。其具体的区别可见此:https://blog.csdn.net/Andy_ICer/article/details/115679314

小结

package的增加对于多个模块共享一个内容提供了方便,易于修改和移植。

3457

3457

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?