计算机组成与设计(RISC-V)——单周期实现数据通路和逻辑控制

1.前言

为了提升对计算机组成与设计(riscv)一书中处理器章节的理解,写下了这篇博客。

2.学习基础

要清楚riscv的指令集,明白指令是如何操作寄存器和内存的,更要清楚不同类型的指令的指令格式。下面列出这章内容所需的四种指令格式:

这四类指令分别为算数、载入、存储和条件分支。

3.带有控制单元的简单数据通路

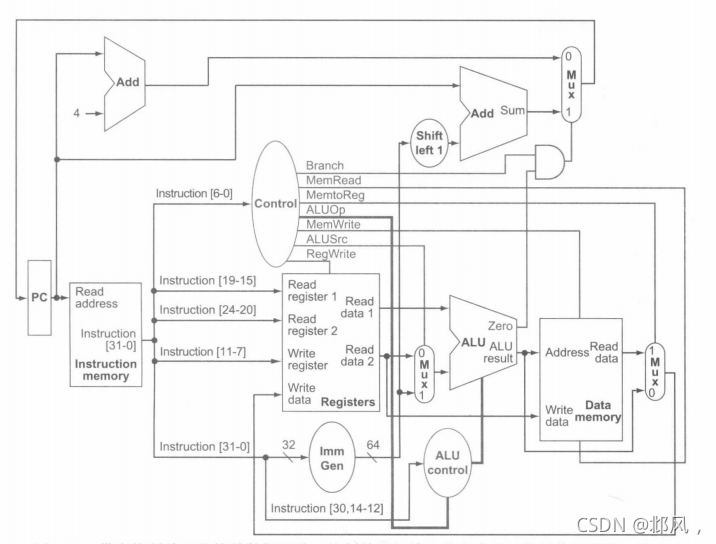

如下图所示:

我们可以看到,控制单元的输入是instruction[31-0]中的七位操作码字段,为[6-0]。输出有七个,分别是两个控制多路选择器的1位信号(ALUSrc和MemToReg)、三个控制寄存器堆和数据存储器读写的信号(RegWrite、MemRead和MemWrite)、一个确定是否分支的1位信号(Branch)和一个ALU的2位控制信号(ALUOp)。分支控制信号与ALU的零输入 信号一起送人一个与门。

以add x1,x2,x3为例讲解数据通路和控制单元如何执行。

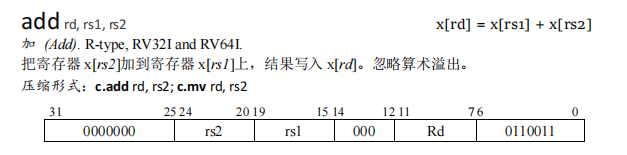

下面给出add操作指令的指令格式:

由此,我们可以知道其数据通路操作:

首先,由指令存储器取PC指令,并且PC经Add算数逻辑单元自增4(Branch为0,无条件执行PC+4)。

其次,将32位指令分位给到控制单元、寄存器堆以及算术逻辑控制单元。寄存器堆读出两个寄存器x2和x3,同时控制单元计算控制信号。

最后,ALUSrc控制多路选择器置0,将Read data1和Read data2给到ALU中。ALU control让ALU施行加法,结果由ALU result给到多路选择器,此时MemtoReg将其置0,于是结果写入到寄存器x1。

4.总结

虽然单周期设计结构并不复杂,可以完成指令操作,但是他的效率太低。在这种结构中,最长的路径决定了其时钟周期,这会使其始终周期太长,违背了加速经常性事件的设计原则。

不过,通过学习单周期实现数据通路和逻辑设计,可以很好的让我们理解指令是如何运作的,有助于我们未来的学习,为设计处理器打下基础。

3903

3903

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?