Wrapping core

本文主要讲述了The Maximized Reuse Core Wrapping Flow的基本原理,因为相较于The Simple Core Wrapping Flow来讲Reuse对timing和area的影响更小,也是更主流的一种设计流程。参考(翻译)自《Synopsys® TestMAX™ DFT User Guide》,FYI。

The Maximized Reuse Core Wrapping Flow

当function I/O register不是通过buffer或者invert直接连到I/O port时,the simple core wrapping flow会添加dedicated wrapper cell,所以为了减少对于core wrapper时序和面积的影响,TestMax DFT也会提供maximized reuse mode可以复用组合逻辑连接到I/O port 的I/O register。

Maximized Reuse Core Wrapper Cells

- Shared-Register Wrapper Cells

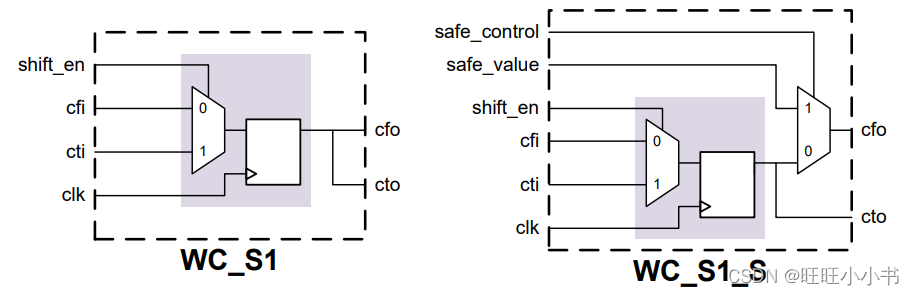

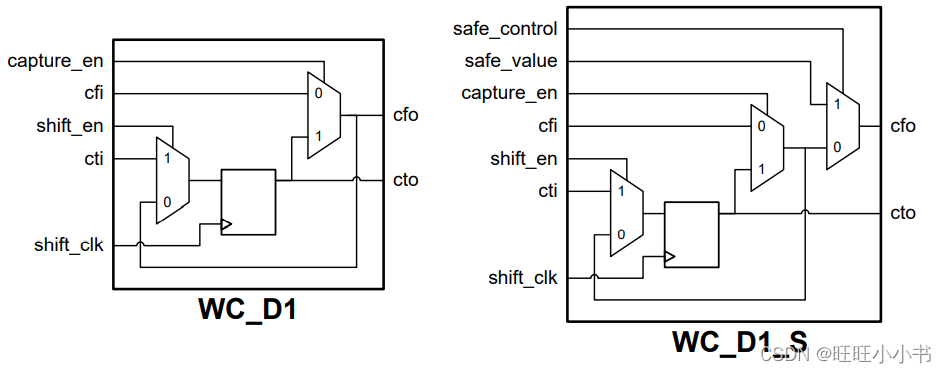

默认情况下maximized reuse flow对所有符合共享条件的port使用shared wrapper cells。下面是不包含safe value和包含safe value的shared wrapper cell。它们的逻辑结构不同于同名的simple core wrapper flow wrapper cell。

为了最小化面积开销,the maximized reuse flow使用没有状态保持功能的shared wrapper cell进行设计。the wrapper cell使用现有的wrapper register来实现,这就意味着他不是一个hierarchy结构,所产生的wrapper cell功能由一个典型的scan cell来实现。

The maximized reuse flow也允许function I/O register通过组合逻辑连接到I/O port进行共享。

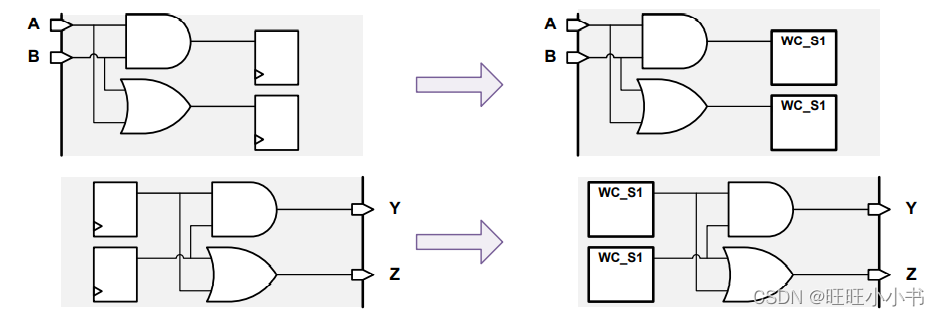

The maximized reuse flow提供了count-based和logic-depth-based来限制function register用来封装I/O port的数量。

使用现有的function register作为shared wrapper cell可以减少core wrapping的面积需求。shared wrapper cell和port之间的组合逻辑有效的被隔离在block外面是core wrapper logic关心的。这些逻辑必须使用EXTEST wrapper mode来测试,这个mode会执行周边逻辑。 - Dedicated Wrapper Cells

在maximized reuse flow中,dedicated wrapper cell被用来封装超过共享阈值的I/O ports。

这里用到的dedicated wrapper cell与simple core wrapper flow相同。

Maximized Reuse Core Wrapper Chains

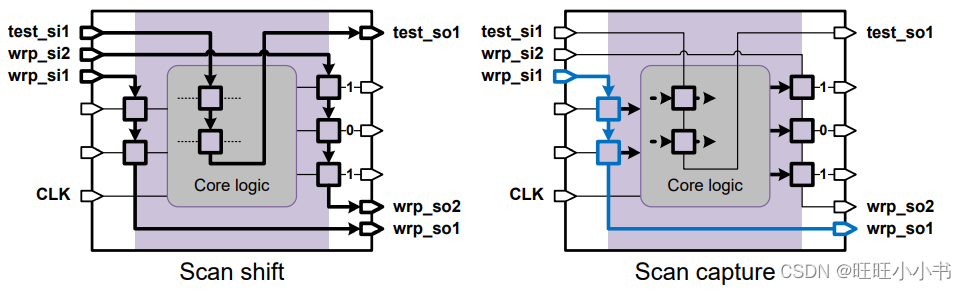

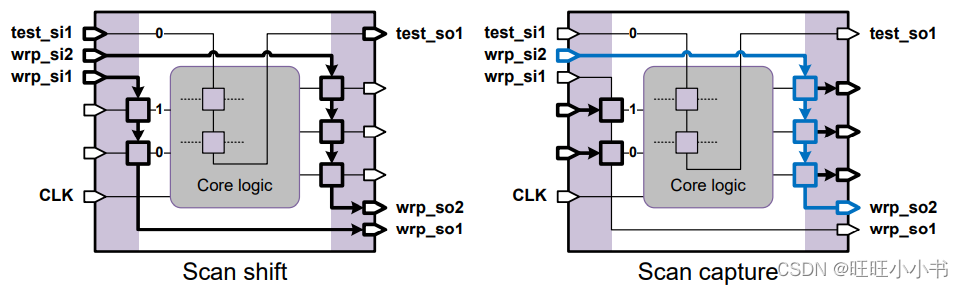

在maximized reuse core wrapping flow中,input 和 output wrapper cell被放置在有着单独的输入输出wrapper shift-enable信号的单独wrapper chain。因为shared wrapper cell在maximized reuse core wrapper flow中没有状态保持功能,所以wrapper chain保持scan shift mode以阻止wrapper cell capture值。

下图展示了在inward-facing操作下的shift和capture行为。在scan capture阶段,input wrapper chain保持scan shift(循环保持相同的值)来阻止外部输入。

下图展示了在outward-facing操作下的shift和capture行为。在scan capture阶段,output wrapper chain保持scan shift来阻止核心驱动的output值(不会干扰到下一个block),core wrapper chain使用逻辑0来驱动以减少功耗。

这些shift和capture操作适用于在input和output wrapper chain的所有wrapper cell,shared cell, dedicated cell,不使用任何dedicated wrapper cell来保持状态循环。

在transition-delay ATPG,保持shift状态的wrapper chain通过shift相反的值来产生transition。

Maximized Reuse Shift Signal

在maximized reuse flow中,scan-enable和wrapper shift signal受当前test mode限制:

- 在inward-facing wrapper mode下,input wrapper shift signal is always asserted。

- 在outward-facing wrapper mode下,output wrapper shift signal is always asserted。

- 在outward-facing wrapper mode下,internal core scan chain的scan-enable信号is always asserted(为了将value load到scanchain)

即使使用单个single wrapper shift signal,该信号在input 和 output wrapper chain也会被单独设置。

1490

1490

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?