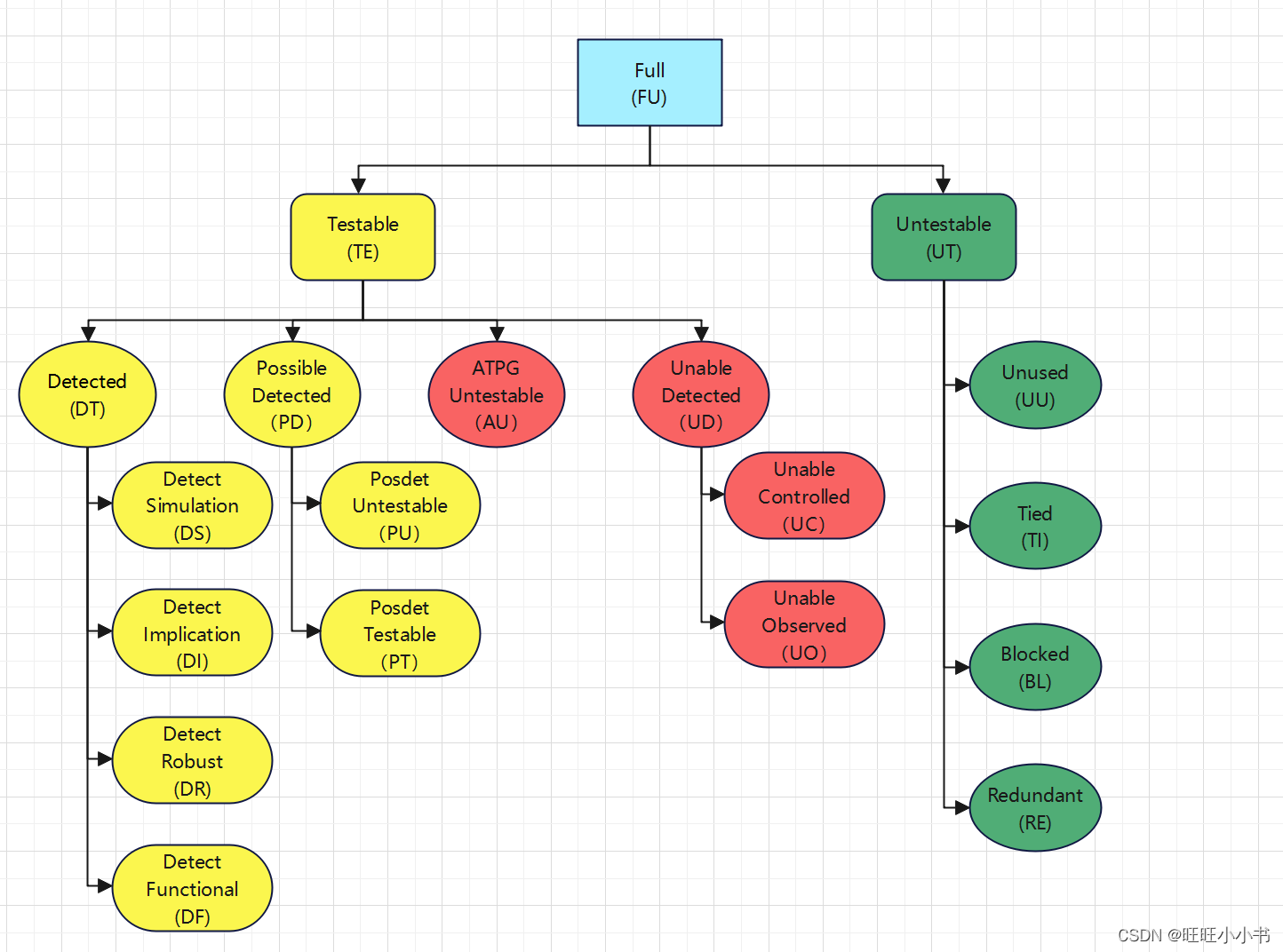

Fault Classes

除了上文提到的UT外,Fault还有另一大类也是我们更加关心的一类TE,即可以检测到的fault。工具在计算test coverage时并不会将UT计算进去,而是计算detect到的fault的数量以及可能detect到的fault占所有fault中除去不可测试的fault的比值,所以提高coverage主要从AU、UD入手。全部Fault的关系如下图所示:

TE(testable)

DT(detected)

所有ATPG可以检测到的fault都被归为DT,主要包括以下两类:

- DI(detect implication)

使用write_pattern产生的pattern就可以将这些点cover到,不需要专门针对这些点产生test pattern,工具在执行scan chain分析时就发现的fault,通常是扫描链中的fault。 - DS(detect simulation)

当工具进行fault simulation时检测到的fault归为DS,此时对产生的pattern去看fault simulation的结果,对比good circuit和actual circuit的simulation的结果,如果不同则说明这个fault可以被detect到。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1697

1697

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?