一、复数乘法

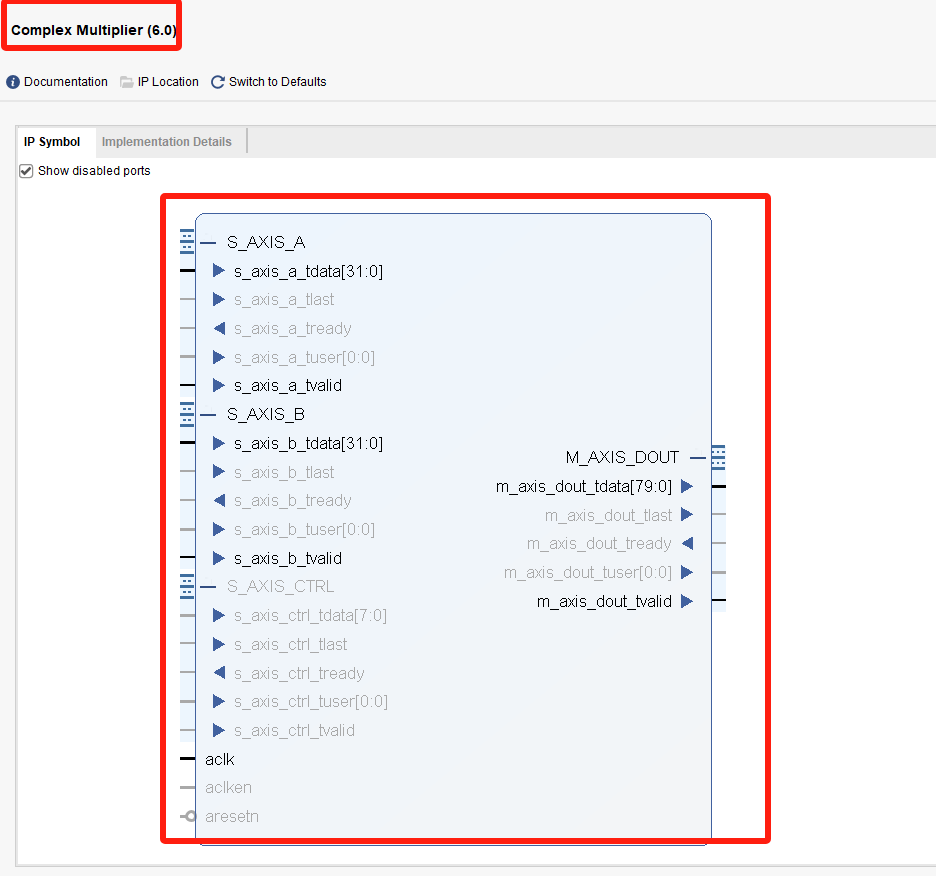

这是一个Xilinx(赛灵思)的复数乘法IP核的接口图,包含了几个主要的AXI-Stream接口。每个接口都有其特定的用途,下面将详细解释各个引脚的作用。

主要接口和引脚说明

S_AXIS_A(输入复数A)

- s_axis_a_tdata[31:0]: 输入数据通道A,通常用于传输复数A的实部和虚部。

- s_axis_a_tlast: 指示传输的最后一个数据(用于分组数据)。

- s_axis_a_tready: 表示从端准备好接收数据。

- s_axis_a_tuser[0:0]: 用户定义信号,用于传输与数据相关的控制信息。

- s_axis_a_tvalid: 表示数据A有效。

S_AXIS_B(输入复数B)

- s_axis_b_tdata[31:0]: 输入数据通道B,通常用于传输复数B的实部和虚部。

- s_axis_b_tlast: 指示传输的最后一个数据。

- s_axis_b_tready: 表示从端准备好接收数据。

- s_axis_b_tuser[0:0]: 用户定义信号。

- s_axis_b_tvalid: 表示数据B有效。

S_AXIS_CTRL(控制信号)

- s_axis_ctrl_tdata[7:0]: 控制数据,通常用于配置或控制IP核的操作模式。

- s_axis_ctrl_tlast: 指示控制数据的最后一个数据。

- s_axis_ctrl_tready: 表示从端准备好接收控制数据。

- s_axis_ctrl_tuser[0:0]: 用户定义的控制信号。

- s_axis_ctrl_tvalid: 表示控制数据有效。

M_AXIS_DOUT(输出复数结果)

- m_axis_dout_tdata[79:0]: 输出数据通道,通常用于传输复数乘法的结果,包括实部和虚部。

- m_axis_dout_tlast: 指示传输的最后一个数据。

- m_axis_dout_tready: 表示从端准备好接收输出数据。

- m_axis_dout_tuser[0:0]: 用户定义信号,用于传输与结果数据相关的控制信息。

- m_axis_dout_tvalid: 表示输出数据有效。

时钟和复位信号

- aclk: 时钟信号。

- aclken: 时钟使能信号,控制时钟是否启用。

- aresetn: 异步复位信号,低电平有效。

总结

- 数据通道(tdata): 传输数据的主要通道,包括输入复数A和B,以及输出复数结果。

- 控制信号(tuser, tvalid, tready, tlast): 控制和协调数据传输,确保数据的完整性和正确性。

- 时钟和复位(aclk, aclken, aresetn): 控制IP核的时钟和复位操作。

这些信号共同工作,确保复数乘法IP核能够正确接收输入数据、执行复数乘法计算,并输出结果。

二、fifo

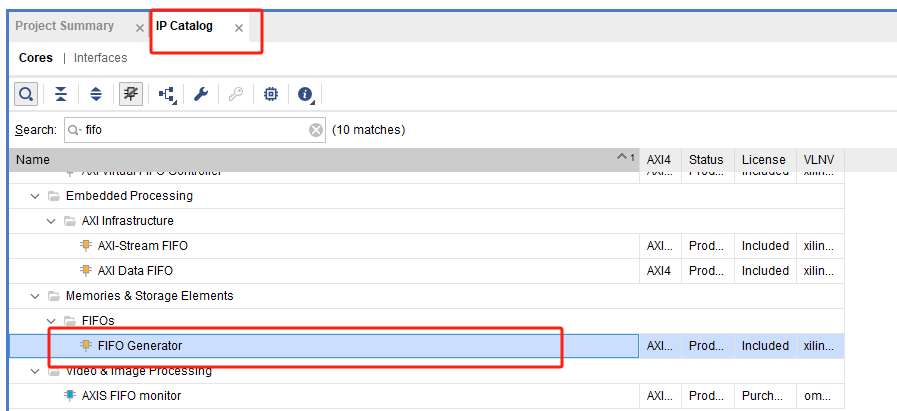

2.1 fifo的IP核创建

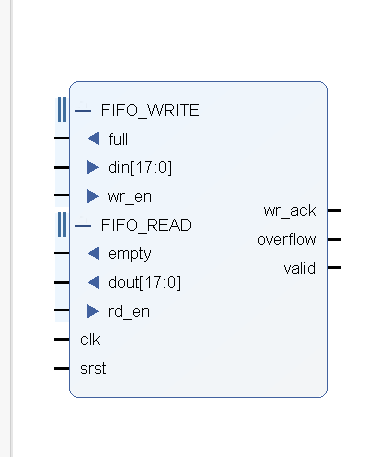

2.2 主要接口和引脚

可能用到的技术博客链接:FIFO IP的使用_fifo ip核使用-CSDN博客

valid和overflow信号需要单独点开

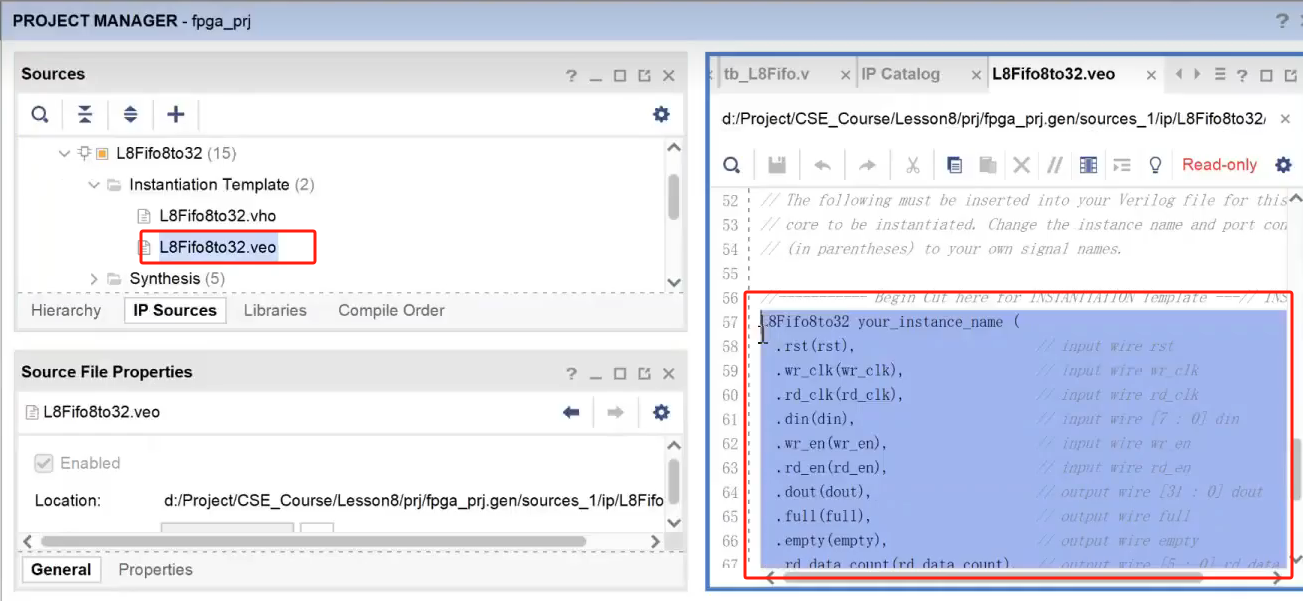

2.3 快捷实例化

找到.veo,然后复制右边的代码就很好实例化模块了

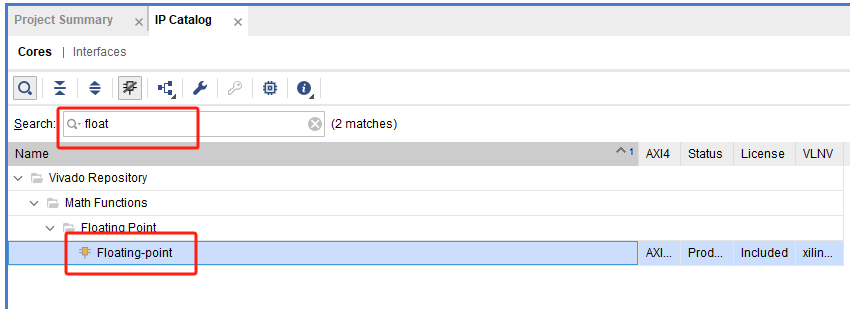

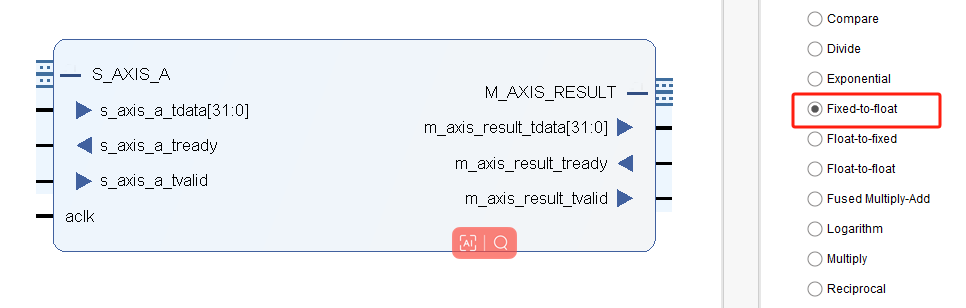

三、定点到浮点

3.1 IP核使用

3.2 主要接口和引脚

四、FFT

一般用浮点的话,前面可以配一个fifo,再配一个定点转浮点,然后浮点再过一个fifo,然后数据传输给FFT的IP核,那么配置的时候,就要在data format选择Floating Point(浮点)

五、移位寄存器shift_ram

模块解析

这段代码实例化了一个名为 shift_ram_fft_data 的模块,它的作用是延迟输入的数据,使得可以获取延迟后的数据。我们假设 shift_ram_fft_data 是一个移位寄存器模块。

移位寄存器的基本功能

一个移位寄存器可以通过时钟信号,将输入的数据按时钟周期依次移位,并在输出端提供延迟后的数据。这在数字信号处理中非常常见,用于对信号进行时间对齐或延迟处理。

代码详细解析

shift_ram_fft_data u_shift_ram_fft_data (

.A (delay_value ), // 输入延迟值,表示延迟的时钟周期数

.D (m_axis_fft_data_tdata ), // 输入数据,需要延迟的数据

.CLK (adc_clk ), // 时钟信号,控制移位操作

.Q (fft_data_delay_right ) // 输出延迟后的数据

);

verilog

复制代码

shift_ram_fft_data u_shift_ram_fft_data ( .A (delay_value ), // 输入延迟值,表示延迟的时钟周期数 .D (m_axis_fft_data_tdata ), // 输入数据,需要延迟的数据 .CLK (adc_clk ), // 时钟信号,控制移位操作 .Q (fft_data_delay_right ) // 输出延迟后的数据 );

引脚解析

-

A (delay_value):这是一个输入端口,用于指定移位寄存器的延迟周期数。它决定了数据在移位寄存器中停留的时间。比如,如果

delay_value为 5,那么输入数据将在 5 个时钟周期后出现在输出端口 Q 上。 -

D (m_axis_fft_data_tdata):这是移位寄存器的输入数据端口。需要延迟处理的数据通过这个端口输入。这里输入的是 FFT 数据

m_axis_fft_data_tdata。 -

CLK (adc_clk):时钟信号,用于同步移位操作。在每个时钟周期的上升沿,移位寄存器会将输入数据移位一位。

-

Q (fft_data_delay_right):这是移位寄存器的输出数据端口。延迟后的数据会通过这个端口输出。这里输出的是延迟后的 FFT 数据

fft_data_delay_right。

示例解析

假设:

- 输入信号

m_axis_fft_data_tdata是 64 位的数据,值为0x123456789ABCDEF0。 delay_value为 3,表示数据需要延迟 3 个时钟周期。- 时钟周期

adc_clk。

初始状态(假设所有移位寄存器中的数据为 0):

yaml

复制代码

寄存器初始状态: 周期 0: 0x0000000000000000 周期 1: 0x0000000000000000 周期 2: 0x0000000000000000 周期 3: 0x0000000000000000

第一个时钟周期:

- 输入数据

0x123456789ABCDEF0进入寄存器。

yaml

复制代码

寄存器状态: 周期 0: 0x123456789ABCDEF0 周期 1: 0x0000000000000000 周期 2: 0x0000000000000000 周期 3: 0x0000000000000000

第二个时钟周期:

0x123456789ABCDEF0移到下一位,新输入为0x0000000000000000(假设之后的数据为 0)。

yaml

复制代码

寄存器状态: 周期 0: 0x0000000000000000 周期 1: 0x123456789ABCDEF0 周期 2: 0x0000000000000000 周期 3: 0x0000000000000000

第三个时钟周期:

0x123456789ABCDEF0继续移到下一位。

yaml

复制代码

寄存器状态: 周期 0: 0x0000000000000000 周期 1: 0x0000000000000000 周期 2: 0x123456789ABCDEF0 周期 3: 0x0000000000000000

第四个时钟周期:

0x123456789ABCDEF0继续移到下一位,并在输出端口 Q 上出现。

yaml

复制代码

寄存器状态: 周期 0: 0x0000000000000000 周期 1: 0x0000000000000000 周期 2: 0x0000000000000000 周期 3: 0x123456789ABCDEF0

- 输出信号

fft_data_delay_right=0x123456789ABCDEF0。

通过这种方式,shift_ram_fft_data 模块实现了对输入数据的延迟处理,使得延迟后的数据可以用于后续的处理步骤。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?